# 金属-氧化物-半导体器件 $\gamma$ 辐照温度效应

王剑屏 徐娜军 张廷庆 汤华莲 刘家璐 刘传洋

(西安电子科技大学微电子研究所, 西安 710071)

姚育娟 彭宏论 何宝平 张正选

(西北核技术研究所, 西安 710024)

(1999 年 11 月 8 日收到)

研究了金属-氧化物-半导体(MOS)器件在  $\gamma$  射线辐照条件下的温度效应. 采用加固的 CC4007 进行辐照实验, 在不同温度、不同偏压, 以及不同退火条件下对 MOS 器件的辐照效应进行了比较, 发现温度对辐照效应的影响主要是决定界面态建立的快慢. 高温下辐照的器件, 界面态建立的时间缩短. 根据实验结果对器件阈值电压漂移的机理进行了探讨.

关键词: 金属-氧化物-半导体场效应, 辐射效应, 阈值电压漂移

PACC: 6180E, 7340Q, 7340T

## 1 引 言

随着数字集成电路日益广泛的应用, 金属-氧化物-半导体(MOS)器件和 MOS 集成电路在军事、航天、核技术等特殊环境下应用也越来越多. 在这些环境中, 如核爆场、地球同步轨道等, 集成电路不可避免地会受到环境的辐射. 大量的测试结果表明, 当 MOS 集成电路工作在有核辐射的环境时, 其电路性能会发生变化, 严重的辐照会导致集成电路失效<sup>[1]</sup>. 目前电子材料和器件的抗辐射加固技术, 仍然是电子学领域研究的热点. 对数字电路中广泛使用的 MOS 器件辐照效应的研究, 具有重要的理论意义和实际应用价值. 本文在针对 CC4007 芯片的辐照实验的基础上对 MOS 器件的辐照温度效应进行了研究, 并对其机理进行了探讨.

电子材料的辐照效应主要分位移效应和电离效应. 对于 MOS 器件而言, 影响器件性能的主要原因是电离效应. 在  $\gamma$  辐射环境中, MOS 器件受到带电粒子的辐照后, 会在栅氧化层  $\text{SiO}_2$  内激发产生电子-空穴对, 电子运动速度快, 很快被扫出栅氧化区, 空穴则在栅氧化层内被陷阱俘获产生大量的辐照感生氧化物陷阱电荷. 同时大量实验证明, 辐照在  $\text{Si}/\text{SiO}_2$  界面处还将产生大量的界面态陷阱电荷. 这些电荷造成了 MOS 器件电参数的变化, 如阈值电

压的漂移, 反向电流的增大, 迁移率和跨导的降低等, 从而引起集成电路产品性能的下降.

已有很多研究表明<sup>[2-4]</sup>, MOS 器件的辐照效应受到辐照总剂量、辐照剂量率、器件偏置条件、辐照温度、器件氧化层工艺等多种条件的影响, 其中辐照总剂量效应对器件的影响最为显著. 在同样的总剂量下, 不同剂量率的辐射效应也不相同, 高剂量率辐照比低剂量率辐照在 MOS 器件栅氧化层中产生更多的氧化物陷阱电荷和较少的界面态, 因此利用高剂量率辐照模拟空间低剂量率效应的工作, 目前还是很多研究者的重点. 但对于宇宙空间及同步轨道的飞行器上使用的 MOS 器件而言, 使用过程中不仅要受到低剂量率的宇宙射线辐射, 同时还受到轨道空间交变温度的影响. 因而研究 MOS 器件辐照性能时, 考虑温度对器件辐照性能参数的影响同样具有实际意义. 以往地面模拟的器件辐照效应实验大多在室温下进行, 这使模拟实验结果与实际情况有一定偏差.

本文在 100°C, 27°C 和 -28°C 下对 MOS 器件进行了辐照实验, 对不同温度下器件参数变化情况进行了对照, 实验表明辐照温度对 MOS 器件工作参数漂移产生很大影响. 同时利用改变氧化层内电场方向条件, 从  $\text{Si}/\text{SiO}_2$  界面系统内部对器件辐照效应机理进行了探讨, 进一步验证了氢离子运动模型能够很好地解释辐照感生界面态的形成过程.

## 2 MOS 器件辐照实验

实验采用西安微电子研究所研制的 CC4007 器件进行辐照。该器件由两对 pMOS, nMOS 和一个 CMOS 倒相器构成，并且在制造工艺中采用了辐照加固处理。MOS 管氧化层厚度为 70 nm，沟道长度为 3  $\mu\text{m}$ ，沟道的宽长比分别为：p1 管 50.67, n1 管 25.3, p2 管 101.33, n2 管 50.67, p3 管 202.67, n3 管 101.33。

器件辐照实验在西北核技术研究所  $\text{Co}^{60}$  辐照源进行，实验中使用的  $\gamma$  射线的剂量率为 0.311 Gy (Si  $\gamma$ s)，辐照剂量率采用热释光法标定。由于使用的是经过加固处理的器件，辐照最大总剂量为  $1.2 \times 10^3$  Gy (Si)。辐照过程中相同的器件分别处于三种不同的温度：100°C, 27°C 和 -28°C。在辐照过程中，CC4007 器件的两对 n 管、p 管的漏极相连，接成倒相器形式。p 管源极接 +5 V, n 管源极接地。栅极采用两种不同的偏压：0 V 和 +5 V，使 p 管 n 管分别处于最坏偏置条件下。辐照后在 100°C 的退火温度下进行了 168 h 的退火，退火过程中对两组器件的栅极加不同的电压，使其氧化物中电场方向相反。

实验所用测量仪器为惠普公司的 HEWLETT PACKARD 4156A 精密半导体参数分析仪，测试电路中采用了惠普公司的 HEWLETT PACKARD 3488A 开关控制仪。

众所周知，电离辐照引起的阈值电压漂移是由氧化层中的氧化物陷阱电荷和  $\text{Si}/\text{SiO}_2$  界面态陷阱电荷两部分引起的。为了分离这两部分电荷对 MOS 器件阈值电压漂移的贡献，本实验中先测量 MOS 器件亚阈特性曲线，然后利用半带电压法<sup>[5]</sup>将阈值电压漂移分离成两部分。

## 3 实验结果及讨论

### 3.1 辐照温度对器件阈值电压漂移的影响

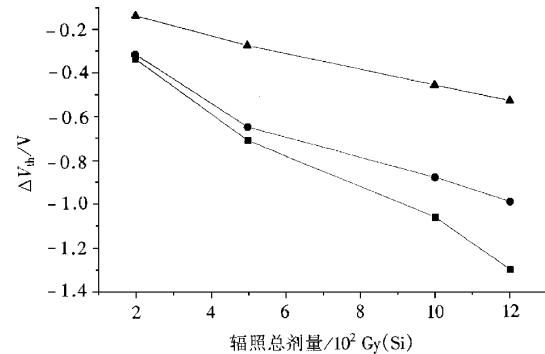

图 1 为不同辐照温度下 nMOS 管阈值电压漂移随辐照总剂量的变化情况。从图 1 可以看出，随辐照温度的降低，阈值电压的漂移逐渐增大。当总剂量达到  $1.2 \times 10^3$  Gy (Si) 时，在 100°C 辐照下的 nMOS 管阈值电压漂移量  $\Delta V_{th}$  的绝对值比在 27°C 辐照下的 nMOS 管小了 0.5 V，比在 -28°C 辐照下的

nMOS 管小了两倍多。

图 1 不同辐照温度下 nMOS 管阈值电压漂移 ▲ 为 100°C, ● 为 27°C, ■ 为 -28°C

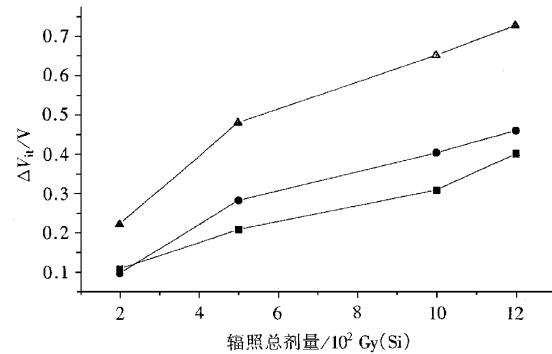

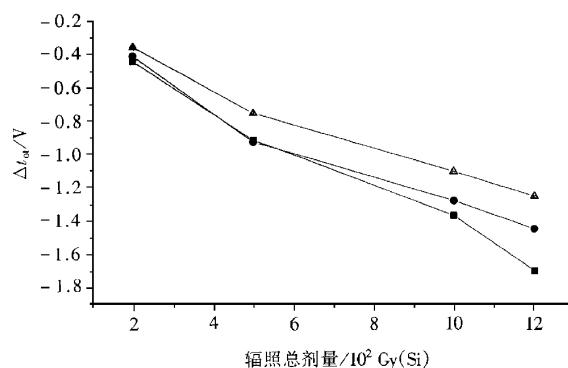

图 2 和图 3 分别为利用半带电压法分离后得到的 nMOS 管界面态陷阱电荷和氧化物陷阱电荷引起的阈值电压漂移  $\Delta V_{it}$ ,  $\Delta V_{ot}$  与辐照总剂量的关系曲线。从图 2 可以看到，辐照温度越高，界面态陷阱电荷引起的阈值电压漂移越大。对于辐照温度为 100°C 的 nMOS 管，在辐照结束时界面态陷阱电荷的建立比在 -28°C 和 27°C 辐照下的管子多了约一倍。对于同一剂量，虽然  $\Delta V_{it}$  和  $\Delta V_{ot}$  在不同温度下的数值不同，但是可以看到  $\Delta V_{ot}$  的变化比  $\Delta V_{it}$  的变化小。可以认为，在辐照过程中器件阈值电压漂移随温度的变化而变化的主要原因是由于  $\text{Si}/\text{SiO}_2$  界面态陷阱电荷的变化而引起的。

图 2 不同辐照温度下界面态引起阈值电压漂移 图注同图 1

pMOS 管和 nMOS 管相同，界面态陷阱电荷密度和氧化物陷阱电荷密度在数量上的变化趋势一致，所不同的只是 pMOS 管界面态陷阱电荷引起的阈值电压漂移量为负值。

氧化物陷阱电荷密度随辐照温度的升高逐渐降低，主要原因可以认为随温度升高，被陷于二氧化硅中空穴陷阱的载流子从晶格振动中获得了更多的能

图 3 氧化物陷阱电荷引起的阈值电压漂移 图注同图 1

量,更容易被陷阱所发射.而界面态随温度的变化可以用界面态建立的氢离子两步模型<sup>[6,7]</sup>解释.首先,电离辐照产生电子-空穴对,空穴被氧化物陷阱所俘获,这个过程伴随能量释放.放出的能量使氧化层中的 Si-H 弱键断裂(由于工艺的原因,氧化层中存在大量氢),形成 H<sup>+</sup> 和三价硅原子.这时 H<sup>+</sup> 和三价硅原子并没有完全脱离,它们之间还存在弱反应.下一步 H<sup>+</sup> 才脱离三价硅原子,扩散到界面处形成界面态(由于氢在 SiO<sub>2</sub> 中扩散系数远低于空穴,因此界面态的建立是缓慢的).到达界面处附近,这个 H<sup>+</sup> 与界面处的一个 Si-H 键以及一个从衬底隧道至界面的电子共同作用,产生界面态.具体反应方程如下:

随辐照温度的升高,氧化层晶格传递给载流子的能量也增大,这些能量可以使更多的 H<sup>+</sup> 脱离 Si,从而增加了运动到界面附近的 H<sup>+</sup> 数量,最终使界面态密度增加.近年来也有人<sup>[8]</sup>认为氧化层中被陷阱俘获的正电荷很大一部分就是 H<sup>+</sup> 和其他一些正离子,同样可以认为随温度的升高,这些正电荷被更多地发射出陷阱,从而增加了运动到界面处的 H<sup>+</sup> 的数量,最终导致界面态密度增加.

### 3.2 辐照后退火过程对界面态陷阱电荷的影响

在辐照结束后,对所有器件都进行了 100℃ 的高温退火,但在退火过程中采用了 +5 V 和 0 V 两种栅极偏压,目的是为了使栅氧化层中的电场方向不同.

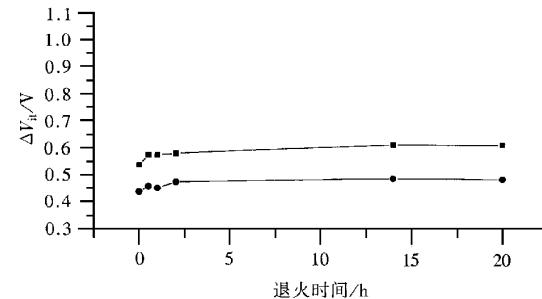

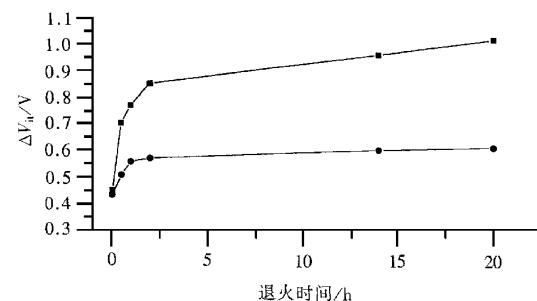

图 4 为两个经过 100℃ 辐照的 nMOS 管在不同栅偏压下由界面态引起的阈值电压漂移与退火时间的关系.从图 4 可以看出,除退火初期界面态有少量

建立外,在退火的大部分时间里界面态基本保持不变,呈现出界面态密度已经饱和.同时,栅偏压为 +5 V 的器件在退火期间界面态密度的增加量并不比栅偏压为 0 V 的器件多,唯一不同的是栅偏压为 +5 V 的器件界面态密度在一开始就大于 0 V 的器件,这是由于辐照时 +5 V 栅压器件界面态密度本身就大于 0 V 下辐照的器件的缘故.

图 4 100℃ 辐照器件界面态在退火过程中的变化 ■ 为 V<sub>g</sub> = +5V, ● 为 V<sub>g</sub> = 0V

图 5 为两个 -28℃ 条件下辐照的 nMOS 器件在退火过程中界面态密度变化的情况.可以看到对于低温辐照的器件在退火期间无论栅压如何,界面态密度都有较大幅度的增加.尤其对 +5 V 栅偏压的器件,经过 20 h 的退火,ΔV<sub>it</sub> 从 0.45 V 增加到 1.0 V 左右.对于栅极偏压为 0 V 的 nMOS 管,ΔV<sub>it</sub> 也从 0.4 V 增加到 0.6 V.

图 5 -28℃ 辐照器件界面态在退火过程中的变化 图注同图 4

对比图 4 与图 5,可以认为退火过程中不同辐照温度的器件界面态建立的不同是由于在高温下辐照的器件界面态的建立速度更快(见图 2),因而在辐照过程结束时,界面态的建立已经基本达到了饱和.而在低温下辐照的器件,在辐照结束时界面态的建立还未达到饱和,因而在退火过程中界面态还在继续建立.这符合界面态建立的 H<sup>+</sup> 两步模型的解

释. 在高温辐照下,  $H^+$  绝大部分被释放并输运到界面, 在辐照期间界面态基本上已经建立并达到饱和, 因此在下一步的高温退火中界面态的数量基本上不变化. 这也补充解释了辐照温度实验的结果.

在低温辐照器件的退火过程中, 注意到偏压为  $+5$  V 的 nMOS 管的氧化物陷阱电荷的数量在退火过程中逐渐减少,  $\Delta V_{ot}$  产生正向漂移, 同时  $\Delta V_{it}$  不断增大, 并且  $\Delta V_{ot}$  减少的量与  $\Delta V_{it}$  增加的量几乎相同. 显示出在退火过程中界面态陷阱电荷的退火与界面态的建立存在一一对应的关系. 文献[9]也报道过在对 pMOS 管的辐照退火实验中发现了这种关系, 说明氧化物陷阱电荷的退火与界面态建立在机理上存在内在的联系.

## 4 结 论

在  $Co^{60}$  源上, 在不同温度下对 MOS 器件进行了  $\gamma$  射线辐照实验, 并对辐照实验结果进行了分析. 可以得到以下结论:

1. 温度对辐照效应的影响主要是决定界面态建立的时间. 随温度的增加, 界面态建立的时间缩短.

2. 在退火过程中, 栅偏压对界面态的建立产生影响. 对于 nMOS 管, 栅极正偏压使界面态建立的

数量增加.

3. 辐照温度效应从另一个侧面对辐照感生界面态建立的氢运动两步模型提供了证据.

4. 利用改变温度条件对器件进行辐照, 可以加速或减缓界面态建立的速度, 这为替代现在广泛使用的耗时较长的辐照反弹测试提供了一条新的途径.

- [1] T. P. Ma *et al.*, Ionizing Radiation Effects in MOS Devices and Circuits (A Wiley-Interscience Publication John Wiley & Sons, 1989).

- [2] J. R. Schwank, F. W. Sexton, D. M. Fleetwood, *IEEE Trans. on Nucl. Sci.*, **35** (1998), 1432.

- [3] M. R. Shaneyfelt, J. R. Schwank, D. M. Fleetwood *et al.*, *IEEE Trans. on Nucl. Sci.*, **45** (1998), 1372.

- [4] A. V. Sogoyan, S. V. Cherepko, V. V. Emelianov, *IEEE Trans. on Nucl. Sci.*, **40** (1998), 69.

- [5] P. J. Mc Whorter, P. S. Winokur, *Appl. Phys. Lett.*, **48** (1986), 133.

- [6] N. S. Sak, D. B. Brown, *IEEE Trans. on Nucl. Sci.*, **36** (1989), 1848.

- [7] R. E. Stahlbush, A. H. Edwards, D. L. Griscom *et al.*, *J. Appl. Phys.*, **73** (1993), 658.

- [8] D. M. Fleetwood, W. L. Warren, *IEEE Trans. on Nucl. Sci.*, **42** (1995), 1698.

- [9] J. R. Schwank, F. W. Sexton, D. M. Fleetwood, *IEEE Trans. on Nucl. Sci.*, **35** (1988), 1432.

## TEMPERATURE EFFECTS OF $\gamma$ -IRRADIATED METAL-OXIDE-SEMICONDUCTOR FIELD-EFFECT-TRANSISTOR

WANG JIAN-PING XU NA-JUN ZHANG TING-QING TANG HUA-LIAN LIU JIA-LU LIU CHUAN-YANG

(Microelectronics Research Institute, Xidian University, Xi'an 710071, China)

YAO YU-JUAN PENG HONG-LUN HE BAO-PING ZHANG ZHENG-XUAN

(Northwest Nuclear Technology Institute, Xi'an 710024, China)

(Received 8 November 1999)

### ABSTRACT

Effects of irradiation temperature are explored for metal-oxide-semiconductor device under  $\gamma$ -rays. Hardened CC4007 chips were irradiated under different temperatures gate bias and annealing conditions. Threshold voltage shift was divided into  $V_{ot}$  and  $V_{it}$  using mid-gap voltage method. Finally, the mechanism of threshold shift was discussed.

**Keywords:** MOS-field effect transistor, radiation effects, threshold voltage shift

**PACC:** 6180E, 7340Q, 7340T