# 0.18μm CMOS 工艺栅极氧化膜可靠性的 衬底和工艺依存性

## 赵 毅1 为 万星拱2)

1 ( 东京大学材料系, 东京 113-8656, 日本) 2 ( 上海集成电路研发中心, 上海 201203) ( 2005年10月27日收到, 2005年11月7日收到修改稿)

用斜坡电压法(Voltage Ramp, V-ramp)评价了  $0.18\mu m$  双栅极 CMOS 工艺栅极氧化膜击穿电量(Charge to Breakdown,  $Q_{bd}$ )和击穿电压(Voltage to Breakdown,  $V_{bd}$ ). 研究结果表明,低压器件(1.8V)的栅极氧化膜(薄氧)p型衬底 MOS 电容和 N型衬底电容的击穿电量值相差较小,而高压器件(3.3V)栅极氧化膜(厚氧)p衬底 MOS 电容和 n衬底 MOS 电容的击穿电量值相差较大,击穿电压测试值也发现与击穿电量相似的现象,其原因可以归结为由于光刻工艺对多晶硅/厚氧界面的损伤。该损伤使多晶硅/厚氧界面产生大量的界面态,从而造成了薄氧与厚氧 n 衬底和 p 衬底 MOS 电容击穿电量差的不同。从 Weibull 分布来看,击穿电压 Weibull 分布斜率比击穿电量,击穿电压的分布非常均匀,而且所有样品的失效模式都为本征失效,没有看到"尾巴",说明工艺非常稳定。

关键词:薄氧,可靠性,击穿电压,击穿电量

PACC: 7340Q, 7360H

## 1.引 言

CMOS 集成电路和器件的可靠性是整个集成电路工艺和制造中非常重要的一部分 $^{[1-3]}$ . 近几年来,为了加快工艺的研发速度,很多公司都采用硅片级可靠性(Wafer Level Reliability,WLR)测试来评价工艺的可靠性 $^{4]}$ . 硅片级可靠性要测试的项目主要有以下几大类:栅极氧化膜的可靠性,互连线可靠性(电迁移 $^{556}$ ],热载流子效应,等离子损伤(天线效应 $^{57}$ )等. 其中,栅极氧化膜是 MOS 器件中最重要的一部分,因而备受重视 $^{[8-10]}$ . 击穿电量(Charge to Breakdown, $^{0}$ )和击穿电压(Voltage to Breakdown, $^{0}$ )是评价栅氧化膜可靠性的两个重要的参数,评价击穿电量和击穿电压和的方法主要有:斜坡电压法,斜坡电流法。

本文中,我们用斜坡电压法评价了 0.18 µm 双栅极 CMOS 工艺栅极氧化膜的可靠性.评价指标是击穿电量和击穿电压.分别研究了薄氧和厚氧的可靠性行为的不同,分析了原因.同时,还考察了器件

衬底对栅极氧化膜可靠性的影响.

## 2. 实 验

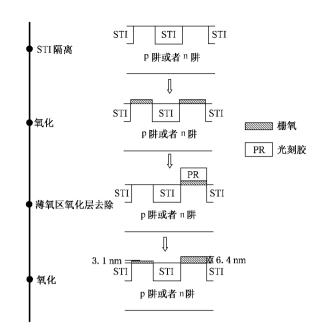

由于需要制备两种不同工作电压的器件(1.8V和3.3V),它们具有不同厚度的栅氧化膜.所以,采用两步氧化工艺.图1是两种不同厚度氧化膜的具体生长工艺流程.采用 STI 隔离,双阱工艺(Twin Wells, P-Well和 N-Well),标准0.18µm CMOS 工艺.

在本文所用到的 MOS 电容尺寸都为 : $1000 \mu m \times 1000 \mu m$ . 每组样品数为 52 个.

本文的实验采用斜坡电压法,利用 HP4071 自动半导体参数测试仪.

栅氧化膜的厚度用椭偏仪测得,薄氧和厚氧的厚度分别为 3.1nm 和 6.4nm. 文中所提到的厚度均为光学厚度.

## 3. 实验结果及其讨论

评价氧化质量的方法主要有斜坡电压法,斜坡

图 1 两种厚度栅氧化层生长过程示意图

电流法 恒定电压法和恒定电流法[2]. 用恒定电流法和恒定电压法 ,要担心电压或者电流值太高时会影响测试结果 ,而太低则要花去大量的测试时间 ,这些都是不利于氧化膜可靠性评价的. 相对而言 ,斜坡电压法可以是一种非常简单有效的方法. 在本文中 ,我们用斜坡电压法分析研究了在  $0.18\mu$ m 工艺下生长的两种不同厚度( 3.1nm 和 6.4nm )氧化膜的击穿电量(  $Q_{\rm bd}$  )和击穿电压(  $V_{\rm bd}$  )特性.

#### 3.1. 斜坡电压法测试击穿电量( $Q_{\mathrm{hd}}$ )

由于在斜坡电压的条件下 栅极电流  $I_{g}$  不是常数 所以击穿电量( $O_{loo}$ )要用积分的方法得到 $^{[8]}$ .

$$Q_{\rm bd} = \int_0^{T_{\rm bd}} I_{\rm g} \mathrm{d}t$$

其中  $T_{M}$  为击穿时间.

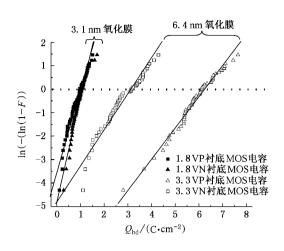

图 2 是厚氧化膜(6.4nm)和薄氧化膜(3.1nm)  $Q_{bd}$ 的 Weibull 分布图. 从图中可以看出,对于6.4nm厚氧化膜而言,p 衬底 MOS 电容  $Q_{bd}$ 值明显比 n 衬底 MOS 电容要小,但是它们的 Weibull 斜率几乎一样,只是整体有了一个平移. 对于此现象,可以给出如下解释:在用斜坡电压法测试时 对于 p 衬底 MOS 电容是在栅极( $V_g$ )上加负压,电子是从栅极上注入到氧化层中,所以栅极和氧化层之间的界面质量就会影响击穿电量的值. 而对于 n 衬底的 MOS 电容,由于也是在积累状态下测试,所以是在栅极上加正电压,所以此时电子是从衬底注入到氧化层中的,起

图 2 薄氧化层与厚氧化层的  $Q_{bd}$ 值 Weibull 分布图

决定作用的是硅衬底和氧化层之间的界面质量,而 通常硅衬底与氧化层的界面相对于栅极和氧化层的 界面来说是非常好的,所以得到的击穿电量值 n 衬 底 MOS 电容相对与 p 衬底 MOS 电容较大. 图 2 中 所示 对于 3.1nm 氧化膜而言 ,p 衬底 MOS 电容和 n 衬底 MOS 电容  $Q_{M}$ 值的 Weibull 分布图 从图中可以 看出 p 衬底 MOS 电容的  $Q_M$  值也比 n 衬底 MOS 电 容要小,但是相差不是特别大,两条线之间的距离明 显较小. 由此可见 ,厚氧和薄氧在 p 衬底 MOS 电容 和 n 衬底 MOS 在  $O_{M}$ 差值上呈现较大的差异,从图 1 栅氧生长工艺可以看出 对于 6.4nm 厚氧 ,它要经 过光刻胶的涂覆 剥离等 这些都会在很大程度上影 响氧化层表面的质量 从而会影响栅极与氧化层之 间的界面质量,会在界面处引入界面态,对 p 衬底 MOS 电容而言,测试时从栅极注入电子,所以注入 的电子会被栅极与氧化层界面中的界面态所捕获, 从而导致了测得的击穿电量较小:而对 n 衬底 MOS 电容 测试时是从衬底注入电子 而衬底和氧化层之 间的界面是较好的,所以得到的击穿电量值较大. 而对于 3.1nm 薄氧化层 就不存在光刻胶的剥离对 氧化层表面损伤的问题. 但是栅极与氧化层的界面 毕竟不如硅衬底与氧化层底界面质量好 ,所以 p 衬 底 MOS 电容的击穿电量值还是要比 n 衬底 MOS 电 容的要小一些, 但是差距没有厚氧大, 此外,从

#### 3.2. 斜坡电压法测试击穿电压( $V_{\rm hd}$ )

击穿电压是氧化膜非常重要的一个参数.

Weibull 分布图看,3.1nm 氧化层的斜率明显比

6.4nm 大. 这也从另外一个侧面表明厚氧的可靠性

其实不如薄氧 其他项目的可靠性测试也表明(如:

HCI 热载流子效应)厚氧的可靠性更令人担忧.

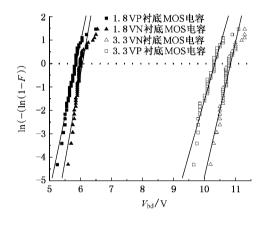

JEDEC 标准根据  $V_{bd}$  值的范围定义了以下三种失效模式  $^{(1)}$  (1)  $V_{bd} < V_{dd}$  , ( $V_{dd}$  :工作电压 )模式 A; 早期失效; (2)  $V_{dd} < V_{bd} < mV_{dd}$  (m > 1) 模式 B ,可靠性失效 (3)  $V_{bd} > mV_{dd}$  ,模式 C ,本征失效. 对于 m 的确定 ,各个公司与机构有自己的定义. 我们取 m = 2.3 ,这也是一个用得比较普遍的值. 图 3 是薄氧和厚氧所有样品击穿电压值的 Weibull 分布图 ,从图中可以看出 ,薄氧和厚氧所有样品的失效模式都为模式 C ,即本征失效. 这说明工艺控制得相当好. 从Weibull 分布看 ,拟合得非常好 ,不存在尾巴现象 ,这反应了我们工艺的稳定性. 但是仍然可以发现一点 不管对于薄氧还是厚氧 ,p 衬底 MOS 电容的击穿电压值比n衬底 MOS 电容的还是要小些.而且也

图 3 薄氧化层与厚氧化层的击穿电压( $V_{\mathrm{bd}}$ )值 Weibull 分布图

是厚氧的 p 衬底 MOS 电容和 n 衬底 MOS 电容差值 更大. 这也把这归因与界面效应. 对于 p 衬底 MOS 电容 测试时电子栅极注入 ,在栅极/栅氧处电子被界面态捕获后 ,降低了栅极的电位 ,从而降低击穿电压. 从 Weibull 斜率来看 ,厚氧和薄氧差不多.

虽然在 0.18 µm 及其以后的工艺 ,一般不用击穿电量作为指标来评价氧化膜质量 [12,13] . 而用击穿电压来作为评价项目 ,击穿电量值只是作为一个参考. 但是 ,从本文结果可以看出 ,击穿电量可以在一定程度上提供更多栅氧可靠性的信息 ,所以在测试时 ,仍然有必要给出击穿电量的数值.

## 4. 结 论

本文研究了 0.18 µm CMOS 工艺栅氧化膜可靠性的衬底和工艺依存性. 结果表明 ,厚氧(6.4 nm )p衬底和 n 衬底 MOS 电容的击穿电量和击穿电压值相差比较大 ,这主要归因于二次氧化工艺时光刻工艺导致了多晶硅与氧化层之间的界面质量劣化 ,在多晶硅/厚氧界面产生大量界面态. 薄氧(3.1 nm )p衬底和 n 衬底 MOS 电容的击穿电量和击穿电压值相差不大. 从击穿电压来看 ,氧化膜基都为本征失效 ,而且 Weibull 分布拟合得非常好 ,没有尾巴现象存在 ,说明工艺稳定性相当好.

<sup>[1]</sup> Wolf S 1997 Silicon Processing For the VLSI Era (New York: Academic) Vol.4

<sup>[2]</sup> Liu H X , Fang J P , Hao Y 2001 Acta Phys . Sin . **50** 1172 (in Chinese) [刘红侠、方建平、郝 跃 2001 物理学报 **50** 1172]

<sup>[ 3 ]</sup> Hu C 1985  $\it IEDM$  ,  $\it Tech$  .  $\it Dig$  ( <code>Washington</code> , DC <code>JEEE</code> ) p368

<sup>[4]</sup> Zhao Y, Xu X M 2004 Semiconductor Technology 29 5 (in Chinese) [赵 毅、徐向明 2004 半导体技术 29 5]

<sup>[5]</sup> Zhao Y, Cao G, Xu X M 2005 Chin. J. Semiconductors 26 1653 (in Chinese)[赵 毅、曹 刚、徐向明 2005 半导体学报 26 1653]

<sup>[6]</sup> Zhao Y , Wan X G , Xu X M , Cao G , Jian Yang 2005 J. Electrochem . Soc . 152 G831

<sup>[7]</sup> Zhao Y, Xu X M 2004 Semiconductor Technology 29 34 (in Chinese J 赵 毅、徐向明 2004 半导体技术 29 34]

<sup>[8]</sup> Cappelletti P , Ghezzi P , Pio F , Riva C 1991 International

Conference on Microelectronic Test Structures , Kyoto , Japan 4 81

<sup>[9]</sup> Zhao Y, Wan X G, Xu X M 2005 Chin. J. Semiconductors **26** 2271 (in Chinese)[赵 毅、万星拱、徐向明 2005 半导体学报 **26** 2271]

<sup>[10]</sup> Wang Y G, Xu M Z, Tan C H, Duan X R 2005 Acta Phys. Sin. 54 3884 in Chinese I 王彦刚、许铭真、谭长华、段小蓉 2005 物 理学报 54 3884]

<sup>[ 11 ]</sup> JEDEC/FSA Joint Publication 2002 Foundry process qualification guidelines ( Arlington : JEDEC ) 16

<sup>[ 12 ]</sup> Degraeve R , Groesenken G , Bellens R , Depas M , Maes H E 1995 IEDM Tech . Dig ( Washington : DC IEEE ) 863

<sup>[13]</sup> Zhao Y, Wan X M, Xu X M, Cao G, Bu J 2006 Chin. J. Semiconductors 27 290 (in Chinese) [赵 毅、万星拱、徐向明、曹 刚、卜 皎 2006 半导体学报 27 290]

## Substrate and process dependence of gate oxide reliability of 0.18µm dual gate CMOS process

Zhao Yi<sup>1</sup>)† Wan Xing-Gong<sup>2</sup>)

1 J. Department of Material Engineering , University of Tokyo ,7-3-1 Hongo , Bunkyo-ku , Tokyo 113-8656 , Japan )

2 J. Shanghai IC R&D Center , Shanghai 201203 , China )

( Received 27 October 2005 ; revised manuscript received 7 November 2005 )

#### Abstract

V-ramp method was used to evaluate gate oxide reliability of  $0.18\mu m$  dual gate CMOS process. Charge of breakdown ( $Q_{bd}$ ) and voltage of breakdown ( $V_{bd}$ ) of gate oxide with n-type substrate and p-type substrate were extracted. It was found that for low voltage (thin oxide) gate oxide device the  $Q_{bd}$  of gate oxide of n-type substrate and p-type substrate are almost the same, but for high voltage (thick oxide) gate oxide device the  $Q_{bd}$  of n-type substrate and p-type substrate have a big difference. At the same time,  $Q_{bd}$  of gate oxide with p-substrate is bigger than that of gate oxide with n-substrate. The difference of  $Q_{bd}$  of thin gate oxide and thick gate oxide can be attributed to lithographic damage to the interface of poly-silicon gate and thick gate oxide. There is a big difference between the Weibull slopes of charge of breakdown of thin oxide and thick oxide. For the voltage of breakdown, Similar difference between n-substrate and p-substrate gate oxide was also observed. However, there is no big difference between the Weibull slopes of voltage of breakdown of thin oxide and thick oxide.

Keywords: ultra thin gate oxide, reliability, charge of breakdown, voltage of breakdown

PACC: 7340Q, 7360H

<sup>†</sup> E-mail: zhao@adam.t.u-tokyo.ac.jp