# 超薄栅下 LDD nMOSFET 器件 GIDL 应力下退化特性\*

# 陈海峰 郝 跃 马晓华 唐 瑜 孟志琴 曹艳荣 周鹏举

(西安电子科技大学微电子学院,西安 710071) (2006年8月1日收到2006年8月14日收到修改稿)

对  $1.4\,\mathrm{nm}$  超薄栅 LDD  $\mathrm{nMOSFET}$  器件栅致漏极泄漏 GIDI( gate-induced drain leakage )应力下的阈值电压退化进行了研究 . GIDL 应力中热空穴注进 LDD 区界面处并产生界面态 这导致器件的阈值电压变大 . 相同栅漏电压  $V_\mathrm{DG}$ 下的不同 GIDL 应力后阈值电压退化量的对数与应力  $V_\mathrm{D}/V_\mathrm{DG}$ 的比值成正比 . 漏偏压  $V_\mathrm{D}$  不变的不同 GIDL 应力后阈值电压退化随着应力中栅电压的增大而增大 相同栅偏压  $V_\mathrm{G}$  下的不同 GIDL 应力后阈值电压退化也随着应力中漏电压的增大而增大 这两种应力情形下退化量在半对数坐标下与应力中变化的电压的倒数成线性关系 ,它们退化斜率的绝对值分别为 0.76 和 13.5 . 实验发现器件退化随着应力过程中的漏电压变化远大于随着应力过程中栅电压的变化 .

关键词:栅致漏极泄漏, CMOS, 阈值电压, 栅漏电压

PACC: 7340Q, 7340, 7360H

# 1. 引 言

为了提高电路的性能,实现电路的高速和低功耗工作,金属-氧化物-半导体(MOS)器件的特征尺寸迅速缩小,对应的栅氧化层厚度越来越薄<sup>1]</sup>.这样作用在氧化层上的电场就极大的增加,由此因薄栅而带来的器件的可靠性问题日益突出.对于 n-MOSFET,超薄栅下的应力引发的泄漏电流和超薄栅氧化层软击穿后的导电机理<sup>[2,3]</sup>,以及热载子退化方面,人们已经做了大量的研究.但是在这些研究中应力多为栅上恒压应力或开态应力.

随着器件越来越薄,器件关态时(nMOSFET 时棚电压  $V_c < 0$  V)由带带隧穿引发的 GIDL(gate-induced drain leakage)电流越来越大,它已经成为严重限制 MOSFET 以及 Flash 存储器的问题之一[4]. GIDL 电流本身便引入了热空穴注入,它使得空穴陷落在栅氧化层中从而会导致器件的不稳定性以及能导致氧化层击穿 $^5$   $^6$   $^1$  因此随着氧化层厚度的减小,关态氧化层的可靠性将会越来越重要 $^6$   $^1$  ,此方面已经引发了越来越多的关注 $^{14-9}$   $^1$  .

Igura 等<sup>7]</sup>得出 GIDL 应力过程中带带隧穿制造 出来的"冷"空穴在横向电场中获得能量变成"热"空 穴从而注入到氧化层中的注入物理机理 他们并发 现恒定  $V_{rc}$ 下的应力中空穴的注入速率不取决于栅 漏电压  $V_{\rm nc}$  ,而仅仅取决于应力中的漏电压  $V_{\rm D}$  .而 压  $V_{\rm DC}$ 的程度大于依赖漏电压  $V_{\rm D}$ . Wu 等人 $^{[6,8]}$ 研究 了恒定漏栅电压  $V_{DG}$ 下的不同 GIDL 应力以及  $V_{DG}$  恒 定的不同 GIDL 应力下超薄栅 MOS 器件的经时击穿 (TDDB)特性,除此之外,GIDL应力被作为热空穴注 入应力被广泛的应用<sup>[5,9]</sup>. 尽管有大量的针对 GIDL 应力研究展开,但这些研究仍然并未完全理解 GIDL 这一空穴注入应力所对器件造成的退化问题以及很 少提供详细的 GIDL 热载流子注入应力后器件的阈 值电压这一重要的电学参量的退化情况 ,而且在对 GIDL 应力中  $V_D$  与  $V_C$  对器件阈值电压退化的不同 的影响的讨论也较少,

本文基于此对  $1.4~\mathrm{nm}$  超薄栅 LDD  $\mathrm{nMOSFET}$  的 GIDL 应力下阈值电压退化进行了研究 ,对相同  $V_\mathrm{DC}$  下的 GIDL 应力以及相同

<sup>\*</sup>国家自然科学基金(批准号 160376024)资助的课题.

<sup>†</sup> E-mail: heellor@yahoo.com.cn

的  $V_{\rm D}$  下的 GIDL 应力问题进行了大量实验以及分析与讨论 给出了 LDD  $_{\rm M}$ OSFET 的阈值电压退化的物理机理以及详细的阈值电压退化情况. 这些研究将有助于更好地了解超薄栅器件在关态应力下的退化以及有助于在研究超薄栅器件的退化过程中选择更有效的空穴注入应力.

### 2. 器件和实验

实验中器件为标准 90 nmCMOS 工艺制造的 LDD nMOSFET. 器件栅长  $L=0.16~\mu\text{m}$  ,栅宽  $W=6~\mu\text{m}$  氧化层厚度分别为  $T_{\text{ox}}=1.4~\text{nm}$  和 4~nm. 栅极 采用  $n^+$ 型多晶硅. 阈值电压定义为漏电流为  $0.1\times W/L\times\mu$ A 时的栅电压. 实验中 1.4~nm 器件阈值电压为 0.32~V.

GIDL 电流测试以及 GIDL 应力过程中 ,源电压  $V_{\rm S}=0$  V 和衬底电压  $V_{\rm B}=0$  V . GIDL 电流用来分析

GIDL 应力中热载流子类型以及氧化层损伤情形. GIDL 应力为三种类型 :相同  $V_{DG}$  = 4.0 V 的 GIDL 应力 相同  $V_{D}$  = 2.4 V 的 GIDL 应力 :相同  $V_{G}$  = -1.6 V 的 GIDL 应力 . 每种类型中不同的应力时间均为 1000 s 应力中每隔 100 s 监测阈值电压 . 所有的应力和测试都在室温下的避光和静电保护环境下使用 HP4156B 精密半导体参数分析仪进行 .

# 3. 结果与讨论

#### 3.1. 超薄栅中 GIDL 应力方法

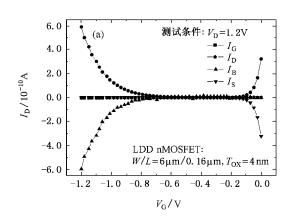

图 I(a)(b)分别为 4 nm 和 1.4 nm 器件的关态 电流特性 .4 nm 器件中 GIDL 电流(关态漏电流  $I_D$ ) 与衬底电流  $I_B$  相同. 栅电流  $I_C$  很小 其与衬底电流 相比可以忽略. 而在 1.4 nm 器件中,相同测试设置下 GIDL 电流明显增大,并且与衬底电流不再相等,栅电流开始变大,其与衬底电流相比不能被忽略.

图 1 关态下器件四种电流 (a)栅厚 4 nm 的情形 (b)栅厚 1.4 nm 的情形

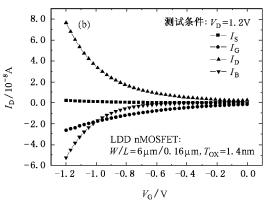

这是因为 GIDL 电流产生在栅压  $V_{\rm G}<0$  V ,漏压  $V_{\rm D}>0$  V 条件下,由于漏栅偏压  $V_{\rm DG}$ 较大,引起漏区 硅中能带向上弯曲.当价带顶超过导带底时,即弯曲 量  $\Psi_{\rm S}>1.2$  eV,电子就会从价带顶隧穿进导带从而被漏极收集,成为 GIDL 电流,如图  $\chi$  a )所示.

一维的 GIDL 电流公式为[10 11]

$$I_{\rm D} = A \times E_{\rm S} \times \exp(-B/E_{\rm S}),$$

(1)

$E_{\rm S} = (V_{\rm DG} - 1.2)/3T_{\rm OX},$  (2)

式中 A 为常数 B = 21.3 MV/cm  $E_s$  为漏栅交叠区界面处的电场 A.2 为垂直界面处隧穿能够发生的能带弯曲最小量 B 是 B SiO<sub>3</sub> 和 Si 的介电常数比值.

在 4 nm 栅中,由于氧化层较厚,从(1)(2)式得 出其 GIDL 电流要小于 1.4 nm 的器件的 GIDL 电流. 由于超薄栅中 GIDL 效应中大量的空穴隧穿进 LDD 区上的栅氧化层中,因此当漏栅电压  $V_{DG}$  很大时,这些空穴将具备足够高的能量,它们会在隧穿过程中在氧化层中造成损伤或者被俘获,这种损伤效果将比在厚栅器件下更加明显。

因为 GIDL 电流对交叠区的损伤非常敏感 ,它

图 2 (a)nMOSFET GIDL 电流产生时的能带弯曲 (b)厚栅下GIDL 电流产生时器件的剖面示意图 (c)超薄栅下的 GIDL 电流产生时器件的剖面示意图( ●表示电子 ;○表示空穴 )

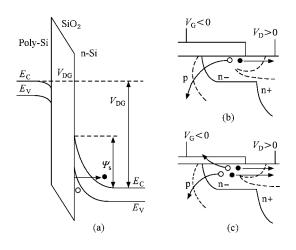

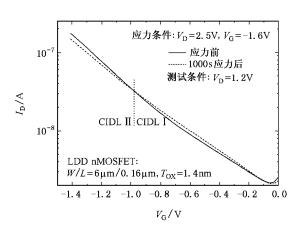

被用来分析 GIDL 应力产生的损伤. 图 3 为 1.4 nm 器件在 GIDL 应力前后 GIDL 电流的变化情况, 从图 中看出 GIDL 应力 1000 s 后 GIDL 电流曲线发生了 变化.GIDL I区应力后电流变大,GIDL II区则变 小.这是因为界面态在高  $V_{\rm nc}$ 下变成中性 ,只有陷阱 电荷通过改变带带隧穿电流而影响 GIDL 电流大 小 $^{[12]}$ .在低  $V_{\rm nc}$ 下界面陷阱通过陷阱辅助带带隧穿 来影响 GIDL 电流<sup>[13]</sup>.在图 3 中 ,GIDI( [ )低电场区 中,GIDL 电流变大,这说明在 GIDL 应力中产生了界 面态,其辅助了带带隧穿,从而使的 GIDL 电流变 大.而在 GIDI( [[ )高电场区中 ,GIDL 电流变小 ,这 是由于陷落的空穴引起的,陷落在界面处的空穴,使 的交叠区中附近硅中的能带弯曲量减小,从而使得 电子的隧穿长度变大 结果导致隧穿电流变小.从以 上分析得知 ,GIDL 应力下 ,热空穴注入进界面以及 产生了大量界面态.

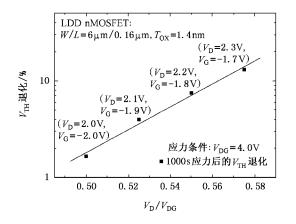

#### 3.2. 相同 $V_{DG}$ 下的 GIDL 应力

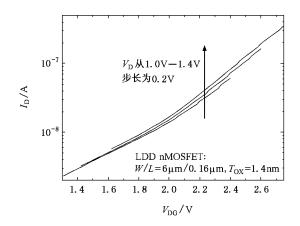

图 4 为器件关态  $I_{\rm D}$ - $V_{\rm DC}$ 曲线 ,从图中看出相同  $V_{\rm DC}$ 下 GIDL 电流并不相等 ,其随着  $V_{\rm D}$  的增大而增大.这是因为  $V_{\rm DC}$ 恒定的情形下 ,在栅漏交叠区附近的纵向电场基本不变 [14]. 当漏电压变大时 ,横向电场将会增加 ,其导致界面处硅中横向的空穴隧穿加剧 因而 GIDL 增加 . 正是这些 GIDL 特性使得相同  $V_{\rm DC}$ 下的不同的 GIDL 应力对器件产生不同的退化 .

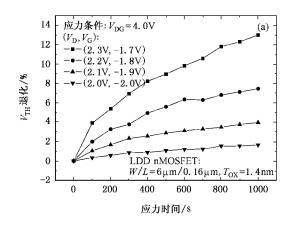

图 5 给出了  $V_{DG}$  = 4 V 的四种 GIDL 应力后器件 阈值电压退化与应力时间曲线. 图中看出应力之后,阈值电压变大 尽管有空穴陷落在氧化层中. 这是因

图 3 GIDL 应力前后关态  $I_D$ - $V_C$  曲线

图 4 相同  $V_{DG}$ 下 GIDL 电流比较

为这些空穴陷落在 LDD 区内 ,并未使得漏区向沟道扩展 ,即未使得有效沟道变短 . 因此这些热空穴并未屏蔽掉那些产生的界面态的影响 ,而那些在应力过程中产生的界面态则增加了 LDD 区电阻以及降低了载流子的迁移率 ,这导致相同偏置下线性区漏电流变小 ,从而使得达到 0.1 × W/L × μA 时的栅电压变大 ,即阈值电压变大 .

图 5 四种  $V_{DG}$  = 4.0 V 下的 GIDL 应力后器件阈值电压退化与应力时间曲线 (a)线性坐标下(b)双对数坐标下

图 6 相同  $V_{\rm DC}$ 下的四种  $_{

m GIDL}$  应力  $_{

m 1000~s}$  后器件阈值电压退化与  $V_{

m D}/V_{

m DC}$ 的关系

#### 3.3. 相同 $V_{\rm G}$ 下的 GIDL 应力

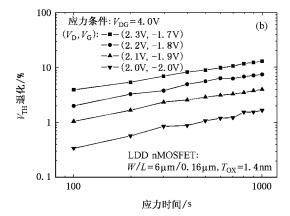

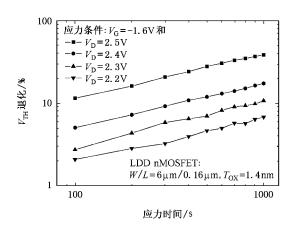

图 7 给出了应力过程中  $V_{\rm G} = -1.6$  V 时四种 GIDL 应力下的阈值电压与应力时间变化曲线. 每种 应力下器件的退化在双对数坐标下呈现线性关系. 随着应力过程中漏偏压  $V_{\rm D}$  的增大,  $V_{\rm TH}$  退化增大.

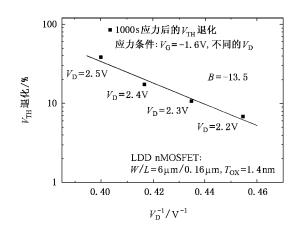

图 8 为从图 7 中提取的各种应力 1000 s 后器件的阈值电压退化量与  $1/V_D$  之间的关系 ,它们在半对数坐标下呈现线性关系 . 这与沟道热载流子退化模型  $\Delta = A \, \mathrm{e}^{B/V_D [\ 16\ ]}$  也相符 ,其中 B 反映的是不同应力下的退化速率 图 8 中斜率 B 值为 -13.5 .

图 7 栅电压不变的四种 GIDL 应力中器件阈值电压与应力时间 曲线

图 8 棚电压不变的四种 GIDL 应力 1000  ${

m s}$  后阈值电压退化与  ${

m 1/}$   $V_{

m D}$  的关系

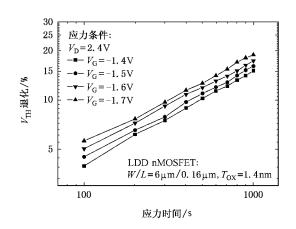

#### 3.4. 相同 $V_{\rm D}$ 下的 GIDL 应力

图 9 为应力过程中漏电压  $V_{\rm D}=2.4~{\rm V}$  时四种 GIDL 应力下器件的阈值电压随时间的变化曲线.图中看出随着应力中的栅电压绝对值的增大 ,阈值电压退化变大.但是栅电压每增加  $0.1~{\rm V}$   $V_{\rm DG}$ 增加  $0.1~{\rm V}$   $V_{\rm DG}$   $V_{\rm DG}$

图 9 漏电压不变的四咱 GIDL 应力中器件阈值电压与应力时间 曲线

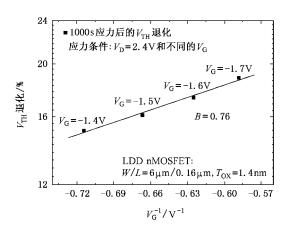

图 10 漏电压不变的四种 GIDL 应力 1000  $_{\mathrm{S}}$  后阈值电压退化与  $_{\mathrm{I}/V_{\mathrm{G}}}$  的关系

$V_{\rm C}$  变化退化的斜率 B 远远小于固定  $V_{\rm C}$  随漏电压  $V_{\rm D}$  退化的斜率(绝对值),即  $0.76 \ll 13.5$ ,因此在 GIDL 应力中增加或减小相同的漏栅电压  $V_{\rm DC}$ ,其应力所引发的退化速度取决于增加的是栅电压或漏电

压 尤其是在超薄栅下.其在应力中增加漏电压的阈值电压退化远大于在应力中增加同样大小的栅电压所引发的退化.

# 4. 结 论

本文讨论了超薄栅下 GIDL 应力问题. 由于在超薄栅下器件中在 GIDL 电流产生过程中大量的空穴直接隧穿进栅中形成栅电流,当这些空穴在强电场中获得足够大的能量,它们将会在隧穿过程中对LDD 区上面的氧化层造成损伤. 因此在超薄栅下利用 GIDL 效应作为应力来研究 LDD nMOS 器件的空穴损伤更加的有效 特别是 LDD 区栅漏交叠区附近的 SiO,/Si 界面.

在 GIDL 应力过程中, 空穴注进栅中, 一些被陷 阱俘获 成为陷落空穴 同时在界面处制造出大量界 面态,由于这些空穴位于 LDD 区内的界面处,因此 它们不能引起器件有效沟道的缩小,所以不能屏蔽 界面态所导致 LDD 区电阻的增加, 因此 GIDL 应力 后器件的阈值电压增大.相同漏栅电压  $V_{\infty}$ 下不同 GIDL 应力中,器件的阈值电压的退化量随着漏电压 的增大而增大,且这种退化的对数与  $V_{\rm D}/V_{\rm DC}$ 的比值 成正比.此外,相同漏电压  $V_{\mathrm{D}}$  下的不同 GIDL 应力 后器件的阈值电压退化量随着应力过程栅电压的增 大而增大 相同栅电压  $V_c$  下的不同 GIDL 应力后器 件的阈值电压退化量随着应力过程栅电压的增大而 增大,这两种应力情形下退化量的对数与应力中变 化的电压的倒数成线性关系,实验发现应力中增加 漏电压的阈值电压退化远大于在应力中增加同样大 小的栅电压所引发的退化.

<sup>[1]</sup> Liu H X , Zheng X F , Hao Y 2005 Acta Phys. Sin. 54 1373(in Chinese ) 刘红侠、郑雪峰、郝 跃 2005 物理学报 54 1373]

<sup>[2]</sup> Wang Y G, Xu M Z, Tan C H, Duan X R 2005 Acta Phys. Sin. 54 3884(in Chinese ] 王彦刚、许铭真、谭长华、段小蓉 2005 物 理学报 54 3884]

<sup>[ 3 ]</sup> Wang Y G , Xu M Z , Tan C H , Zhang J F , Duan X R 2005 *Chinese Physics* **14** 1886

<sup>[4]</sup> Chu Y L , Wu C Y 1989 IEEE Electron Devices Letters 21 123

<sup>[5]</sup> Ma Z , Lai P T , Cheng Y C 1993 IEEE trans . Electron devices 40 125

<sup>[6]</sup> Wu E , Nowak E , Lai W 20 EE 04 CH37533 42nd Annual International Reliability Physics symposium 84

<sup>[7]</sup> Igura Y , Matsuoka H , Takeda E 1989 IEEE Electron Devices Letters 10 227

<sup>[8]</sup> Wu E, Nowak E 2004 IEEE Electron Devices Letters 25 414

<sup>[9]</sup> Kim Y P, Kim S T, Moon J T, Kim S U 2001 IEEE Transaction on Device and Materials Reliability 1 104

<sup>[ 10 ]</sup> Chen J , Chen T Y , Chen I C , Ko P K , Hu C 1987 IEEE Electron

Device Lett . 8 515

<sup>[ 11 ]</sup> Wang T , Chang T E , Chiang L P , Wang C H , Zous N K , Huang C 1998 IEEE Trans . Electron Devices 45 1511

<sup>[ 12 ]</sup> Lo G Q , Kong D L 1990 IEDM Tech . Dig . 557

<sup>[ 13 ]</sup> Cheng K , Lyding J W 2003 IEEE Electron Devices Letters 24 487

- [ 14 ] You K F , Wu C Y 1999 IEEE Trans . Electron Devices 46 1174

- [ 15 ] Takeda E , Yang C Y , Hamada A M 1995 Hot-carrier effects in MOS devices ( San Diego : Academic ) p82.

[ 16 ] Min B W , Zia O , Celik M , Widenhofer R , Kang L , Song S , Gonzales S , Mendicino M 2001 *IEDM* 873

# Characteristics of degradation under GIDL stress in ultrathin gate oxide LDD nMOSFET 's \*

Chen Hai-Feng Hao Yue Ma Xiao-Hua Tang Yu Meng Zhi-Qin Cao Yan-Rong Zhou Peng-Ju (School of Microelectronics, Xidian University, Xi 'an 710071, China)

(Received 1 August 2006; revised manuscript received 14 August 2006)

#### Abstract

The threshold voltage ( $V_{\rm TH}$ ) degradation have been investigated under GIDL (gate induced drain leakage) stresse in LDD nMOSFET with 1.4 nm-thick gate oxide. The trapped holes and interface states generated in the stress process at interface around LDD overlapping region result in the increase in  $V_{\rm TH}$ . The logarithm of  $V_{\rm TH}$  degradation after GIDL stresses at constant  $V_{\rm DG}$  is proportional to the ratio of  $V_{\rm D}/V_{\rm DG}$ . The  $V_{\rm TH}$  degradation after GIDL stresses at constant  $V_{\rm D}$  increases with increasing  $V_{\rm G}$  in the stress , and that after GIDL stresses at constant  $V_{\rm G}$  increases with increasing  $V_{\rm D}$  in the stress In the last two cases the  $V_{\rm TH}$  degradation is always linear with the reciprocal of the bias which changes in the stress , and the absolute values of degradation slopes are 0.76 and 13.5 , respectively. Experimental result shows that the degradation depends more strongly on  $V_{\rm D}$  than on  $V_{\rm G}$ .

Keywords: gate-induced drain leakage, CMOS, threshold voltage, drain-to-gate voltage

PACC: 7340Q, 7340, 7360H

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (Grant No. 60376024).