# SiC 肖特基源漏 MOSFET 的阈值电压 \*

汤晓燕<sup>†</sup> 张义门 张玉明

(宽禁带半导体材料与器件教育部重点实验室 西安电子科技大学微电子学院 西安 710071)

(2008年5月5日收到 2008年7月14日收到修改稿)

SiC 肖特基源漏 MOSFET 的阈值电压不同于传统的 MOSFET 的阈值电压。在深入分析工作机制的基础上,利用二维模拟软件 ISE 提取并分析了器件的阈值电压。对 SiC 肖特基源漏 MOSFET 的阈值电压给出物理描述,得出当源极载流子主要以场发射方式进入沟道,同时沟道进入强反型状态,此时的栅电压是该器件的阈值电压。

关键词:碳化硅,肖特基接触,阈值电压

PACC:7280,7330,7340S,7220

## 1. 引言

碳化硅(SiC)肖特基源漏 MOSFET(Schottky Barrier Source/Drain Metal-Oxide Transistor, SBSD-MOSFET)用肖特基金属代替了高掺杂的pn结做 MOSFET 的源漏,其工艺比离子注入工艺简单得多,避免了长期困扰常规 SiC MOSFET 的离子注入工艺难度大、退火温度高、晶格损伤大<sup>[1]</sup>,注入激活率低<sup>[2]</sup>等问题,有利于改进器件的特性。目前尚没有 SiC SBSD-MOSFET 工艺实验的相关报道<sup>[3]</sup>。

对 Si 基 SBSD MOSFET 的研究开展的较早,近年来这种结构已经成为实现超深亚微米 MOSFET 的一种结构<sup>[4]</sup>。研究者已经认识到这种结构器件的阈值电压与传统 MOSFET 不同<sup>[5,6]</sup>,但还没能给出明晰的物理定义。本文研究了 SiC SBSD-MOSFET 的阈值电压,对 SiC SBSD-MOSFET 的阈值电压给出了物理描述。

## 2. 基本输运机理

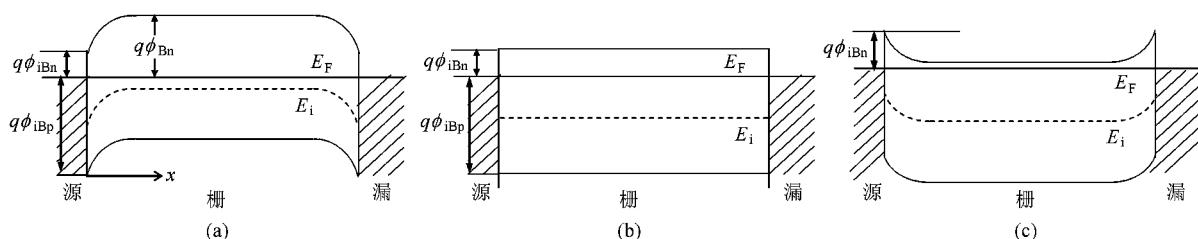

SBSD-MOSFET 器件能否正常工作的关键是源漏肖特基接触金属的选择。对 n 沟器件要求金属和反型后的 SiC 表面形成较低的电子势垒。图 1 是 n 沟 SBSD-MOSFET 器件表面随栅压变化的能带图。当栅压  $V_G$  为零时,源漏区对电子和空穴均有较高的势垒,阻碍载流子流动,器件处于关态,如图 1(a)。随着栅压增大,电子的有效势垒高度( $q\phi_{iBn}$ )降低。定义  $q\phi_{iBn} = W_m - \chi$  为电子的本征势垒高度( $W_m$  为金属的功函数,  $\chi$  为半导体的电子亲和能),空穴的势垒高度用  $q\phi_{iBp}$  表示。当电子的有效势垒高度等于其本征势垒高度时能带弯曲消失,如图 1(b)。该状态源漏金属的费米能级等于器件表面 SiC 的费米能级,是源漏金属和 SiC 表面形成电子的反阻挡层和阻挡层的分界限,称此时的栅压为势垒

图 1 SiC n 沟 SBSD-MOSFET 随栅压变化的能带图

\* 国家自然科学基金(批准号 50476007)和国家重点基础研究发展计划(973)项目(批准号 2002CB311904)资助的课题。

† E-mail: xytang@mail.xidian.edu.cn

阈值  $V_{BT}$ . 为了区分把表面临界强反型时的栅电压称为沟道阈值  $V_{CHT}$ .  $V_G > V_{BT}$  时电子的势垒高度等于本征势垒高度(图1(c)).  $V_G > V_{CHT}$  时 n 型沟道出现. 栅压越大, 势垒宽度越窄, 电子的隧穿概率增大, 器件开启.

很显然要使器件开启这两个阈值都必须达到. Calvet 等人<sup>[7]</sup>研究了 Si 基 SBSD MOSFET, 认为 SBSD MOS 器件的阈值电压  $V_T = \max(V_{CHT}, V_{BT})$ , 但实际情况并非如此. 当栅压  $V_G > \max(V_{CHT}, V_{BT})$  时, 电流仍可能受到反偏的源极势垒的限制. 以下通过数值模拟对其进行说明.

### 3. 基本模型的选取

采用二维模拟软件 ISE 对 6H-SiC SBSD-NMOSFET 的基本特性进行了模拟. ISE 中对于器件电学特性的模拟描述, 主要是通过求解漂移-扩散模型中的三组方程来实现的, 包括泊松方程, 载流子连续性方程和载流子输运方程. 不同材料和结构的器件需要选用不同的模型. 考虑到 SiC 材料特有的“冻析效应”选择了不完全离化模型. 基于 MOSFET 的结构特点选择了低场迁移率模型和横向场迁移率模型. 低场迁移率模型考虑了晶格散射和电离杂质散射. 横向场迁移率模型考虑了  $\text{SiO}_2/\text{SiC}$  界面处的表面散射, 包括表面声子散射和表面粗糙度散射<sup>[8]</sup>. 由于本文模拟中未涉及高场, 故未计入高场迁移率模型. 针

对这种结构的特殊性需要选择肖特基接触模型. ISE 中对于肖特基接触模型作了如下的定义:

$$\varphi_s = V_{\text{applied}} - \phi_{Bn} + \frac{kT}{q} \ln \left( \frac{N_c}{n_i} \right), \quad (1)$$

$$J_n = qv_n(n_{\text{surf}} - n_0), \\ J_p = -qv_p(p_{\text{surf}} - p_0), \quad (2)$$

$$n_0 = N_c \exp \left( \frac{-q\phi_{Bn}}{kT} \right), \\ p_0 = N_v \exp \left( \frac{-E_g + q\phi_{Bn}}{kT} \right), \quad (3)$$

其中,  $k$  为玻尔兹曼常数,  $\varphi_s$  为肖特基接触处的表面势,  $V_{\text{applied}}$  是偏置电压,  $N_c$  和  $N_v$  是半导体的导带底和价带顶的有效态密度,  $n_i$  是本征载流子浓度,  $J_n$  和  $J_p$  分别是接触处电子和空穴的电流密度,  $n_{\text{surf}}, p_{\text{surf}}$  分别是表面处的电子和空穴浓度,  $n_0$  和  $p_0$  是体内的电子和空穴浓度,  $v_n$  和  $v_p$  是电子和空穴的表面复合速度,  $E_g$  是半导体的禁带宽度.(1)–(3)式是作为求解前述三个基本方程的边界条件.

在常规肖特基接触模型的基础上 ISE 还提供了肖特基势垒隧穿模型. 由于 SBSD-MOSFET 的载流子主要以隧道方式穿过源极肖特基势垒进行传输, 故势垒隧穿模型尤为重要. 该模型的基本思想是把势垒的隧穿电流转换成载流子的产生与复合, 得到产生率与复合率, 然后将其净复合率代入载流子连续性方程进行求解.

$$\Gamma_{\text{WKB}} = \exp \left[ -\frac{2}{h} \int_0^r \sqrt{2m_i(\varphi - \varphi(r')) + \frac{\chi - \chi(r')}{q}} dr' \right], \quad (4)$$

$$G_{st} = \frac{A^* E}{k} \Gamma_{\text{WKB}} T \ln \left\{ 1 + \exp \left[ -\frac{q(\phi_{Bn} + \varphi_s - \varphi) + \chi_s - \chi}{kT} \right] \right\}, \quad (5)$$

$$R_{st} = \frac{A^* E}{k} \Gamma_{\text{WKB}} T \ln \left\{ 1 + \frac{n}{N_c} \right\}. \quad (6)$$

模型中  $\Gamma_{\text{WKB}}$  是 WKB 近似方法得到的隧穿概率,  $G_{st}$  是产生率,  $R_{st}$  是复合率. 其中  $h$  是普朗克常数,  $m_i$  是隧穿有效质量(本文对电子取值  $0.9m_0$ , 对空穴取值  $1.2m_0$ <sup>[9]</sup>,  $m_0$  是电子的静止质量),  $A^*$  是电子或空穴的有效理查逊常数,  $E$  是隧穿方向的电场强度,  $\varphi$  是静电势.  $0 < r' < r$  表示可能发生隧穿的范围,  $r' = 0$  对应金属半导体界面, 角标  $s$  表示金半

接触处的相应物理参数.

### 4. 阈值分析

模拟中采用了 6H-SiC 的材料参数, 考虑了 p 型 6H-SiC 杂质(掺 Al, 离化能 200 meV)的不完全离化. 栅长  $1 \mu\text{m}$ , 氧化层厚度  $20 \text{ nm}$ , 衬底受主掺杂浓度  $N_A$

$= 1 \times 10^{16} \text{ cm}^{-3}$ , 栅极金属功函数取 4.3 eV(Al), 固定氧化物电荷面密度  $1 \times 10^{11} \text{ cm}^{-2}$ , 界面态密度  $1 \times 10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$ (假设界面态在禁带中均匀分布)<sup>[10]</sup>.

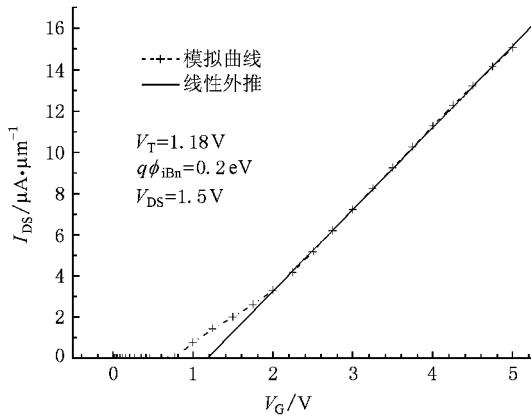

图 2 6H-SiC SBSD-NMOSFET 阈值电压的提取

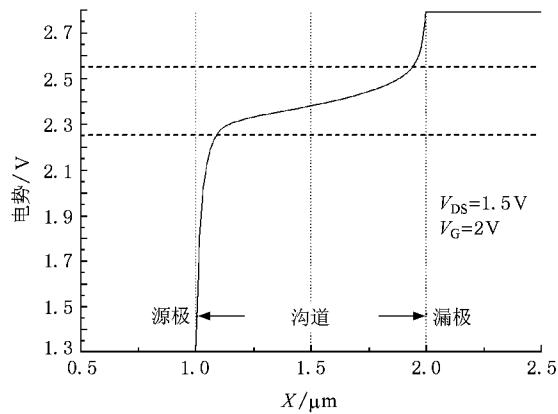

从模拟的转移特性曲线(漏极电流  $I_{DS}-V_G$ )中  $V_G$  轴的线性外推值可以得到室温下该器件的阈值电压, 如图 2. 其中肖特基金属对电子的本征势垒高度  $q\phi_{iBn} = 0.2 \text{ eV}$ , 源漏电压  $V_{DS} = 1.5 \text{ V}$ . 由于源极和漏极肖特基势垒的存在只有少部分源漏电压降落在沟道中, 这一点从沟道表面的电势分布图(图 3)可以看出.

图 3 沟道表面的电势分布

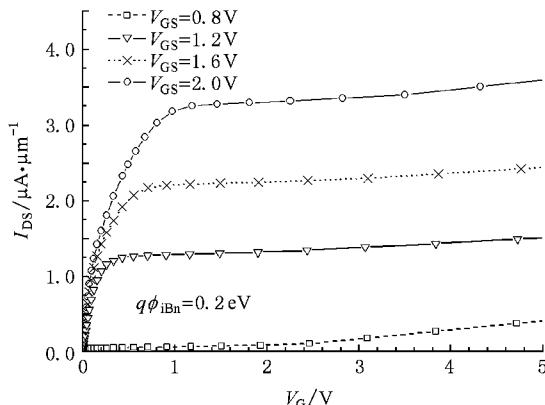

相同条件下得到不同  $q\phi_{iBn}$  的阈值电压列在表 1 中. 通过提取表面电子浓度随栅电压的变化得到沟道阈值  $V_{CHT}$ (表面电子浓度等于衬底浓度时的栅电压). 通过能带图的变化可以得到势垒阈值. 可以看出  $V_T > \max(V_{CHT}, V_{BT})$ . 这意味着即使源漏金属和 SiC 表面形成电子的阻挡层, 同时表面达到强反型, 器件仍受到源极势垒的限制而没能进入线性区. 这

一点通过模拟器件在阈值点附近的输出特性曲线(图 4)可以更为清楚的体现. 因此在 SBSD MOS 器件中规定  $V_{BT}$  和  $V_{CHT}$  中较大的一个为阈值电压只能近似地描述器件的临界开启点.

表 1 不同  $q\phi_{iBn}$  下的阈值电压

| $q\phi_{iBn}/\text{eV}$ | 0.2  | 0.25 | 0.3  |

|-------------------------|------|------|------|

| $V_T/\text{V}$          | 1.18 | 1.39 | 1.52 |

| $V_{BT}/\text{V}$       | 0.71 | 0.65 | 0.59 |

| $V_{CHT}/\text{V}$      | 0.73 | 0.73 | 0.73 |

图 4 6H-SiC SBSD-NMOSFET 在阈值附近的输出曲线

在表面达到强反型后( $V_G \geq V_{CHT}$ ), 源漏电压较小的情况下沟道电导和栅压成近似线性关系. 只有源极电导也和栅压也成近似线形关系后器件才能够进入线性区, 而栅电压达到势垒阈值并不能满足这个条件.

在  $V_G > V_{BT}$  后, 随着栅电压增大电子从源极进入沟道的方式从热发射逐渐向场发射过渡. 在源端反向偏置为  $V_r$  的情况下, 场发射电流可以近似表示为<sup>[11]</sup>

$$J_{FE} \approx C(q\phi_{Bn})TE_{00}(V_G)V_r \times \exp\left(-\frac{q\phi_{Bn}}{E_{00}(V_G)}\right), \quad (7)$$

其中  $C$  是与势垒高度有关的常数.

对(7)式中的指数项做泰勒展开, 取前两项得到

$$J_{FE} \approx CTV_r(E_{00}(V_G) - q\phi_{Bn}), \quad (8)$$

$$E_{00}(V_G) = \frac{qh}{4\pi} \sqrt{\frac{n_{eff}}{m_t \epsilon_s}} = \frac{qh}{4\pi} \sqrt{\frac{C_{ox}(V_G - V_{CHT})}{qd_{inv} m_t \epsilon_s}}. \quad (9)$$

而(9)式中  $C_{ox}$  是栅氧化层电容, 有效沟道厚度

与栅电压近似成  $d_{inv} \propto \frac{1}{V_G - V_{CHT}}$ , 故  $E_{00} \propto (V_G - V_{CHT})$ . 可以看出按场发射方式电子通过源极势垒的电流和栅压成近似线性关系. 这样在表面进入强反型后, 当源极电子主要以场发射方式进入沟道时器件才能进入线性区. 此时的栅电压就是器件的阈值电压.

## 5. 结 论

本文研究了 SiC SBSD-MOSFET 的阈值电压, 指出器件的开启由源漏肖特基势垒和沟道的输运状态

共同控制. 利用二维模拟软件 ISE 对器件的阈值电压进行分析, 提取的阈值电压  $V_T > \max(V_{CHT}, V_{BT})$ , 说明即使源漏金属和 SiC 表面形成少子的阻挡层, 同时表面达到强反型, 器件仍可能受到源极势垒的限制而不能进入线性区. 因此在以往的研究中规定  $V_{BT}$  和  $V_{CHT}$  中较大的一个为阈值电压只能近似地描述器件的临界开启点.

理论分析指出: 当载流子按场发射方式进入沟道, 源极接触电导和栅极电压成近似线性关系. 这样在表面进入强反型后, 当源极载流子主要以场发射方式进入沟道时器件才能进入线性区. 此时的栅电压就是器件的阈值电压.

- [1] Cooper J A ,Melloch M R ,Singh R 2002 *IEEE Transactions on Electron Devices* **49** 658

- [2] Gao J X ,Zhang Y M ,Zhang Y M ,Tang X Y 2002 *Chinese Journal of Semiconductors* **23** 408 (in Chinese) [ 邹锦侠、张义门、张玉明、

汤晓燕 2002 半导体学报 **23** 408 ]

- [3] Wang Y ,Zhang Y M ,Zhang Y M ,Tang X Y 2003 *Acta Phys . Sin.* **52** 2553 [ 王 源、张义门、张玉明、汤晓燕 2003 物理学报 **52** 2553 ]

- [4] Kedzierski J ,Xuan P ,Anderson E H 2000 *IEDM Tech . Digest* 57

- [5] Moongyu Jang ,Seongjae Lee ,and Kyungwan Park 2003 *IEEE Transactions on Nanotechnology* **2** 205

- [6] Moongyu Jang ,Kicheon Kang ,Seongjae Lee 2003 *Applied Physics Letters* **82** 21

- [7] Calvet L E ,Luebben H ,Reed M A 2000 *Superlattices and Microstructures* **28** 501

- [8] Integr. Syst. Eng. San Jose CA 95113 ,2001 Inc. ,ISE 7.0 USER manual

- [9] Crofton J ,Sriram S 1996 *IEEE Transactions on Electron Devices* **43** 2305

- [10] Ciobanu F ,Frank T ,Pensl G 2006 *Mater . Sci . Forum* **527-529** 991

- [11] Laurie Ellen Calvet 2001 *A dissertation of Yale University for the Degree of Doctor Chapter* **2** 30

# The threshold voltage of SiC Schottky barrier source/drain MOSFET<sup>\*</sup>

Tang Xiao-Yan<sup>†</sup> Zhang Yi-Men Zhang Yu-Ming

(Key Lab of Ministry of Education for Wide Band-Gap Semiconductor Materials and Devices, Microelectronics Institute, Xidian University, Xi'an 710071, China)

(Received 15 May 2008; revised manuscript received 14 July 2008)

## Abstract

Threshold voltage of SiC Schottky barrier source/drain MOSFET( SBSD MOSFETs ) is different from the threshold voltage of traditional MOSFETs. Based on a comprehensive analysis of the operational mechanism, the threshold voltage of SBSD MOSFET is extracted and analyzed with 2-D simulator ISE. The threshold voltage of the device is defined as the gate voltage at which carriers from the source contact enter the channel by field emission while the channel is strongly inverted.

**Keywords:** silicon carbide, Schottky contact, threshold voltage

**PACC:** 7280, 7330, 7340S, 7220

\* Project supported by the National Nature Science Foundation of China( Grant No. 60476007 ) and the National Basic Research Program( 973 Program ) of China( Grant No. 2002CB311904 ).

† E-mail :xytang@mail.xidian.edu.cn