# 亚 100 nm 应变 Si/SiGe nMOSFET 阈值电压二维解析模型<sup>\*</sup>

王冠宇<sup>†</sup> 张鹤鸣 王晓艳 吴铁峰 王斌

(西安电子科技大学微电子学院, 宽禁带半导体材料与器件重点实验室, 西安 710071)

(2010 年 6 月 29 日收到; 2010 年 10 月 19 日收到修改稿)

本文基于二维泊松方程, 建立了适用于亚 100 nm 应变 Si/SiGe nMOSFET 的阈值电压理论模型。为了保证该模型的准确性, 同时考虑了器件尺寸减小所导致的物理效应, 如短沟道效应, 量子化效应等。通过将模型的计算结果与二维器件模拟器 ISE 的仿真结果进行对比分析, 证明了本文提出的模型的正确性。最后, 还讨论了亚 100 nm 器件中常规工艺对阈值电压的影响。该模型为亚 100 nm 小尺寸应变 Si 器件的分析设计提供了一定的参考。

**关键词:** 亚 100 nm, 应变 Si/SiGe nMOSFET, 二维表面势, 阈值电压

**PACS:** 71.23. An, 71.70. Fk

## 1. 引言

根据摩尔定律和器件的等比例缩小原则, 集成电路的集成度和复杂性随之增强, Si 基 MOSFET 器件特征尺寸不断减小, 从而导致了一系列涉及材料、器件物理和结构方面的新问题。当器件尺寸不断缩小至亚 100 nm 甚至纳米级, 传统的等比例缩小方法很难进一步提升器件的性能<sup>[1]</sup>。为此, 新型半导体材料和器件结构成为目前研究的重点。由于 Si 基 Si/SiGe 应变材料具有迁移率高, 能带结构可调, 应变实现方式简单, 并与传统 Si 工艺完全兼容等令人瞩目的优点, 所以利用 Si 基应变材料来提高器件性能已经成为研究设计高速、高性能小尺寸 MOSFET 器件与电路的首选方案<sup>[2-4]</sup>。

随着器件特征尺寸的不断缩小, 沟道掺杂浓度也随之增加, 栅氧厚度减小, 从而导致了表面电场的提高。此时, 经典的缓变沟道近似不再成立, 一些物理效应也开始变得十分明显, 例如短沟道效应, 表面量子化效应, 重掺杂禁带宽度变窄效应等。为了建立准确的二维阈值电压模型则必须考虑包括这些物理效应。作为器件最重要的物理参数之一,

目前国内外关于应变 Si/SiGe nMOSFET 的阈值电压模型研究多集中于长沟道的一维分析<sup>[5-7]</sup>, 而真正适用于亚 100 nm 小尺寸应变 Si 器件的阈值电压模型则鲜有报道, 而且这些已经报道的一维模型并未完全考虑上述物理效应。基于此, 本文的目的是为亚 100 nm 应变 Si/SiGe nMOSFET 建立一个更加准确适用的二维阈值电压模型。首先利用二维泊松方程, 建立了物理意义明确的二维沟道表面势模型, 然后综合考虑了小尺寸器件的物理效应对阈值电压的影响, 最后得到了二维阈值电压的解析表达式。

## 2. 理论模型推导

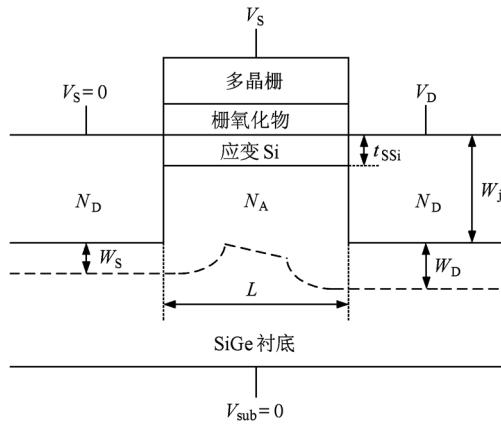

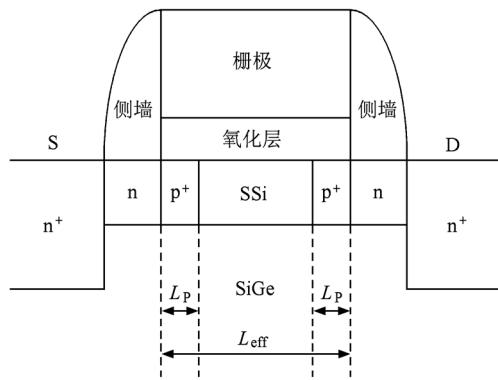

应变 Si/SiGe nMOSFET 的器件剖面结构以及几何结构参数如图 1 所示。图中,  $t_{\text{SSi}}$  表示应变 Si 沟道的厚度;  $L$  为沟道长度;  $W_s$  和  $W_d$  分别表示两侧源漏区的耗尽宽度; 源漏掺杂浓度为  $N_d$ 。为了使模型简洁, 突出其物理意义, 我们首先假设几个理想化条件: 1) 氧化层中无杂质电荷; 2) 应变 Si 沟道完全耗尽, 且强反型刚刚开始时, 沟道自由电荷可忽略不计; 3) 应变 Si 沟道厚度相比于源漏结深一般很小, 近似认为源漏结深  $W_j$  对阈值电压无影响; 4) 衬底

\* 国家部委资助项目(批准号: 51308040203, 6139801), 中央高校基本科研业务费(批准号: 72105499, 72104089) 和陕西省自然科学基础研究计划(批准号: 2010JQ8008) 资助的课题。

† Email: SiGeBiCMOS@foxmail.com

电极接地,  $V_{\text{sub}} = 0$ , 且漏电压  $V_{\text{DS}}$  很小. 同时规定平行于沟道的方向为  $x$  方向, 垂直于沟道的方向为  $y$  方向, 并取沟道与源级交界面的位置为  $x$  方向坐标原点.

图 1 应变 Si/SiGe nMOSFET 器件剖面结构

## 2.1. 二维沟道表面势理论模型

沟道表面势是小尺寸 MOSFET 的重要物理参数之一, 它直接决定着器件的阈值电压的大小. 对于小尺寸器件, 传统的缓变沟道近似已不再适用, 沟道横向表面电势不再是恒定不变的, 所以我们必须使用二维分析来描述器件的物理特性. 设定  $\text{SiO}_2/\text{Si}$  界面处  $y=0$ , 强反型刚刚开始时, 忽略应变 Si 沟道可动电荷, 那末二维泊松方程则可写为

$$\frac{\partial^2 \psi_{\text{ssi}}(x, y)}{\partial x^2} + \frac{\partial^2 \psi_{\text{ssi}}(x, y)}{\partial y^2} = \frac{qN_A}{\epsilon_{\text{ssi}}} \quad (0 \leq x \leq L, 0 \leq y \leq t_{\text{ssi}}), \quad (1)$$

其中,  $\psi_{\text{ssi}}(x, y)$  为应变 Si 沟道中的二维电势,  $\epsilon_{\text{ssi}}$  为应变 Si 的介电常数. 根据文献[8], 在  $y$  方向上, 沟道区域的电势  $\psi_{\text{ssi}}(x, y)$  近似服从平方分布, 表达式如下:

$$\psi_{\text{ssi}}(x, y) = \psi_{\text{s,ssi}}(x) + C_1(x)y + C_2(x)y^2 \quad (0 \leq y \leq t_{\text{ssi}}). \quad (2)$$

同样地, 为了避免过于繁琐的数学运算, 便于得到解析表达式, 设定弛豫 SiGe 衬底耗尽区边界处  $Y=0$ , 则 SiGe 衬底区域的电势也可以近似为平方

分布

$$\psi_{\text{SiGe}}(x, Y) = \psi_{\text{s,SiGe}}(x) + C_3(x)Y + C_4(x)Y^2 \quad (0 \leq Y \leq t_{\text{SiGe}}), \quad (3)$$

式中的  $\psi_{\text{s,SiGe}}(x) = V_{\text{sub}} = 0$  为 SiGe 层耗尽边界处的表面势, 这里  $t_{\text{SiGe}}$  代表 SiGe 层的耗尽宽度.  $C_1(x)$ ,  $C_2(x)$ ,  $C_3(x)$ ,  $C_4(x)$  是关于  $x$  的常函数, 联立(2), (3)两式, 其值可由如下 3 个边界条件确定:

(i)  $\text{SiO}_2/\text{应变 Si}$  交界面处 ( $y=0$ ) 电位移矢量连续:

$$\left. \frac{\partial \psi_{\text{ssi}}(x, y)}{\partial y} \right|_{y=0} = -\frac{V_{\text{GS}} - V_{\text{FB}} - \psi_{\text{s,ssi}}(x)}{\gamma_1 t_{\text{ox}}}, \quad (4)$$

$\gamma_1 = \epsilon_{\text{ssi}}/\epsilon_{\text{ox}}$ ,  $\epsilon_{\text{ox}}, t_{\text{ox}}$  分别为氧化层的介电常数和厚度,  $V_{\text{FB}}$  表示平带电压.

(ii) SiGe 耗尽区边界处 ( $Y=0$ ) 电场为 0,

$$\left. \frac{\partial \psi_{\text{SiGe}}(x, Y)}{\partial Y} \right|_{Y=0} = 0. \quad (5)$$

(iii) Si/SiGe 异质结界面处电势和电位移矢量均连续,

$$\psi_{\text{ssi}}(x, t_{\text{ssi}}) = \psi_{\text{SiGe}}(x, t_{\text{SiGe}}), \quad \left. \frac{\partial \psi_{\text{ssi}}(x, y)}{\partial y} \right|_{y=t_{\text{ssi}}} = -\left. \frac{\partial \psi_{\text{SiGe}}(x, Y)}{\partial Y} \right|_{Y=t_{\text{SiGe}}}, \quad (6)$$

其中,  $\gamma_2 = \epsilon_{\text{ssi}}/\epsilon_{\text{SiGe}}$ . 然后将  $C_1(x)$ ,  $C_2(x)$  分别代入(2)式中, 同时令(1)式中  $y=0$ , 这样经过整理, 我们可以得到一个关于  $\psi_{\text{s,ssi}}(x)$  的二阶常系数微分方程

$$\frac{d^2 \psi_{\text{s,ssi}}(x)}{dx^2} - \alpha \psi_{\text{s,ssi}}(x) = \beta, \quad (7)$$

式中

$$\alpha = \frac{[\gamma_2(W_d - t_{\text{ssi}}) - 2(t_{\text{ssi}} - \gamma_1 t_{\text{ox}})]}{2\gamma_1 t_{\text{ox}} t_{\text{ssi}} [\gamma_2(W_d - t_{\text{ssi}}) - t_{\text{ssi}}]},$$

$$\beta = \frac{qN_A}{\epsilon_{\text{ssi}}} - \frac{[\gamma_2(W_d - t_{\text{ssi}}) - 2t_{\text{ssi}}](V_{\text{GS}} - V_{\text{FB}})}{2\gamma_1 t_{\text{ox}} t_{\text{ssi}} [\gamma_2(W_d - t_{\text{ssi}}) - t_{\text{ssi}}]}.$$

为了求解(7)式, 应用如下 2 个边界条件:

(iv)  $\psi_{\text{s,ssi}}(0) = V_{\text{bi,ssi}}$ ; (v)  $\psi_{\text{s,ssi}}(L) = V_{\text{bi,ssi}} + V_{\text{DS}}$ , 并注意到  $-\beta/\alpha$  为微分方程的一个特解, 则(7)式的解可写为

$$\psi_{\text{s,ssi}}(x) = A \exp(\lambda x) + B \exp(-\lambda x) - \beta/\alpha, \quad (8)$$

其中  $A, B$  为以下常数:

$$A = \left[ \frac{(V_{\text{bi,ssi}} + V_{\text{DS}} + \beta/\alpha) - (V_{\text{bi,ssi}} + \beta/\alpha) \exp(-\lambda L)}{1 - \exp(-2\lambda L)} \right] \times \exp(-\lambda L),$$

$$B = \frac{(V_{\text{bi,ssi}} + \beta/\alpha) - (V_{\text{bi,ssi}} + V_{\text{DS}} + \beta/\alpha) \exp(-\lambda L)}{1 - \exp(-2\lambda L)},$$

$\lambda = \sqrt{\alpha}$ ,  $V_{bi,ssi} = (kT/q)\ln(N_A N_D/n_{i,ssi}^2)$  为源极-沟道结的自建电势.

此外,注意到在平带条件下,由于较大的价带断续  $\Delta E_v$  的存在,体内的空穴在应变 Si/SiGe 界面处积累形成了偶极层,使界面处能带弯曲,从而影响了平带电压. 因应变 Si 层一般很薄,则需计入偶极层的影响. 利用高斯定理,可以得到偶极层的电势  $\psi_{dipole}$ <sup>[9]</sup> 为

$$\psi_{dipole} = \frac{qN_A t_{ssi}^2}{2\epsilon_{ssi}} + \frac{qN_A t_{ssi} L_d \sqrt{2}}{2\epsilon_{ssi}}, \quad (9)$$

式中,  $L_d = \sqrt{kT\epsilon_{SiGe}/q^2 N_A}$  为德拜长度. 同样由文献[9],(4)式中的平带电压  $V_{FB}$  可以进一步表示为

$$V_{FB} = \frac{\phi_{gate}}{q} - \left[ \chi_{SiGe} + \frac{E_{g,SiGe}}{q} - \frac{kT}{q} \ln\left(\frac{N_{v,SiGe}}{N_A}\right) \right] - \psi_{dipole}, \quad (10)$$

其中,  $\chi_{SiGe}$  与  $N_{v,SiGe}$  分别为弛豫 SiGe 的亲和势与价带有效状态密度.  $\phi_{gate}$  为栅极材料的功函数.

## 2.2. 二级物理效应的影响

和其他小尺寸器件一样,在亚 100 nm 应变 Si/SiGe nMOSFET 中,由于高的掺杂浓度和很强的纵向电场的影响,沟道内的电子输运特性同样发生改变,在平行于  $SiO_2$ /应变 Si 界面的平面内仍遵循经典的运动规律,而在垂直该界面的方向上则出现了量子化效应,电子运动既要服从麦克斯韦方程又要服从薛定格方程,因此电子在沟道中的分布不同于经典情况,从而导致栅电容和阈值电压发生变化.

在体 Si 器件中,根据经典的器件物理,强反型开始时的阈值表面势  $\psi_{th,Si}$  定义为两倍体内费密势,即  $\psi_{th,Si} = 2\psi_f$ . 但是在量子化条件下,由于表面处能级分裂为一系列的子能级,导致了表面势的改变,因此该阈值条件不能准确成立,必须对其进行量子化修正. 文献[10]提出了一种新的量子化阈值条件,表示为

$$\frac{dQ_{inv}}{d\phi_S} \Big|_{\phi_{th,Si}} = \frac{dQ_{dep}}{d\phi_S} \Big|_{\phi_{th,Si}} \Leftrightarrow \frac{dQ_{inv}}{dV_{GS}} \Big|_{V_{th,Si}} = \frac{dQ_{dep}}{dV_{GS}} \Big|_{V_{th,Si}}, \quad (11)$$

式中,  $Q_{inv}$  和  $Q_{dep}$  分别为反型层电荷密度与总的耗尽层电荷密度. 在量子化条件下,表面势随掺杂浓度的变化关系可以由(11)式的自治解得出,据此,文献[11]给出了量子化阈值表面势的解析式

$$\psi_{th,ssi}^{QM} = 2\psi_f + \frac{kT}{q} \times m \times \left(\frac{N_A}{10^{17}}\right)^n, \quad (12)$$

其中,  $m = 1.785$ ,  $n = 0.3522$  为数值拟合系数.

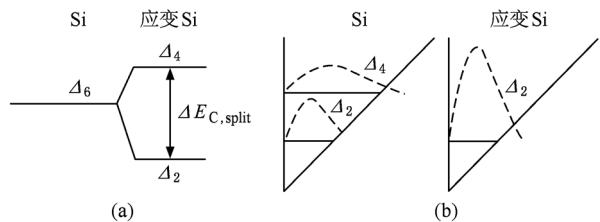

在应变 Si 器件中,由于应变的作用,导带分裂为二度简并能谷  $\Delta_2$  和四度简并能谷  $\Delta_4$  (如图 2 所示),导致  $\Delta_2$  能谷电子数增加,  $\Delta_4$  能谷电子数减少. 而实际上,超过 90% 的电子填充了  $\Delta_2$  能谷的基态子能级  $E_0$ <sup>[12]</sup>, 因此我们可以假设应变 Si 表面反型层形成一个三角形势阱,且只有最低基态子能级中包含电子,即第一能级近似. 相对于导带底,基态子能级能量可以表示为<sup>[13]</sup>

$$E_0 = \frac{(q\hbar F_s)^{2/3}}{(2m_y)^{1/3}} \times S_0, \quad (13)$$

式中,  $m_y$  为垂直方向( $y$  方向)电子的量子化有效质量,  $F_s$  为  $y$  方向上的表面电场,  $\hbar = h/2\pi$  ( $h$  为普朗克常数),  $S_0 = \left[\frac{9}{8}\pi\right]^{2/3}$ .

图 2 应变对 Si 能带结构的改变 (a) 导带分裂;(b) 应变 Si 和体 Si 的能谷分布

在量子化条件下,相对于同样器件结构参数的体 Si nMOSFET,无论应变 Si 层是否完全耗尽,发生强反型时应变 Si/SiGe nMOSFET 的反型层电荷应与体 Si 器件的反型层电荷相等<sup>[14]</sup>,据此,文献[14]给出了应变 Si 沟道阈值表面势与体 Si 沟道表面势的关系

$$\psi_{th,ssi}^{QM} \approx \psi_{th,Si}^{QM} + \frac{kT}{q} \ln\left(\frac{N_{v,Si}}{N_{v,ssi}}\right) - \frac{\Delta E_{g,ssi}}{q}, \quad (14)$$

式中,  $\Delta E_{g,ssi}$  表示由应变引起的禁带宽度变化量.  $N_{v,Si}$  与  $N_{v,ssi}$  分别为体 Si 与应变 Si 价带有效态密度,且满足  $N_{v,Si}/N_{v,ssi} = (m_{p,Si}/m_{p,ssi})^{3/2}$ .  $m_{p,ssi}$  为应变 Si 中空穴的有效质量. 实际上,在应力的作用下,  $m_{p,ssi}$  相比于体 Si 的  $m_{p,Si}$  有着更加明显的各向异性,为了使模型更加准确,则必须考虑其各向异性. 基于  $k \cdot p$  理论框架,我们求得了(001)面应变 Si 价带边的  $E(k)$ - $k$  关系,最终计算出  $m_{p,ssi}$ ,详细计算过程参见文献[15]. 这里,仅将常用的几个晶向的计算结果列于表 1.

表 1 (001) 面沿不同晶向的空穴有效质量/ $m_0$

| Ge 组分 | [001]  | [111] | [010] | [110] | [−101] |

|-------|--------|-------|-------|-------|--------|

| 0.1   | 0.0782 | 0.19  | 0.093 | 0.14  | 0.14   |

| 0.2   | 0.0778 | 0.172 | 0.094 | 0.142 | 0.1337 |

| 0.3   | 0.0767 | 0.168 | 0.093 | 0.144 | 0.1320 |

另外,由于量子化效应造成了电子的波函数的峰值点偏移了表面,偏移距离为  $\Delta t$ ,这等效于栅氧化层的有效厚度增加了( $\Delta t/\gamma_1$ ).其中  $\Delta t$  可由(13)式推得

$$\Delta t = (S_0 - 1) \left( \frac{2qm_y}{\hbar^2} F_{s,ssi} \right)^{-1/3}. \quad (15)$$

由高斯定理知  $F_{s,ssi} \approx qN_A W_d / \epsilon_{ssi}$ .  $W_d$  为总的耗尽宽度,在量子化条件下,同时考虑到短沟道效应,  $W_d$  可借助一维泊松方程求出

$$W_d = \kappa \sqrt{\left(1 - \frac{1}{\gamma_2}\right) t_{ssi}^2 + \frac{2\epsilon_{SiGe}}{qN_A} \phi_{th,ssi}^{QM}}, \quad (16)$$

其中  $\kappa = [1 - 2\exp(-L/\lambda_d)]^{-1}$  是描写短沟道效应的因子<sup>[16]</sup>,  $\lambda_d = \xi(W_s + W_d)$ ,  $\xi = 0.65$ , 在很小的  $V_{DS}$  下,  $W_s$  与  $W_d$  的值近似为

$$W_s \approx W_d \approx \sqrt{\frac{2\epsilon_{SiGe}}{q} \frac{N_D}{N_A} \left( \frac{V_{bi,SiGe}}{N_D + N_A} \right)}. \quad (17)$$

同理,根据(15)式,将(8)式中的氧化层厚度量子化修正为

$$t_{ox}^{QM} = t_{ox} + \frac{\Delta t}{\gamma_1} = t_{ox} + \left( \frac{S_0 - 1}{\gamma_1} \right) \left( \frac{2qm_y}{\hbar^2} F_{s,ssi} \right)^{-1/3}. \quad (18)$$

由于栅氧化层的有效厚度增加,同时也意味着有氧化层中存在着密度为  $qN_A \Delta t$  的电荷,这部分电荷使氧化层充电,也导致了在平带电压  $V_{FB}$  上叠加了一个电场,所以必须对(11)式的平带电压予以修正,修正后的平带电压表示为

$$V_{FB}^{QM} = V_{FB} + \frac{1}{2} \frac{qN_A \Delta t^2}{\epsilon_{ssi}} + qN_A \Delta t \left( \frac{t_{ox}}{\epsilon_{ox}} \right). \quad (19)$$

在小尺寸器件中,应变 Si 层的厚度一般很薄(5—15 nm 左右),由于晶格失配,应变 Si/SiGe 异质结界面处的形貌比较粗糙,界面粗糙度不可忽略,且直接影响了应变 Si 沟道的有效厚度,最终导致应变 Si 反型层的基态能级和阈值电压的改变.根据文献[17]中的分析,基态能级  $E_0$  随应变 Si 厚度的变化而变化,在整个平面内其平均值则近似为

$$E_0 = \langle E_0(t_{ssi} + \Delta(r)) \rangle \approx E_0(t_{ssi}) + \frac{1}{2} \frac{\partial^2 E_0}{\partial t_{ssi}^2} \langle \Delta(r) \rangle^2, \quad (20)$$

其中,  $\Delta(r)$  是关于表面粗糙度波矢  $r$  的函数,在生长平面内其平均值约为 1.1 nm.为了获得  $E_0$  与  $t_{ssi}$  的函数关系,我们不妨假设  $SiO_2$ /应变 Si/SiGe 异质结构形成一个一维方形势阱,这样我们就可以利用方形势阱近似得到

$$E_0 = \frac{1}{2} \frac{\hbar^2 \pi^2}{m_y t_{ssi}^2}. \quad (21)$$

那末由于表面粗糙度所引起的阈值电压的改变量可以写为

$$\begin{aligned} \Delta V_{th}^{SR} &= \frac{1}{2q} \frac{\partial^2 E_0}{\partial t_{ssi}^2} \langle \Delta(r) \rangle^2 \\ &= \frac{3}{2} \frac{\hbar^2 \pi^2}{qm_y t_{ssi}^4} \langle \Delta(r) \rangle^2. \end{aligned} \quad (22)$$

在小尺寸器件中,沟道和衬底一般掺杂浓度很高,所以这时就不能不考虑由重掺杂所导致的禁带宽度变窄效应(BGN),文献[18]给出了禁带宽度改变量的解析式: $\Delta E_{g,BGN} = 18 \ln(N_A/10^{17})$  meV.由于本文中应变 Si 沟道和衬底使用了统一掺杂,应变 Si 和 SiGe 的禁带宽度均变窄,若体现在对阈值电压的改变,可以取二者改变量的平均值  $\Delta E_{g,BGN}/2$ ,则阈值电压增加了  $\Delta E_{g,BGN}/2q$ .

另外,由于超薄氧化层的存在,若使用多晶 Si 栅极,还需要考虑栅极耗尽效应,最终导致阈值电压的升高  $\Delta V_{th}^{poly}$ .根据电场-电势关系,求得  $\Delta V_{th}^{poly}$  如下:

$$\begin{aligned} \Delta V_{th}^{poly} &= \frac{1}{2} W_{d,poly} F_{poly} \\ &= \frac{1}{2} \frac{qN_A W_d^2}{\epsilon_{ssi} N_{poly}} \\ &= \frac{N_A}{N_{poly}} \psi_{th,ssi}^{QM}, \end{aligned} \quad (23)$$

其中,  $W_{d,poly}$  与  $F_{poly}$  分别为多晶 Si 栅极的耗尽宽度和电场强度,  $N_{poly}$  为多晶 Si 掺杂浓度.

### 2.3. 二维阈值电压解析模型

在二维表面势模型中,最小表面势点  $x_{min}$  可以由  $d\psi_{s,ssi}(x)/dx = 0$  来求出,  $x_{min} = \lambda [\ln(B/A)/2]$ , 将其代入(8)式中,我们可以得到沟道最小表面势为

$$\psi_{s,ssi}^{min} = \psi_{s,ssi}(x_{min}) = 2 \sqrt{AB} - \beta/\alpha. \quad (24)$$

当器件开启时,此时的最小表面势  $\psi_{s,ssi}^{min}$  即为刚达到强反型时沟道阈值电势  $\psi_{th,ssi}^{QM}$ ,满足  $\psi_{s,ssi}(x_{min}) = \psi_{th,ssi}^{QM}$  的栅源电压  $V_{GS}$  即为  $V_{th}$ ,进一步求得考虑量

子化效应的  $V_{th}$  的解析表达式如下:

$$V_{th}^{QM} = \frac{\alpha \psi_{th,ssi}^{QM} [\exp(\lambda L) + 1]^2 + \frac{qN_A}{\epsilon_{ssi}} [\exp(\lambda L) - 1]^2 - 4\alpha V_{bi,ssi} \exp(\lambda L) + \zeta V_{FB}^{QM} [\exp(\lambda L) - 1]^2}{[\exp(\lambda L) - 1]^2 \zeta} - \frac{2\alpha V_{DS} \exp(\lambda L) + 2\alpha \exp(\lambda L/2) [\exp(\lambda L) + 1] \sqrt{(\psi_{th,ssi}^{QM} - V_{bi,ssi})(\psi_{th,ssi}^{QM} - V_{bi,ssi} - V_{DS})}}{[\exp(\lambda L) - 1]^2 \zeta}, \quad (25)$$

式中常数  $\zeta = (a - 2t_{ssi})/2ab$ ;  $a = \gamma_2 W_d + (1 + \gamma_2)t_{ssi}$ ;  $b = \gamma_1 t_{ssi} t_{ox}^{QM}$ .

另外需要注意的是,如果源漏偏置电压  $V_{DS}$  很大,则上述模型还需计入漏致势垒降低(DIBL)效应的影响. DIBL 造成的阈值电压减小量与  $V_{DS}$  成线性关系:  $\Delta V_{th}^{DIBL} = \sigma V_{DS}$ ,  $\sigma = \epsilon_{ssi}/\pi LC_{ox}^{QM}$  为 DIBL 因子<sup>[19]</sup>.

综上所述,小尺寸应变 Si/SiGe nMOSFET 二维阈值电压理论上可表示为

$$V_{th} = V_{th}^{QM} + \Delta V_{th}^{SR} + \Delta V_{th}^{poly} + \Delta V_{th}^{DIBL} + \frac{\Delta E_{g,BGN}}{2q}. \quad (26)$$

### 3. 结果与讨论

#### 3.1. 理论模型结果与分析

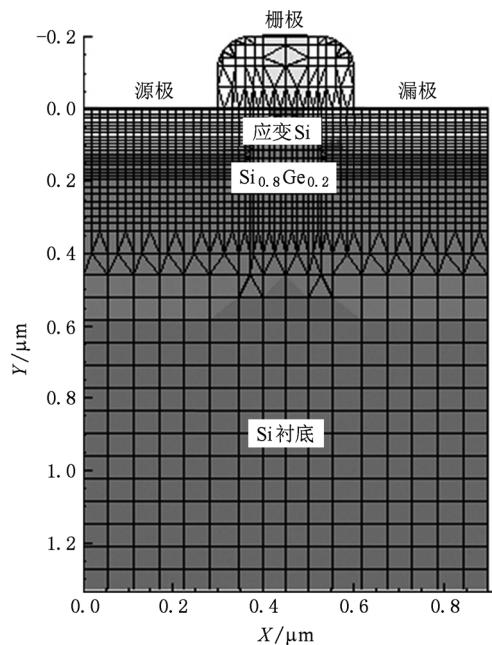

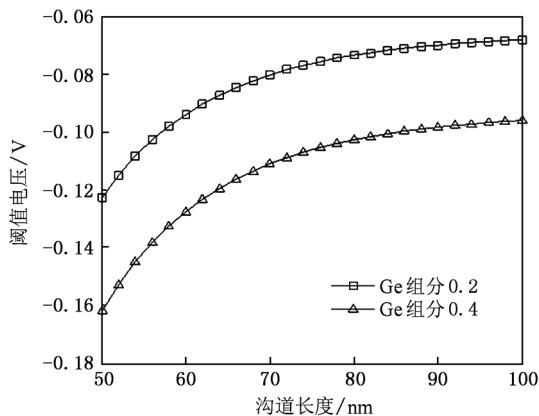

为了验证本文提出的理论模型的正确性,首先将本文模型用 MATLAB 软件进行计算,应变 Si 沟道选用[001]晶向. 因目前真正适用于小尺寸应变 Si 器件的阈值电压模型鲜有报道,因此本文的计算结果主要与二维器件模拟器 Synopsys ISE TCAD® 10.0 中的仿真结果进行比较. 仿真用器件的网格划分如图 3 所示,模型计算结果如图 4 所示. 从图 4 中可以看出,随着沟道长度的不断缩短,阈值电压陡降,体现出明显的短沟道效应. 表 3 是计算结果和仿真结果的比较,阈值电压的仿真结果是通过应变 Si/SiGe nMOSFET 的转移特性来提取的. 可以看到,本文的模型计算结果同仿真数据较为接近,证明了前述理论模型的正确性. 其最大误差约为 10%,造成该最大偏差的原因可能是因为弛豫 SiGe 层的热导率较低,随着器件的尺寸缩小至 50 nm,实际的自加热效应变得更加明显.

需注意的是,器件的阈值电压为负,这是由于当栅压  $V_{GS}$  很小时,小尺寸器件相对于长沟道器件

有更强的表面电场,沟道表面能带更加弯曲,造成表面三角形势阱(图 2(b))深度增加;另一方面,随着 Ge 组分的增加,Si 与 SiGe 的导带断续  $\Delta E_c$  亦随之增大,有更多数量的电子易于在沟道应变 Si/SiGe 量子阱之中积累,这就导致了器件在关态的时候沟道中的电子面密度已经达到强反型的阈值条件,沟道随之导通,器件成为常开型(耗尽型),需加一定的负栅压以维持器件的关态. 按照器件物理学的定义,此时所加的负栅压即为器件的阈值电压.

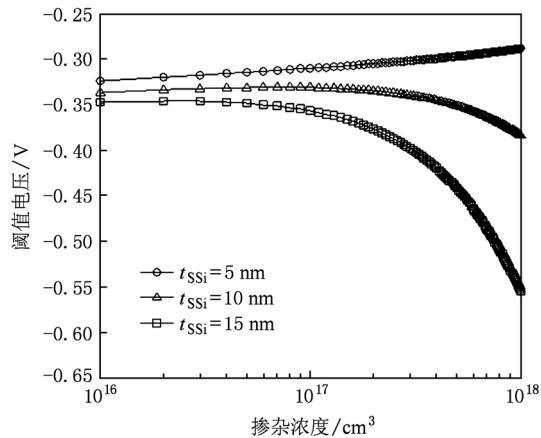

对于亚 100 nm 的小尺寸 nMOSFET,在较小的漏偏压下,影响阈值电压的因素主要是量子化效应和短沟道效应,为了进一步说明二者对阈值电压的综合影响,我们首先取不同厚度的应变 Si 沟道来进行比较(如图 5 所示). 计算时 Ge 组分取 0.2, 沟道长度 50 nm,掺杂浓度  $1 \times 10^{16}$ — $1 \times 10^{18} \text{ cm}^{-3}$ , 沟道厚度分别为 5, 10, 15 nm, 其余参数同表 1. 由图可见,在不同的沟道厚度下,两种效应对阈值电压的

图 3 器件结构仿真模型及网格划分

控制能力是不同的。当沟道厚度较大时( $t_{\text{SSI}} = 15 \text{ nm}$ )，阈值电压随掺杂浓度的增大而单调下降，体现出明显的短沟道效应。注意到量子化效应应该使阈值电压增大，但此时的阈值电压反而减小，这就说明此时阈值电压主要由短沟道效应控制，量子化效应的影响较弱。其物理原因是沟道越厚，沟道表面的三角形势阱越宽，这样量子化所引起的子能级分裂程度越小，从而量子化效应减弱。随着沟道厚度不断减小，阈值电压降低的幅度也减小，说明量子化效应不断增强。当 $t_{\text{SSI}} = 5 \text{ nm}$ 时，阈值电压不再降低反而升高，这是因为势阱中子能级分裂得更开，此时的量子化效应相对于短沟道效应更加显著的缘故。

图4 阈值电压随沟道长度的变化

表2 理论模型中器件主要结构参数

|                                       |                      |

|---------------------------------------|----------------------|

| 应变 Si 沟道厚度 $t_{\text{SSI}}/\text{nm}$ | 15                   |

| 栅氧化层厚度 $t_{\text{OX}}/\text{nm}$      | 2                    |

| 沟道和衬底掺杂浓度 $N_A/\text{cm}^{-3}$        | $1 \times 10^{18}$   |

| 源漏掺杂浓度 $N_D/\text{cm}^{-3}$           | $2 \times 10^{20}$   |

| 沟道长度 $L/\text{nm}$                    | 50—100               |

| 源漏电压 $V_{\text{DS}}/\text{mV}$        | 50                   |

| Ge 组分                                 | 0.2, 0.4             |

| $n^+$ 多晶 Si 栅极功函数/eV                  | 4.35                 |

| $n^+$ 多晶 Si 栅极掺杂浓度/ $\text{cm}^{-3}$  | $0.5 \times 10^{20}$ |

表3 理论模型计算结果与仿真结果的比较

| 沟道长度/nm | 计算结果/V | 仿真结果/V |

|---------|--------|--------|

| 50      | -0.122 | -0.468 |

| 60      | -0.193 | -0.43  |

| 70      | -0.18  | -0.4   |

| 80      | -0.173 | -0.392 |

图5 不同沟道厚度下阈值电压随浓度的变化

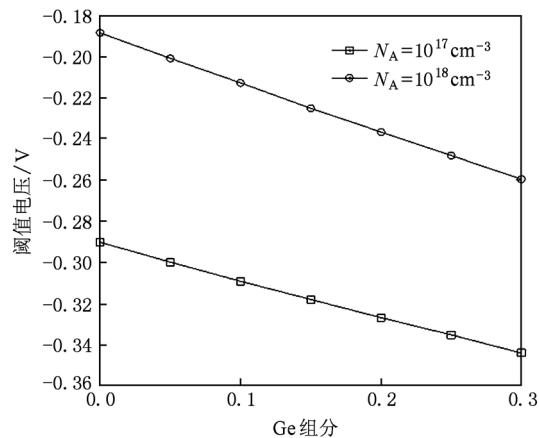

图6 不同浓度下阈值电压随Ge组分的变化

图6表示的是沟道长度25 nm, 沟道厚度为5 nm条件下, 两种不同掺杂浓度条件下阈值电压随弛豫SiGe虚拟衬底中Ge组分的变化情况。从图中我们可以看出, 随着Ge组分的不断增大, 阈值电压近似呈线性下降, 这是由于应变Si/SiGe量子阱的深度与Ge组分成正比, 量子阱愈深, 电子愈容易在阱中积累并达到反型, 导致电子面密度增加, 从而阈值电压愈低。此外, 若Ge组分一定, 掺杂浓度愈高, 阈值电压愈大, 由(26)式可知, 这是由于高掺杂浓度使得禁带宽度变窄效应和量子化效应对阈值电压的影响变得更加明显, 导致阈值电压升高。

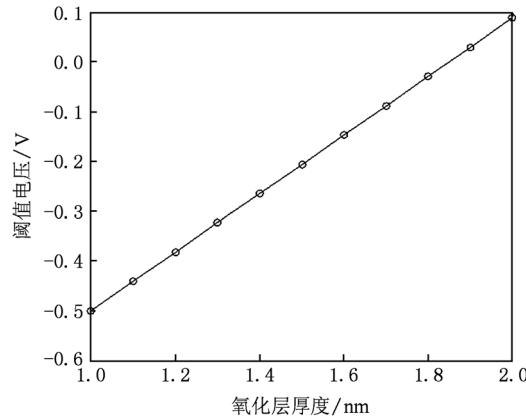

栅氧化层厚度对阈值电压的影响示于图7。掺杂浓度为 $1 \times 10^{18} \text{ cm}^{-3}$ , Ge组分0.2, 其余条件同前。我们可以明显看出, 阈值电压随栅氧厚度的增加而显著增加。这是因为栅氧厚度的增加导致(19)式中的平带电压增加, 从而(25)式中的量子化阈值电压升高所致。实际上, 如果栅氧厚度增加, 则多晶Si栅

极耗尽效应减弱,应变 Si 沟道表面三角形势阱中的电场减小,导致量子化效应亦随之减弱,这两个效应的减弱会使阈值电压降低,只不过降低的幅度小于平带电压增大的幅度,因而总体上阈值电压还是随栅氧厚度增加而增大。

图 7 阈值电压随栅氧化层厚度的变化

### 3.2. 器件工艺对阈值电压的影响

前述的分析讨论是基于物理模型的,为使本文模型具有一定的实际意义,本小节主要结合图 1 的应变 Si 器件结构以及深亚微米器件中常规的轻掺杂漏区(LDD)、栅极侧墙(spacer)和峰值掺杂(HALO)工艺,简要讨论器件工艺对阈值电压的影响。图 8 为包含上述 3 种工艺的示意图,LDD 结构附近的高浓度 p<sup>+</sup>区即 HALO 区。根据文献[20],LDD 与 HALO 工艺所导致的阈值电压改变可分为两部分:一部分是 LDD 导致的有效沟道长度减小的影响,另一部分是 HALO 区高掺杂的影响,具体表示为

图 8 LDD, spacer 以及 HALO 结构示意图

$$\Delta V_{th} = (\eta - 1) M \exp(-\lambda L_{eff}/2) - N \exp(-\lambda L_{eff}). \quad (27)$$

结合本文的理论模型,上式中的  $\lambda = \sqrt{\alpha}$ ,  $\eta$  和  $M, N$  为如下常数:

$$\eta = \frac{\lambda L_p}{\theta} \sqrt{\frac{\psi_{S,SSi}^{\min}(N_p) - \psi_{S,SSi}^{\min}(N_A) + V_{th}(N_A) - V_{th}(N_p)}{V_{DS}}};$$

$$M = 2 \sqrt{(V_{bi,SSi} - \psi_{S,SSi}^{\min})(V_{bi,SSi} - \psi_{S,SSi}^{\min} + V_{DS})};$$

$$N = 3(V_{bi,SSi} - \psi_{S,SSi}^{\min}) + V_{DS}.$$

同时将(8)式中的  $V_{bi,SSi}$  修正为

$$V_{bi,SSi} = (kT/q) \ln(N_p N_{D,LDD} / n_{i,SSi}^2).$$

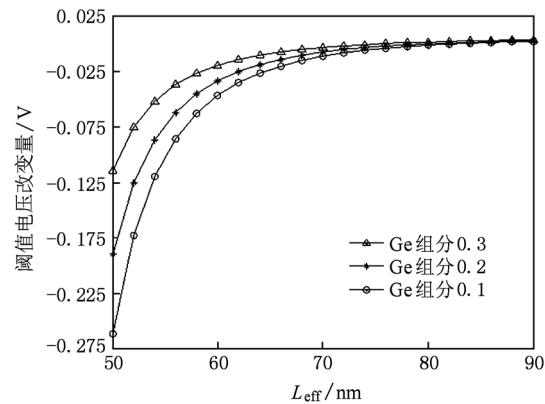

$\theta$  是工艺拟合参数,由具体工艺给定。实际的 HALO 结构是大角度离子注入工艺实现的,其实际浓度分布是关于位置坐标的复杂函数,且注入剂量与注入能量有关,因此(27)式中的  $N_p$  与实际工艺有关,一般取其浓度分布的平均值。不同衬底 Ge 组分下 LDD 与 HALO 工艺所导致的阈值电压改变量的计算结果如图 9 所示,为简单起见,不妨设  $\theta = 1$ 。由图可见,随着有效沟道长度的不断减小,阈值电压的改变量越大,这说明在小尺寸应变 Si/SiGe nMOSFET 中 HALO 工艺也是影响阈值电压的一个因素,且随着衬底 Ge 组分增大,阈值电压改变量随之减小。

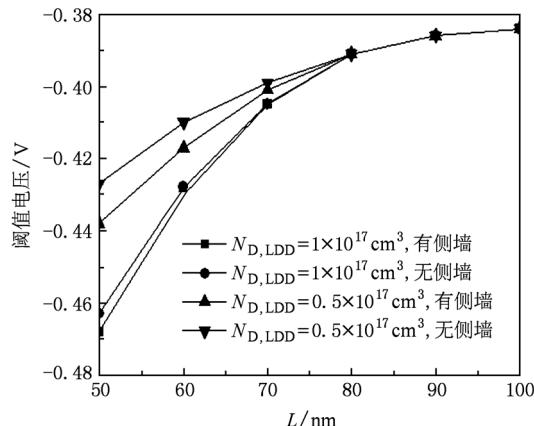

由于栅极侧墙 spacer 中的电力线通常认为是弧形的,建立具体的解析模型需将弧形电力线等效为直线,则必须进行坐标变换,模型较为复杂。限于篇幅,这里仅将其对阈值电压的影响做定性的讨论。使用 ISE TCAD 分别对包含侧墙以及不包含侧墙的应变 Si nMOSFET 结构进行仿真,结果见图 10。因 Ge 组分和沟道掺杂浓度对阈值电压的影响前面已经讨论,图 10 主要讨论侧墙及 LDD 掺杂浓度对阈值电压的影响,Ge 组分取 0.2, 沟道掺杂为 10<sup>18</sup>

图 9 LDD 和 HALO 工艺对阈值电压的影响

$\text{cm}^{-3}$ . 从图中可知, 含有侧墙结构的阈值电压低于无侧墙结构的阈值电压, 二者的差值与侧墙下面的轻掺杂 LDD 区的掺杂浓度  $N_{D,\text{LDD}}$  有关, 且随  $N_{D,\text{LDD}}$  的减小而增大. 当沟道长度约为 80 nm 时, 侧墙结构

对阈值电压几乎没有影响.

#### 4. 结 论

本文针对应变 Si/SiGe nMOSFET 的器件结构, 基于二维泊松方程, 主要对器件的表面势和阈值电压的物理模型进行了研究, 并对阈值电压的理论模型进行了数值计算与分析, 模型计算结果与仿真结果接近, 趋势一致, 证明了该模型的正确性. 基于此, 进一步讨论了器件结构参数以及物理效应对阈值电压的影响. 最后分析讨论了实际深亚微米器件工艺对阈值电压的影响. 应该指出的是, 本文所提出的模型是基于物理的模型, 在此基础上进行数学处理可进一步提高模型的计算精度. 本文模型的推导过程和计算结果为亚 100 nm 的小尺寸应变 Si/SiGe nMOSFET 器件的分析和设计提供了有一定价值的参考.

图 10 侧墙 spacer 对阈值电压的影响

- [1] O'Neil A G, Antoniadis D A 1996 *IEEE Trans. Electron Devices* **43** 911

- [2] Song J J, Zhang H M, Hu H Y, Dai X Y, Xuan R X 2007 *Chin. Phys.* **16** 3827

- [3] Song J J, Zhang H M, Hu H Y, Xuan R X, Dai X Y 2009 *Acta Phys. Sin.* **58** 7947 (in Chinese) [宋建军、张鹤鸣、胡辉勇、宣荣喜、戴显英 2009 物理学报 **58** 7947]

- [4] Wang G Y, Zhang H M, Song J J, Wang X Y, Qin S S, Qu J T 2010 *Acta Phys. Sin.* (in press) [王冠宇、张鹤鸣、宋建军、王晓艳、秦珊珊、屈江涛 2010 物理学报] (已接受)

- [5] Karthik C, Zhou X, Chiah S B 2004 *NSTI-Nanotech* **2** 179

- [6] Tinoco J C, Garcia R, Iñiguez, Cerdeira A, Estrada M 2008 *Semicond. Sci. Tech. nol.* **23** 035017

- [7] Zhang Z F, Zhang H M, Hu H Y, Xuan R X, Song J J 2009 *Acta Phys. Sin.* **58** 4948 (in Chinese) [张志峰、张鹤鸣、胡辉勇、宣荣喜、宋建军 2009 物理学报 **58** 4948]

- [8] Kumar M J, Venkataraman V, Nawal S 2007 *J. Comput. Electron.* **6** 439

- [9] Nayfeh H M, Hoyt J L, Antoniadis D A 2004 *IEEE Trans. Electron Devices* **51** 2069

- [10] Janik T, Majkusiak B 1994 *J. Appl. Phys.* **75** 5186

- [11] Xu J P, Li Y P, Lai P T, Chen W B, Xu S G, Guan J G 2008 *Microelectronics Reliability* **48** 23

- [12] Yang N, Henson W K, Hauser J R, Wortman J J 1999 *IEEE Trans. Electron Devices* **46** 1464

- [13] Stern F 1972 *Phys. Rev. B* **5** 4891

- [14] Zhang W M, Fossum J G 2005 *IEEE Trans. Electron Devices* **52** 263

- [15] Song J J, Zhang H M, Xuan R X, Hu H Y, Dai X Y 2009 *Acta Phys. Sin.* **58** 4958 (in Chinese) [宋建军、张鹤鸣、宣荣喜、胡辉勇、戴显英 2009 物理学报 **58** 4958]

- [16] Suzuki K 2000 *IEEE Trans. Electron Devices* **47** 1202

- [17] Low T, Li M F, Samudra G, Yeo Y C, Zhu C, Chin A, Kwong D L 2005 *IEEE Trans. Electron Devices* **52** 2430

- [18] Xu S L, Xie M X, Zhang Z F 2007 *SiGe Microelectronics Technology* (Beijing: National Defense Industry Press) p269 (in Chinese) [徐世六、谢孟贤、张正璠 2007 SiGe 微电子技术 (北京: 国防工业出版社) 第 269 页]

- [19] Zou X, Xu J P, Li C X, Lai P T, Chen W B 2007 *Microelectronics Reliability* **47** 391

- [20] Yu B, Clement H J, Wann 1997 *IEEE Trans. Electron Devices* **44** 627

# Two-dimensional threshold voltage model of sub-100 nm strained-Si/SiGe nMOSFET\*

Wang Guan-Yu<sup>†</sup> Zhang He-Ming Wang Xiao-Yan Wu Tie-Feng Wang Bin

(Key Laboratory for Wide Band-Gap Semiconductor Materials and Devices, School of Microelectronics, Xidian University, Xi'an 710071, China)

(Received 29 June 2010; revised manuscript received 19 October 2010)

## Abstract

In this paper, based on the two-dimensional (2D) Poisson's equation, an analytical model of threshold voltage, which is applied to a sub-100nm strained-Si/SiGe nMOSFET, is proposed. The secondary effects induced by reducing size such as short-channel effects, quantum mechanical effects are also taken into consideration in order to ensure the accuracy of the model. Then the evidence for the validity of our model is derived from the comparison between analytical results and the simulation data from the 2D device simulator ISE. Finally, the influence of conventional arts in sub-100 nm device fabrication on threshold voltage is also discussed. The proposed model can also be easily used for reasonable analysis and design of sub-100nm strained-Si/SiGe nMOSFET.

**Keywords:** sub-100 nm, strained-Si/SiGe nMOSFET, 2D surface potential, threshold voltage

**PACS:** 71.23. An, 71.70. Fk

\* Project supported by National Ministries and Commissions (Grant Nos. 51308040203, 6139801), the Fundamental Research Funds for the Central Universities (Grant Nos. 72105499, 72104089), and Natural Science Basic Research Plan in Shaanxi Province of China (Grant No. 2010JQ8008).

† E-mail: SiGeBiCMOS@foxmail.com