## 小尺寸应变 Si nMOSFET 物理模型的研究\*

屈江涛<sup>†</sup> 张鹤鸣 秦珊珊 徐小波 王晓艳 胡辉勇 (西安电子科技大学微电子学院,宽禁带半导体材料与器件重点实验室,西安 710071) (2010 年 8 月 23 日收到;2010 年 12 月 13 日收到修改稿)

本文运用高斯定律得出多晶 SiGe 栅应变 Si nMOSFET 的准二维阈值电压模型,并从电流密度方程出发建立了小尺寸应变 Si nMOS 器件的 I-V 特性模型. 对所得模型进行计算分析,得出沟道 Ge 组分、多晶 Si<sub>1-y</sub>Ge<sub>y</sub> 栅 Ge 组分、栅氧化层厚度、应变 Si 层厚度、栅长以及掺杂浓度对阈值电压的影响. 运用二维器件模拟器对器件表面势和 I-V 特性进行了仿真,所得结果与模型仿真结果一致,从而证明了模型的正确性.

关键词:多晶 SiGe 栅,高斯定理,阈值电压,速度过冲

**PACS**: 85.30. – Z, 85.30. De, 85.30. Tv

## 1. 引 言

将硅基应变技术引入 Si 器件和集成电路,利用 Si/SiGe 赝晶生长产生的应变效应来改变材料性质,可显著提高器件中载流子的迁移率<sup>[1]</sup>.由于应变硅技术与 Si 工艺相兼容,具有维系 Si 工艺巨大经济性的优势,所以在高性能小尺寸 MOS 器件设计中被广泛应用<sup>[2-4]</sup>.

近几年,有关应变 Si nMOS 的研究多集中在具 体工艺下器件性能的研究[5,6],且对其阈值电压模 型的建立多是通过求解柏松方程获得的[3,7]. 本文 基于多晶 SiGe 栅应变 Si nMOS 器件物理,通过分析 器件沟道区域的电场分布,运用高斯定理,得到了 器件的准二维阈值电压模型. 同时注意到深亚微米 小尺寸器件速度过冲效应比较显著,而目前的器件 电流模型对应变 Si 的速度过冲效应很少考虑, 目模 型推导主要使用低场下恒定迁移率模型,并多是仿 真优化[3,8],基于此,本文从电荷密度连续性方程出 发,考虑了速度过冲效应,引入与横向电场成函数 关系的迁移率模型,建立了适合小尺寸器件的电学 特性参数模型.通过数学仿真获得了阈值电压随沟 道 Ge 组分、多晶 Si<sub>1-x</sub>Ge<sub>x</sub> 栅 Ge 组分、栅氧化层厚 度、应变 Si 层厚度、栅长以及掺杂浓度的变化规律. 并用二维器件模拟器对器件表面势和 I-V 特性进行 模拟,所得结果与模型仿真结果一致,从而证明了模型的正确性.

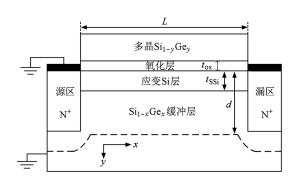

图 1 多晶  $Si_{1-y}Ge_y$  栅应变 Si nMOS 器件结构

## 2. 物理模型的研究

多晶  $Si_{1-y}Ge_y$  栅应变 Si nMOS 器件结构如图 1 所示. 器件采用倒掺杂分布,即  $N_{ch} < N_b$ ,较低的沟道区掺杂  $N_{ch}$  能减少离化杂质散射,另外虚拟衬底中掺杂较高,所以耗尽层只扩展到虚拟衬底中,而下面的 Ge 组分渐变 SiGe 缓冲层对阈值电压和电学特性没有影响,因此图 1 只表示出沟道和虚拟衬底部分. 一般应变 Si nMOS 器件多以多晶 Si 做栅,而本文采用了多晶  $Si_{1-y}Ge_y$  栅. 与多晶 Si 栅相比,多晶  $Si_{1-y}Ge_y$  栅既可抑制栅耗尽效应,提高栅氧化层

<sup>\*</sup>国家部委项目(批准号:51308040203,9140A08060407DZ0103,6139801)资助的课题.

<sup>†</sup> E-mail:taoq716@ foxmail.com

的可靠性<sup>[9,10]</sup>,同时随 Ge 组分的不同其功函数有较 宽的变化范围,利于调节器件的阈值电压<sup>[9,11]</sup>.

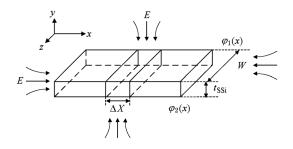

图 2 应变 Si 沟道电场分布

#### 2.1. 准二维表面势模型

高斯定理指出穿过任何闭合曲面的电通量等 于该闭合曲面所包围的净电荷,即

$$\oint_{s} E(x) \, \mathrm{d}s = \frac{q}{\varepsilon_0}. \tag{1}$$

应变 Si nMOS 的沟道电场分布情况如图 2 所示. 由图可知,应变 Si 沟道区仅受 x 和 y 方向电场的影响,而 z 方向没有电场. 图中  $\varphi_1(x)$  为 SiO<sub>2</sub>/SSi 界面电势,  $\varphi_2(x)$  为 SSi/SiGe 界面电势,  $t_{SSi}$  为沟道厚度,W 为沟道宽度. 理想条件下,应用耗尽近似,假设应变 Si 层均匀掺杂且完全耗尽,氧化层中没有杂质电荷,则根据高斯定理,x 方向和 y 方向四个面的电通量之和等于  $\Delta X$  沟道长度内电荷量,即可得到

$$\varepsilon_{\rm SSi} t_{\rm SSi} \frac{\partial E_1(x)}{\partial x} + \varepsilon_{\rm ox} \frac{V_{\rm G} - \varphi_1(x)}{t_{\rm ox}} - \varepsilon_{\rm SiGe} \frac{\varphi_2(x)}{d - t_{\rm csi}} = q N_{\rm ch} t_{\rm SSi}, \qquad (2)$$

式中, $E_1(x)$  为  $SiO_2/SSi$  界面电场、 $N_{ch}$  为沟道区掺杂浓度,d 为强反型耗尽层宽度, $\varepsilon_{ssi}$  为应变 Si 介电常数, $\varepsilon_{ox}$  为栅氧化层介电常数, $\varepsilon_{SiGe}$  为弛豫 SiGe 介电常数, $t_{ox}$  为栅氧化层厚度, $V_G = V_{GS} - V_{FB}$  为有效栅压. 等式左边三项分别表示了从x 方向进入沟道的电通量、从应变 Si 上表面进入的电通量、从应变 Si 下表面进入的电通量。通过求解一维柏松方程可得最大耗尽层厚度

$$d = k \left[ \frac{2\varepsilon_{\text{SiGe}}}{qN_{\text{B}}} (\Delta \varphi + \varphi_{\text{s}}) \right]^{1/2}, \tag{3}$$

式中 $k = [1 - 2\exp(-L/\lambda_d)]$  为短沟道因子<sup>[12]</sup>,  $\lambda_d = \delta(W_s + W_d)$ ,  $W_s$  和  $W_d$  分别为源漏耗尽宽度,  $\delta =$

$$0.65, W_{\rm s} \approx W_{\rm d} \approx \sqrt{\frac{2\varepsilon_{\rm Si}}{q} \frac{N_{\rm D}}{N_{\rm B}} \left(\frac{V_{\rm bi,Si}}{N_{\rm D} + N_{\rm B}}\right)}. \ \ \vec{\Xi} \ \dot{\Psi}, \ N_{\rm D},$$

$N_{\rm B}$  分别为源漏掺杂和衬底掺杂, $V_{\rm bi,Si}$  为源极与沟道区间的自建电势.  $\varphi_{\rm s}$  为应变 Si 强反型时的表面势. 因为沟道设计很薄,所以需要考虑到 Si/SiGe 界面电势的影响,因此  $\varphi_{\rm s}$  可认为是 SiO<sub>2</sub>/SSi 与 SSi/SiGe 界面电势的平均值 [13],即

$$\varphi_{s} = \frac{kT}{q} \left[ \ln \left( \frac{N_{ch}}{n_{i,ssi}} \right) + \ln \left( \frac{N_{B}}{n_{i,SiGe}} \right) \right] - \left( \frac{\Delta E_{v} + \Delta E_{c}}{2q} \right), \tag{4}$$

式中,  $n_{i,ssi}$  为应变 Si 本征载流子浓度,  $n_{i,siGe}$  为弛豫 SiGe 本征载流子浓度,  $\Delta E_v$ ,  $\Delta E_e$  分别为价带差和导带差. 因为  $d \geq t_{ssi}$  则

$$\varphi_2(x) = \frac{1}{2} \frac{q N_{\rm B}}{\varepsilon_{\rm SiCo}} d^2.$$

(5)

将(3)式代入(5)式可得

$$\varphi_{2}(x) = k^{2} (\Delta \varphi + \varphi_{1}(x))$$

$$= k^{2} \left[ \varphi_{1}(x) + t_{SSi}^{2} \left( \frac{qN_{B}}{\varepsilon_{Si}} - \frac{qN_{ch}}{2\varepsilon_{Si}} - \frac{qN_{B}}{2\varepsilon_{SiGe}} \right) \right]. \quad (6)$$

将(6)式代入(2)式整理可得关于 $\varphi_1(x)$ 的二阶非 齐次微分方程

$$\frac{\partial^2 \varphi_1(x)}{\partial x^2} - \alpha^2 \varphi_1(x) = \beta, \tag{7}$$

式中

$$\begin{split} \alpha^2 &= \frac{C_{\text{ox}} + C_{\text{SiGe}} k^2}{\varepsilon_{\text{Si}} t_{\text{SSi}}}, \\ \beta &= \frac{q N_{\text{ch}}}{C_{\text{SSi}} t_{\text{SSi}}} + \frac{C_{\text{SiGe}} k^2 \Delta \varphi - C_{\text{ox}} V_{\text{G}}}{C_{\text{SSi}} t_{\text{SSi}}^2} \\ C_{\text{SiGe}} &= \frac{\varepsilon_{\text{SiGe}}}{d - t_{\text{SSi}}}, \\ C_{\text{ox}} &= \frac{\varepsilon_{\text{ox}}}{t_{\text{ox}}}, \\ C_{\text{SSi}} &= \frac{\varepsilon_{\text{Si}}}{t_{\text{SSi}}}. \end{split}$$

(7)式的通解可表示为

$arphi_1(x) = C_1 \exp(\alpha x) + C_2 \exp(-\alpha x) + \sigma$ . (8) 利用漏源区电势边界条件  $arphi_1(0) = V_{\rm bi}$  和  $arphi_1(L) = V_{\rm bi} + V_{\rm DS}$  对上式进行求解可得

$$\begin{split} C_1 &= \frac{(V_{\text{bi}} + V_{\text{DS}} - \sigma) - (V_{\text{bi}} - \sigma) \exp(-L\alpha)}{\exp(L\alpha) - \exp(-L\alpha)} \\ C_2 &= \frac{(V_{\text{bi}} + V_{\text{DS}} - \sigma) - (V_{\text{bi}} - \sigma) \exp(L\alpha)}{\exp(-L\alpha) - \exp(L\alpha)} \\ \sigma &= -\beta/\alpha^2 \,, \end{split}$$

式中,考虑到应变的影响,源极与沟道区间的自建 电势  $V_{\text{bi}}$  可表示为

$$\begin{split} V_{\text{bi,SSi}} &= V_{\text{bi,Si}} + \Delta V_{\text{bi}} \\ &= \frac{E_{\text{g,Si}}}{2q} + \frac{kT}{q} \ln \left( \frac{N_{\text{ch}}}{n_{\text{i,Si}}} \right) \\ &- \frac{\Delta E_{\text{g,SSi}}}{q} + \frac{kT}{q} \ln \left( \frac{N_{\text{V,Si}}}{N_{\text{V,SSi}}} \right), \end{split} \tag{9}$$

式中  $\Delta E_{g.SSi}$  为应变引起的能带减小量.

在平带条件下,由于较大的价带差 $\Delta E_{x}$ 的存在, 体内的空穴在 Si/SiGe 界面处积累形成了偶极层, 使界面处能带弯曲,从而影响了平带电压. 应变 Si 层很薄,需计入偶极层的影响.利用高斯定理,可以 得到偶极层的电势  $\phi_{\text{dipole}}$  [14] 为

$$\phi_{\text{dipole}} = \frac{qN_{\text{ch}}t_{\text{Si}}}{2\varepsilon_{\text{SSi}}}(\sqrt{2}L_{\text{d}} + t_{\text{SSi}}), \qquad (10)$$

式中, $L_a$  为德拜长度,其值为

$$L_{\rm d}=\sqrt{arepsilon_{

m SiCe}kT/q^2N_{

m B}}.$$

这样,将栅极区域的平带电压  $V_{

m FB}$  修正如下:

$$\begin{split} V_{\rm FB} &= \varphi_{\rm Poly \, SiGe} \, - \, \left( \left( \chi_{\rm SiGe} \, + \, \frac{\Delta E_{\rm C}}{2 \, q} \right) \right. \\ &\left. + \left( \frac{E_{\rm g, SSi}}{2} \, \frac{kT}{q} \ln \! \left( \frac{N_{\rm ch}}{n_{\rm i, ssi}} \right) \right) \right) \, - \, \phi_{\rm dipole} \,, \end{split} \tag{11}$$

式中,  $\phi_{\text{Poly SiGe}}$  为多晶 SiGe 栅的功函数,  $\chi_{\text{SiGe}}$  为弛豫 SiGe 的亲合势,  $E_{g,SSi}$  为应变 Si 的禁带宽度,为了求 阈值电压模型,须求得(8)式的最小值,令  $\frac{\partial \varphi_1(x)}{\partial x}$ = 0. 可以求得

$$\varphi_{\rm SSi,min} = 2 \sqrt{C_1 C_2} + \sigma. \tag{12}$$

此时的表面势  $\varphi_{\mathrm{SSi.min}}$  即为刚达到强反型时沟道阈值 表面势 $\varphi_s$ , 即 $\varphi_{SSi,min} = \varphi_s$ , 进一步求解,则此时的栅 源电压  $V_{\rm cs}$  即为器件的阈值电压  $V_{\rm th}$ ,表达式为

$$V_{\text{thl}} = \frac{\alpha^{2} \varphi_{s} (\exp(\alpha L) + 1)^{2} + \gamma (\exp(\alpha L) - 1)^{2} - 4\alpha V_{\text{bi,SSi}} \exp(\alpha L) + \eta V_{\text{FB}} (\exp(\alpha L) - 1)^{2}}{(\exp(\alpha L) - 1)^{2} \eta} - \frac{2\alpha V_{\text{DS}} \exp(\alpha L) + 2\alpha \exp(\alpha L) (1 + \exp(\alpha L)) \sqrt{(\varphi_{s} - V_{\text{bi,SSi}})^{2} - (\varphi_{s} - V_{\text{bi,SSi}}) V_{\text{DS}}}}{(\exp(\alpha L) - 1)^{2} \eta},$$

(13)

其中

$$\begin{split} \gamma &= \frac{q N_{\rm ch}}{\varepsilon_{\rm Si}} + \frac{C_{\rm SiGe} k^2 \Delta \varphi}{C_{\rm SSi} t_{\rm SSi}^2}, \\ \eta &= \frac{C_{\rm ox}}{C_{\rm SSi} t_{\rm SSi}^2}. \end{split}$$

对于小尺寸器件,随着源漏压降的升高,DIBL效应 引起的阈值电压偏移不能忽略,因此必须对(13)式 进行修正

$$V_{\rm th} = V_{\rm th1} - \mu V_{\rm ds}$$

式中 $\mu$ 为 DIBL 因子<sup>[15]</sup>,可表示为 $\mu = \frac{\varepsilon_0 \varepsilon_{\text{ssi}}}{\pi C L}$

#### 2. 2. I-V 电流电压特性模型

对于小尺寸器件,由于沟道长度与载流子平均 自由程同量级或小于平均自由程,沟道载流子不会 遭受散射,因此形成速度过冲,这时速度过冲效应 所引起的电流增大不能忽略,因此可由  $I = (W_{t_{si}})J$ 可得 nMOSFET 的沟道电流方程

$$I = Wt_{ssi}J = Wt_{ssi} \left[ q\mu_n n(x) E(x) \right]$$

$$+q\mu_n n(x)\delta(E)\frac{\mathrm{d}E(x)}{\mathrm{d}x}$$

, (14)

式中  $\delta(E) \approx \frac{2}{3} v_{\text{sat}} \tau_{\text{W}}$  为能量弛豫长度 [16],  $v_{\text{sat}}$  为饱 和速度,  $\tau_w$  为能量弛豫时间,其值随 Ge 组分的变化 详见文献[17]. 电子局限在表面的量子阱沟道中, 其浓度为

$n(x) = C_{ox}(V_{GS} - V_{th} - V(x))/qt_{ssi},$  (15) V(x) 为沿沟道方向的电压降. W 为沟道宽度,而强 场下沿沟道方向的μ, 为

$$\mu_n = \mu_0 \left( 1 + \frac{\mu_0}{2\nu_{\text{sal}}} E(x) \right)^{-1},$$

(16)

式中 $\mu_0$ 为低场迁移率,采用文献[18]中的模型.发 生速度过冲时有  $\frac{dE(x)}{dx} = \theta \frac{V_{DS}}{I^2}$  [19],  $\theta$  为与工艺有 关的参数,其值约为 0. 2. 同时将  $E(x) = \frac{\mathrm{d}V(x)}{\mathrm{d}x}$  代

入到(14)式中并整理,并对x从0到L积分,对 V(x) 从 0 到  $V_{\rm DS}$  积分,从而得到沟道电流  $I_{\rm DS}$  的 表达式.

#### 1) 非饱和区

$$I_{\text{DS}} = \frac{W\mu_{\text{eff}} C_{\text{ox}}}{L \left( 1 + \frac{\mu_{\text{eff}} V_{\text{DS}}}{2\nu_{\text{sat}}} \right)}$$

$$\times \left( \left( \left( V_{\text{GS}} - V_{\text{th}} \right) V_{\text{DS}} - \frac{V_{\text{DS}}^2}{2} \right)$$

$$\times \left( 1 + \frac{\theta \delta(E)}{L} \right) + \frac{\theta^2 \delta(E)}{12L} V_{\text{DS}}^2 \right). \quad (17)$$

#### 2)饱和区

$$I_{DS} = \frac{W\mu_{\text{eff}}C_{\text{ox}}}{L\left(1 + \frac{\mu_{\text{eff}}(V_{\text{GS}} - V_{\text{th}})}{2\nu_{\text{sat}}}\right)} \times \left(\frac{1}{2}(V_{\text{GS}} - V_{\text{th}})^{2}\left(1 + \frac{\theta\delta(E)}{L}\right) + \frac{\theta^{2}\delta(E)}{12L}(V_{\text{GS}} - V_{\text{th}})^{2}\right).$$

(18)

### 3. 仿真分析与讨论

运用 Matlab 对模型进行仿真. 如未做特殊说明,基本参数选取如下:

$t_{\rm ssi} = 10 \text{ nm}, t_{\rm ox} = 5 \text{ nm}, N_{\rm ch} = 10^{16} \text{ cm}^{-3}, N_{\rm b} = 10^{17} \text{ cm}^{-3},$ 多晶 SiGe 栅 Ge 组分 y = 0.4,沟道 SiGe 区 Ge 组分 x = 0.3,栅长 L = 150 nm.

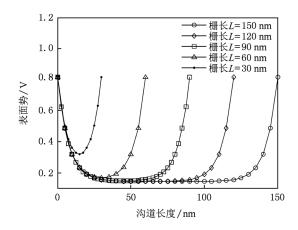

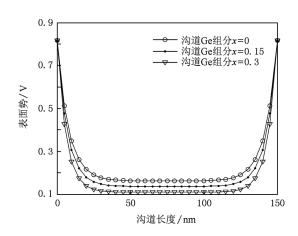

图 3 为不同栅长情况下,沿沟道方向表面电势的分布情况,其中源漏电压和栅压都为 0. 从图中可以看出,随着沟道长度的缩短,沟道表面势逐渐增大,即源端的势垒高度减小,这与体硅器件中沟道长度对表面势的影响一致. 如图 4 所示,随着 Ge 组分的提高,应变 Si 层应力增加,则禁带宽度减小,本征载流子浓度提高,沟道表面势则降低,而源端势垒高度增加.

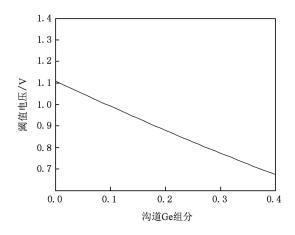

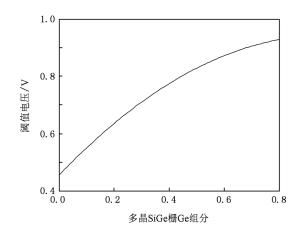

图 5 显示了沟道 Ge 组分对阈值电压的影响. 随着 Ge 组分的增加,应变 Si 导带进一步下降,从而提高了沟道内二维电子气的面密度,因此阈值电压降低. 图 6 为多晶 SiGe 栅 Ge 组分对阈值电压的影响,从图中可以看出阈值电压随着多晶 SiGe 栅 Ge 组分的增加而提高,这是由于多晶 SiGe 栅随着 Ge 组分的增大其功函数降低,使平带电压  $V_{FB}$  降低,则阈值电压升高. 从图 6 中可以看出 Ge 组分从 0 到 1 阈值电压变化幅度约 0.5 V. 可见多晶 SiGe 栅对阈值电压有着优异的调控作用.

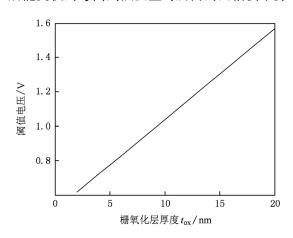

图 7 显示了栅氧化层厚度对阈值电压的影响. 从图中可以看出,随着栅氧化层厚度的增加,阈值电压提高.这是由于栅氧厚度的增加使栅极对沟道

图 3 不同沟道长度下的沟道表面势

图 4 不同 Ge 组分下的沟道表面势

图 5 沟道 Ge 组分对阈值电压的影响

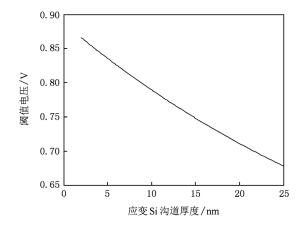

的控能力减弱,因此在器件的设计当中,保证器件可靠性的同时应尽量降低栅氧化层的厚度,以提高栅极对沟道的控制能力. 应变 Si 层厚度对阈值电压的影响如图 8 所示,阈值电压随沟道厚度的增加而

图 6 多晶 SiGe 栅 Ge 组分对阈值电压的影响

降低,这是由于较厚的应变 Si 做沟道,在栅极加电压后能更快的弯曲到强反型时所需的两倍费米势.

图 7 栅氧化层厚度对阈值电压的影响

图 8 应变 Si 层厚度对阈值电压的影响

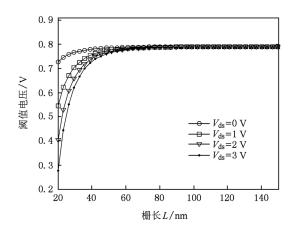

图 9 不同栅长下漏源电压对阈值电压的影响. 从图中可以看出,当栅长小于 60 nm 时,阈值电压随 栅长的减小而迅速降低,栅长不变的情况下,随源漏电压的增加而减小.而这种现象在栅长大于 60 nm 时变化不明显.该现象是由于漏致势垒降低(DIBL)的短沟道效应对阈值电压造成影响的结果.

图 9 不同栅长下漏源电压对阈值电压的影响

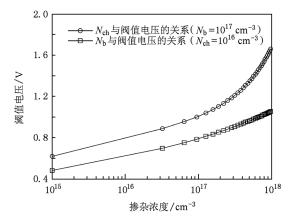

图 10 为掺杂浓度与阈值电压的关系. 图中两条曲线,一条表示了衬底掺杂浓度  $N_b$  =  $10^{17}$  cm<sup>-3</sup> 时,沟道掺杂浓度与阈值电压的关系;另一条表示了沟道掺杂浓度为  $N_{ch}$  =  $10^{16}$  cm<sup>-3</sup> 时,衬底掺杂浓度与阈值电压的关系. 从图中可以看出两种掺杂浓度与阈值电压的关系. 从图中可以看出两种掺杂浓度的提高都使阈值电压升高. 当沟道掺杂浓度  $N_{ch}$  小于 $10^{17}$ 时,阈值电压变化较慢,这是因为较低的沟道掺杂浓度  $N_{ch}$  很容易完全耗尽,因此对阈值电压的影响很小. 当  $N_{ch}$  大于  $10^{17}$ 时,阈值电压变化幅度增大,这是因为随着  $N_{ch}$  的提高,沟道需要更高的栅压才能完全耗尽,同时沟道达到强反型时所需的费米势提高,沟道掺杂浓度的提高造成沟道内反型载流子面密度的减小,使阈值电压提高,而衬底掺杂浓度对应变 Si nMOS 阈值电压的影响规律与其对体硅器

图 10 掺杂浓度对阈值电压的影响

件阈值电压的影响变化规律一致.

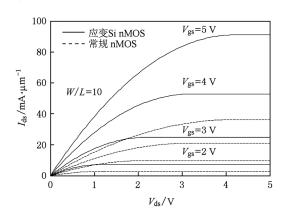

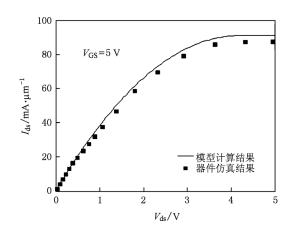

图 11 应变 Si nMOSFET 的 I-V 特性

图 11 为应变 Si NMOSFET 的 I-V 特性. 由图 11 仿真结构可知,源漏电流随着栅压的增大而提高,当  $V_{\rm gs}$  = 5 V 时应变 Si nMOS 的饱和漏电流为 90mA,相同条件下的常规器件饱和漏电流为 40mA,由于硅基应变技术使器件电子迁移率大幅度提高,所以其性能比常规体 Si 器件性能提高了 2 倍多,可见在相同栅压下,应变 Si nMOS 比常规 nMOS 拥有更高的电流驱动能力.

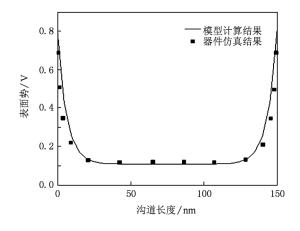

图 12 Ge 组分为 0.3 时沟道表面势分布

图 13 应变 Si NMOSFET 的 I-V 特性

为了验证模型的正确性,采用二维器件模拟器 ATLAS 对多晶 SiGe 栅应变 Si nMOS 器件进行仿真, 所得结果与 MATLAB 数值计算所得结果进行比对, 如图 12、图 13 所示. 图中黑心方框为器件模拟器 ATLAS 模拟出的结果,线条为模型计算结果. 从图中可看出计算结果与仿真结果基本符合,从而证明了模型的正确性.

## 4. 结 论

本文基于物理原理,对多晶 SiGe 栅应变 Si nMOS 沟道区的电通量进行了分析,运用高斯定理得出器件的准二维阈值电压模型.考虑到短沟道器件的速度过冲效应,建立了非恒定迁移率下的电流电压电学特性模型.通过数值计算获得阈值电压随沟道 Ge 组分、多晶 Si<sub>1-y</sub>Ge<sub>y</sub> 栅 Ge 组分、栅氧化层厚度、应变 Si 层厚度、栅长及掺杂浓度的变化规律,并利用器件仿真软件 ATLAS 对器件进行仿真,所得结果与模型仿真结果一致,从而证明了模型的正确性.

<sup>[1]</sup> Currie M T 2004 IEEE International Conference on Integrated Circuit Design and Technology 2004 p261

<sup>[2]</sup> Song J J, Zhang H M, Dai X Y, Hu H Y, Xuan R X 2008 Acta Phys. Sin. **57** 5918 (in Chinese) [宋建军、张鹤鸣、戴显英、胡辉勇、宣荣喜 2008 物理学报 **57** 5918]

<sup>[3]</sup> Zhang H M, Cui X Y, Hu H Y, Dai X Y, Xuan R X 2007 Acta Phys. Sin. **56** 5052(in Chinese) [张鹤鸣、崔晓英、胡辉勇、戴 显英、宣荣喜 2007 物理学报 **56** 5052]

<sup>[4]</sup> Song J J, Zhang H M, Hu H Y, Dai X Y, Xuan R X 2007 Chin. Phys. 16 3827

<sup>[5]</sup> Driussi F, Esseni D, Selmi L, Hellstrom P E 2008 Solide-State Electronics 52 498

<sup>[6]</sup> Hartmann J M, Abbadie A, Rouchon D, Barnes J P 2008 Thin Solid Films 516 4238

<sup>[7]</sup> Zhang Z F, Zhang H M, Hu H Y, Xuan R X, Song J J 2009

\*\*Acta Phys. Sin. 58 4948 (in Chinese) [张志锋、张鹤鸣、胡辉

- 勇、宣荣喜、宋建军 2009 物理学报 58 4948]

- [8] Gao Y, Sun L W, Yang Y, Liu J 2008 Journal of Semiconductors 29 338 (in Chinese)[高 勇、孙立伟、杨 媛、刘 静 2008 半导体学报 29 338]

- [9] Ponomarev Y V 1997 IEDM p829

- [10] Lee W C, Watson B, King T J, Hu C M 1999 IEEE Electron Devices Lett. 20 232

- [11] King T J, McVittie J P, Saraswat K C, Pfiester J R 1994 IEEE Trans. Electron Devices 41 228

- [12] Kunihiro Suzuki 2000 IEEE Trans. Electron Devices 47 2372

- [13] Nayfeh H M, Hoyt J L, Dimitri A A 2004 IEEE Trans. Electron

- Devices 51 2069

- [14] Nayfeh H M, Hoyt J L, Dimitri A A 2004 IEEE Trans. on Electron Devices 51 2069

- [15] Arora ND 1989 Advanced Device Physics (New York: Academic Press Inc)

- [16] Price P J 1988 Journal of Applied Physics 63 4718

- [17] Rim K, Hoyt J L, Gibbons J F 2000 IEEE Trans. on Electron Devices 47 1406

- [18] Ismail K, Nelson S F 1993 Applied Physics Letter 63 660

- [19] Roldán J B, Gámiz F, López V 1997 IEEE Trans. on Electron Devices 44 841

# Study of physically modeling for small-scaled strained Si nMOSFET\*

Qu Jiang-Tao<sup>†</sup> Zhang He-Ming Qin Shan-Shan Xu Xiao-Bo Wang Xiao-Yan Hu Hui-Yong

(Key Lab of Wide Band-Gap Semiconductor Materials and Devices, School of Microelectronics, Xidian University, Xi'an 710071, China)

(Received 23 August 2010; revised manuscript received 13 December 2010)

#### Abstract

In this paper, quasi-2D threshold voltage model of strained Si nMOS with polycrystalline SiGe gate is established based on the Guass Law and its *I-V* character model is also built based on the current density equation. The influence of relevant parameter on threshold voltage is analyzed by numerical analysis, and the validity of the model is verified by device simulator.

**Keywords:** polycrystalline SiGe gate, Gauss law, threshold voltage, velocity overshoot effect **PACS:** 85.30.-Z, 85.30. De, 85.30. Tv

<sup>\*</sup> Project supported by the National Ministries and Commissions (Nos. 51308040203, 9140A08060407DZ0103, 6139801).

<sup>†</sup> E-mail: taoq716@ foxmail. com