# 考虑量子效应的高 k 栅介质 SOI MOSFET 特性研究 $^*$

# 曹磊† 刘红侠

(西安电子科技大学微电子学院, 宽禁带半导体材料与器件教育部重点实验室, 西安 710071)

(2012年6月11日收到; 2012年7月16日收到修改稿)

本文主要研究考虑量子效应的高 k 栅介质 SOI MOSFET 器件特性. 通过数值方法自治求解薛定谔方程和泊松方程,得到了垂直于 SiO $_2$ /Si 界面方向上载流子波函数及能级的分布情况,结合 Young 模型,在考虑短沟道效应和高 k 栅介质的情况下,对 SOI MOSFET 的阈值电压进行模拟分析. 结果表明:随着纵向电场的增加,量子化效应致使反型层载流子分布偏离表面越来越严重,造成了有效栅氧化层厚度的增加和阈值电压波动. 采用高 k 栅介质材料,可以减小阈值电压,抑制 DIBL 效应. 较快的运算速度保证了模拟分析的效率,计算结果和 ISE 仿真结果的符合说明了本文的模型精度高.

关键词: 量子化效应, 高 k 材料, SOI MOSFET, 阈值电压

PACS: 73.40.Qv, 73.40.Lq, 12.39.Pn

# 1 引言

随着 CMOS 技术进入纳米尺度, 器件在等比例 缩小技术方面的不断进步和巨大成功,集成电路才 有了今天的辉煌成就. 近几年, 已有一些文章报道 了小于 100 nm 的 MOS 器件的研究和制作, 65 nm, 45 nm 乃至 30 nm CMOS 都已经投入了生产使用. 但是器件尺寸的进一步缩小, 已经接近其物理极 限, 许多小尺寸效应的研究刻不容缓 [1-3]. 为了保 证栅对沟道电荷的控制力,抑制短沟道效应,通常 要求栅氧化层厚度随沟道长度的缩小而减小,同时 希望沟道的掺杂浓度不断提高,这些变化将使垂直 于  $Si/SiO_2$  界面方向的电场增加, Si 中界面附近的 势阱加深,沟道反型层中的载流子被约束在表面很 窄的势阱中, 载流子沿垂直于表面方向的运动时量 子化, 研究表明, 这一现象对器件的性能, 特别是阈 值电压有很大的影响 [4-7]. Wirth 等发现沟道长度 为 30 nm 的 MOS 晶体管的  $I_{\rm d}$ - $V_{\rm g}$  特征曲线出现了 振荡,产生振荡的原因是沟道电子的量子化效应和

库仑阻塞效应 <sup>[8]</sup>,传统 CMOS 结构将被 SOI 等新结构器件或者纳电子器件所代替,这是一个必然的发展趋势. 同时,在 MOS 器件尺寸等比缩小进程中,电源电压并没有按相同比例同步减小,这使得器件内部电场增强. 当 MOS 器件栅介质厚度下降到 2 nm 左右时,栅极泄漏电流增加,器件无法正常工作. 因此,高 k 栅介质已是一个非常热门的研究课题 <sup>[9,10]</sup>.

# 2 泊松方程和薛定谔方程自洽求解

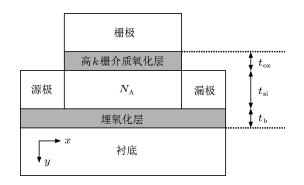

高 k 栅介质 SOI MOSFET 器件的剖面结构示意图如图 1 所示. 图中高 k 栅介质的厚度为  $t_{ox}$ ,沟道的厚度为  $t_{si}$ ,埋氧化层的厚度为  $t_{b}$ ,沟道长度为 L,沟道的掺杂浓度为  $N_{A}$ .

为了满足计算模型的普适性, 计算过程采用载流子费米统计和掺杂浓度的部分电离模型 [11]. 根据泊松方程有

$$\frac{dV^2}{dy^2} = -\frac{q}{\varepsilon} (N_{\rm d}^+ - N_{\rm a}^- + p - n),$$

(1)

† E-mail: cao0273@sina.com

© 2012 中国物理学会 Chinese Physical Society

http://wulixb.iphy.ac.cn

<sup>\*</sup>国家自然科学基金 (批准号: 61076097, 60936005), 教育部科技创新工程重大项目培育资金 (批准号: 708083) 和中央高校基本科研业务费 专项资金 (批准号: 20110203110012) 资助的课题.

其中 V 为沿器件 y 方向的电势, q 为电荷电量,  $\varepsilon$  为介电常数, 电势与导带底和价带顶能量之间的关系如下:

$$E_{\rm c} = -qV, \tag{2}$$

$$E_{\rm v} = -qV - E_{\rm g},\tag{3}$$

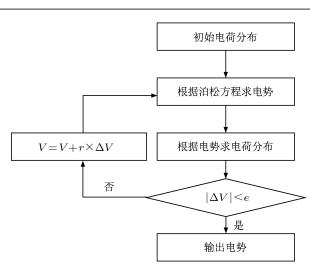

其中  $E_g$  为禁带宽度. 在器件内部, 电荷分布决定电势分布, 而电势分布反过来又影响电荷分布, 因此, 器件结构中的电势分布可以通过载流子统计分布与泊松方程的自治求解求得, 计算过程如图 2 所示.

图中的 r 为电势增量的松弛因子, 实际计算过

程中,r 的取值从 0.001 开始不断缓慢增大,从而实现其优化. 电势差的判别值 e 对载流子浓度的精度影响很大,通常取  $10^{-6}$  eV 即可. 在使用泊松方程求解电势的过程中,本文采用了有限差分法将其化成差分数值方程

$$\frac{V_{i+1} - 2V_i + V_{i-1}}{h^2} = -\frac{\rho(i)}{\varepsilon},\tag{4}$$

其中,  $V_i$  表示第 i 个格点的电势值,  $\rho_i$  表示第 i 个格点的电荷浓度, h 表示格点之间的距离, 则泊松方程化为各点上的线性方程

$$\begin{bmatrix} -2 & 1 & & & & & \\ 1 & -2 & 1 & & & & \\ & 1 & -2 & 1 & & & \\ & & & 1 & -2 & 1 \\ & & & & 1 & -2 \end{bmatrix} \begin{bmatrix} V_2 \\ V_3 \\ V_4 \\ \dots \\ V_{n-2} \\ V_{N-1} \end{bmatrix} = \frac{1}{\varepsilon} \begin{bmatrix} \rho_2 \\ \rho_3 \\ \rho_4 \\ \dots \\ \rho_{n-2} \\ \rho_{n-1} \end{bmatrix} - \begin{bmatrix} V_1 \\ 0 \\ 0 \\ \dots \\ 0 \\ V_n \end{bmatrix}.$$

(5)

方程组右边第二项中  $V_1$  和  $V_n$  分别表示栅电压和衬底电压.

图 1 高 k 栅 SOI MOSFET 结构示意图

在栅介质和沟道的交界处,因为量子化效应的存在,限制了电子在垂直于界面方向的自由运动.因此,在计算时必须引入薛定谔方程来求解,垂直于界面方向的导带底势阱对电子的量子限制可以用有效质量近似下的薛定谔方程描述:

$$-\frac{\hbar^2}{2}\frac{\mathrm{d}}{\mathrm{d}y}\left[\frac{1}{m^*(y)}\frac{\mathrm{d}}{\mathrm{d}z}\psi(y)\right] + E_{\mathrm{C}}(y)\psi(y)$$

$$=E\psi(y), \tag{6}$$

其中,  $m^*$  为电子的有效质量,  $\psi$  为二维电子气的波函数, E 为量子化能级,  $E_{\rm C}$  为导带底能量.

图 2 SOI MOSFET 沟道电势计算流程

同样的道理,对于薛定谔方程,需要将二阶微分表达式转换为差分格式,本文采用等间距离散,格点间距为 $\Delta h$ ,则薛定谔可转化为

$$-\frac{\hbar^{2}}{2\Delta h^{2}} \frac{1}{m_{i+1/2}^{*}} \psi_{i+1} + \left(\frac{\hbar^{2}}{2\Delta h^{2}}\right) \times \left(\frac{1}{m_{i+1/2}^{*}} + \frac{1}{m_{i-1/2}^{*}}\right) + E_{C}^{i} \psi_{i}$$

$$-\frac{\hbar^{2}}{2\Delta h^{2}} \frac{1}{m_{i-1/2}^{*}} \psi_{i-1} = E\psi_{i},$$

(7)

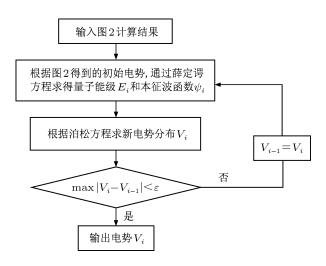

其中,  $m_{i+1/2}^*$  为电子有效质量在第i 个点和第i+1 个点的平均值. 同时运用 MATLAB 计算软件中的 eig 函数可以求解矩阵本征值和本征函数, 泊松 方程和薛定谔方程的自治求解如图 3 所示.

图 3 自治求解薛定谔 - 泊松方程流程图

计算经验表明, 图 2 的计算结果误差越小, 薛定谔-泊松方程的迭代次数越少, 计算时间越短, 通常初始电势的误差要小于  $10^{-10}$  eV. 图中的  $\varepsilon$  为电势误差的判别值.

#### 3 考虑量子效应的阈值电压

在考虑量子化效应后,反型层电子浓度的最大值出现在半导体沟道内,使得载流子与界面的平均距离较经典的情况下相差  $\Delta y$ ,电场会在  $\Delta y$  上产生额外压降  $\Delta \phi_s^{\rm QM}$ ,且有效氧化层厚度变为  $t_{\rm ox}+\varepsilon_{\rm ox}\times\Delta y/\varepsilon_{\rm si}$ ,当栅氧化层非常薄时, $\Delta y$  对氧化层电容的影响非常显著,此差值可以表示为 [12]

$$\Delta y = \left(\frac{9h^2}{16\pi^2 qm^* E_{\text{eff}}}\right)^{1/3} - \frac{3KT}{2qE_{\text{eff}}}, \quad (8)$$

其中  $E_{\rm eff}$  为反型沟道纵向有效电场. 因此, 阈值表面势由经典情况的  $\phi_{\rm sTH}$  变为考虑量子效应的

$$\phi_{\text{sTH}} = 2\phi_{\text{f}} + \Delta\phi_{\text{s}}^{\text{QM}}, \tag{9}$$

根据 QM 模型, 要使表面反型层载流子电荷面密度  $Q^{\mathrm{QM}}$  达到和经典模型得到的强反型时反型载流子面密度  $Q^{\mathrm{CL}}$  同样的值, 则要加上  $\Delta\phi_{\mathrm{s}}^{\mathrm{QM}}$ , 可以将这种差异表达为

$$\Delta \phi_{\rm s}^{\rm QM} = \frac{K_0 T}{q} \ln \left( \frac{Q^{\rm CL}}{Q^{\rm QM}} \right). \tag{10}$$

因此, 考虑量子化效应以后, 只有当器件的表面势最小值等于  $\phi_{\text{sTH}}$  时, 可以认为器件导通, 此时可以得到器件的阈值电压.

# 4 结果与分析

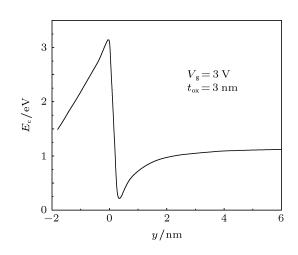

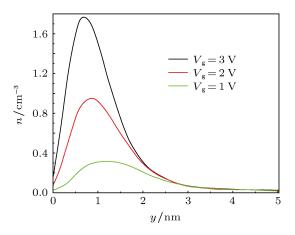

薛定谔 - 泊松方程自洽模拟可以精确计算体系 载流子分布和静电势能分布,结合 ISE 仿真,对本 文的计算结果进行验证. 在使用 ISE 的过程中, 采 用了高场饱和迁移率模型、载流子散射迁移率模 型、SRH 复合模型、雪崩模型,同时为引入量子化 效应, 采用了 Van Dort 量子修正模型, 对于高 k 材 料的模拟,编写了  $Al_2O_3$  和  $HfO_2$  参数文件. 图 4 和 图 5 给出了自洽解模拟 SOI MOSFET 器件界面势 垒和反型层电子面密度的分布图. 从图中可以看出, 由于强电场的存在, 栅介质和硅沟道界面附近的沟 道发生了能带弯曲[13,14], 电子面密度在界面处很 小,随着离开表面距离的增加,电子浓度先增加,达 到峰值以后减小,分布也有所展宽.同时,随着外加 栅电压越高.则电子面密度最大值越靠近栅介质和 硅沟道的界面,并且电子分布的宽度减小. 这些都 是因为能级量子化效应引起的载流子分布在空间 上产生位移所导致的.

图 4 界面势垒的分布图

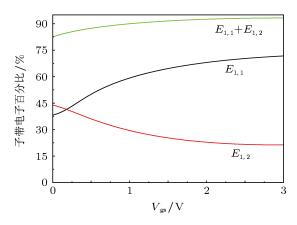

图 6 所示为最低 2 个子带上电子浓度占总浓度的百分比,本文仅计算了最低二个子带,从图中可以看出,当栅电压从 0 V 变化到 3 V 时,最低二个子带的电子数量占总载流子数量的 90%左右.由于能量量子化,载流子遵守离散子带分布,进而取代了经典理论的连续能带.因此,每个子带的载流子

密度可由子带能级和二维态密度计算得出. 从计算结果可以看出, 最低两个子带的载流子在总电子数量中占支配地位. 所以, 采用最低的二个子带来简化计算也是十分合理的.

图 5 载流子浓度的分布图

图 6 最低两个子带电子浓度占总浓度的百分比

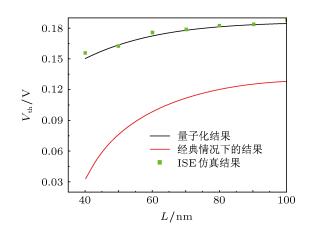

阈值电压是器件的最重要的参数,它定义为器件开始导通时的电压,阈值电压对于电路性能的影响很大.因此,建立精确的阈值电压模型非常重要.图 7 给出了阈值电压随沟道长度的变化,从图中可以看出,在考虑量子化效应的条件下,器件的阈值电压明显高于经典情况下的器件阈值电压,这与前面的理论分析一致.同时,随着器件沟道长度的减小,器件的阈值电压也随着减小.从图中可以看出,本文的计算结果与 ISE 仿真结果基本一致,证明了本文计算过程的正确性.但在经典情况下,器件的阈值电压下降的较快,这是由于量子效应引起的阈值电压增加部分抵消了由沟长减小引起的阈值电压的减小.因此,在建立小尺寸器件的阈值电压时,不考虑量子化效应会造成一定的误差.

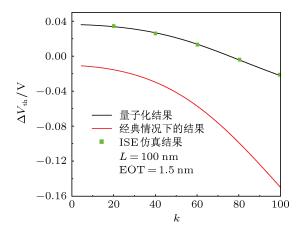

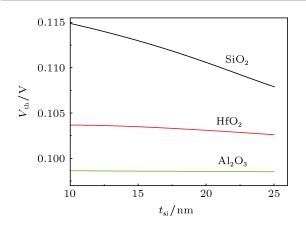

随着器件尺寸越来越小, 栅极漏电流对器件性 能的影响已经不能忽视, 因此要选取高 k 材料来代 替传统的 SiO<sub>2</sub> 层, 提高栅氧化层的物理厚度. 图 8 给出了阈值电压漂移随栅氧化层介电常数的变化, 这里阈值电压漂移定义为短沟道阈值电压和沟长 为 200 nm 的器件阈值电压的偏离. 从图中可以看 出, 随 k 值增加, 量子修正的短沟道阈值电压模型 给出比经典模型小得多的阈值电压漂移,即未考虑 量子化效应的经典短沟道模型过高地估计了k值 的影响. 图中 ISE 仿真数据给出了 k 为 20, 40, 60, 80,100 时阈值电压的漂移,本文计算结果很好的 符合了 ISE 模拟结果. 图 9 给出了在不同的栅氧化 层k值下,器件阈值电压随沟道层厚度的变化关系, 从图中可以看出,随着栅氧化层k值的减小,阈值 电压随沟道层厚度的增加而减小的量越来越大,这 说明随着高 k 介质的介电常数的增加, 器件的阈值 电压减小随沟道 Si 层厚度的增加越来越不明显.

图 7 阈值电压与沟道长度的关系

图 8 阈值电压漂移与栅氧化层介电常数的关系

图 9 阈值电压与沟道厚度的关系

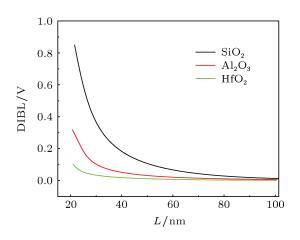

图 10 DIBL 效应随沟道长度的变化

图 10 给出了在考虑量子化效应的情况下,器件的 DIBL 随沟道长度的变化. 如图所示,当器件的沟道长度小于 50 nm 时,随着栅氧化层介质 k 值的减小而增大,而当沟道长度大于 50 nm 时,器件的 DIBL 效应都比较小,基本都趋近零. 由计算结果可以看出,采用高 k 栅氧化层介质的器件有更好的 DIBL 抑制能力.

# 5 结 论

随着器件尺寸的不断减小, SOI MOSFET 凭借 其突出的优点成为了研究热点. 本文通过自洽求 解薛定谔 - 泊松方程, 对高 k 栅介质 SOI MOSFET 进行了数值计算. 从计算结果可以看出, 考虑量子 化效应以后, 器件沟道的反型层载流子偏离栅介质 和沟道界面, 增大了栅氧化层厚度. 同时, 随着 k 值 增加, 量子修正的器件阈值电压比经典情况下有 小的多的阈值电压漂移, 量子效应和短沟道效应对 阈值电压的影响有互相补偿的作用. 采用高 k 栅 介质, 不仅能有效降低器件的栅极泄漏电流, 而且 对 DIBL 的抑制能力更强. 本文的计算过程采用成 熟的有限差分方法, 具有计算速度快, 精度高的特 点, 通过与 ISE 仿真结果对比, 也证明了本文计算 过程的正确性.

<sup>[1]</sup> Li C, Zhuang Y Q, Zhang L, Bao J L 2012 Chin. Phys. B 21 048501

<sup>[2]</sup> Chaudhry A, Kummer M J 2004 IEEE Trans. on Devices Mater. Rel. 4 99

<sup>[3]</sup> Coling J P 1993 Silicon-on-Insulator Technology. (Boston: Kluwer Academic publishers) p5

<sup>[4]</sup> Hirosh Iwai 2004 Solid-State Electronics. 48 497

<sup>[5]</sup> Meind J D, Chen Q, Davis J A 2001 Science 293 2044

<sup>[6]</sup> Depas M, Ngarn T, Heyns M M 1996 IEEE Trans. Electron Devices 43 1499

<sup>[7]</sup> Li J, Liu H X, Li B, Cao L, Yuan B 2010 Acta Phys. Sin. **59** 8131 (in Chinese) [李进, 刘红侠, 李斌, 曹磊 2010 物理学报 **59** 8131]

<sup>[8]</sup> Goser K, Glosekotter P, Dienstuhl J 2004 Germany. Springer-Verlag Berlin Heidelberg.

<sup>[9]</sup> Ma F, Liu H X, Kuang Q W, Fan J B 2012 Chin. Phys. B 21 057304

<sup>[10]</sup> Onishi K, Choi R, Kang C S, Cho H J, Kim Y H, Nieh R E, Han J, Krishnan S A, Akbar M S, Lee J C 2003 IEEE Trans. Electron Devices. 50 1517

<sup>[11] [</sup>刘恩科, 朱秉升, 罗晋生 1997 半导体物理学 (第 4 版) (北京: 国防工业出版社) 第 53 页]

<sup>[12]</sup> Schwarz S A, Russek S E 1983 IEEE Trans. Electron Devices 30 1634

<sup>[13]</sup> Yu Z P, Robert W D, Richard A K 2000 IEEE Trans. Electron Devices 47 1819

<sup>[14]</sup> Bryan A, Biegel, Mario G, Ancana, Conor S, Rafferty 2004 NAS Technical Report. NAS-04008

# Study of the SOI MOSFET characteristics of high-k gate dielectric with quantum effect\*

Cao Lei<sup>†</sup> Liu Hong-Xia

(Key Lab of Ministry of Education for Wide Band-Gap Semiconductor Materials and Devices, School of Microelectronics, Xidian University, Xi'an 710071, China)

(Received 11 June 2012; revised manuscript received 16 July 2012)

#### **Abstract**

In the paper, we mainly investigate the SOI MOSFET characteristics of high-k gate dielectric with quantum effect. Self-consistent solutions of Schrödinger and Poisson equation are solved in this paper to obtain carrier wave function in the directiong perpendicular to the SiO2/Si interface and energy level distribution. Based on Young model, the threshold voltage and short-channel effects of SOI MOSFET with high-k gate dielectric are simulated and analyzed. The carrier distribution in inversion layer deviates from the surface with the increase of longitudinal electric field, which is caused by quantum effect. It increases the thickness of effective gate oxide and fluctuation of threshold voltage. Meanwhile, high-k gate dielectric materials can reduce the threshold voltage and restrain the DIBL efficiently. The calculation results matching ISE simulation results show that the model has a high-level accuracy, and faster operation ensures the efficiency of the simulation analysis.

**Keywords:** quantum effect, high-K material, SOI MOSFET, threshold voltage

PACS: 73.40.Qv, 73.40.Lq, 12.39.Pn

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (Grant Nos. 61076097, 60936005), the Cultivation Fund of the Key Scientific and Technical Innovation Project, Ministry of Education of China Program (Grant No. 708083), and the Specialized Research Fund for the Doctoral Program of Higher Education (Grant No. 20110203110012).

<sup>†</sup> E-mail: cao0273@sina.com