# 0.18 μm 窄沟 NMOS 晶体管总剂量效应研究\*

吴雪1)2)3) 陆妩1)2)\* 王信1)2)3) 席善斌1)2)3) 郭旗1)2) 李豫东1)2)

1)(中国科学院特殊环境功能材料与器件重点实验室,新疆理化技术研究所,乌鲁木齐 830011)

2) (新疆电子信息材料与器件重点实验室,乌鲁木齐 830011)

3) (中国科学院大学, 北京 100049)

(2011年11月28日收到;2013年3月3日收到修改稿)

为明确深亚微米 NMOS 器件抗辐照能力以及研究其加固措施,本文对 0.18 μm 窄沟 NMOS 晶体管进行了<sup>60</sup>Coγ 总剂量辐射效应研究. 结果表明: 和宽沟器件不同, 阈值电压、跨导、漏源电导对总剂量辐照敏感, 此现象被称之为辐射感生窄沟道效应; 相比较栅氧化层, 器件隔离氧化层对总剂量辐照更敏感; 窄沟道 NMOS 器件阈值电压不仅和沟道耗尽区电荷有关, 寄生晶体管耗尽区电荷对其影响也不可忽略, 而辐照引起源漏之间寄生晶体管开启,形成漏电通道, 正是导致漏电流、亚阈斜率等参数变化的原因.

关键词:  $0.18\mu m$ , 窄沟 NMOS 晶体管,  $^{60}Coy$  辐照, 辐射感生窄沟道效应

**PACS:** 61.80.Ed, 77.84.Bw, 85.30.Tv **DOI:** 10.7498/aps.62.136101

## 1 引言

20世纪80年代以来, 国内外对大尺寸 MOS器 件进行了充分的总剂量辐射效应研究[1-3],研究发 现器件栅氧化层和隔离氧化层在辐照过程中都会 产生大量氧化陷阱电荷及界面陷阱电荷,从而对器 件性能造成辐射损伤, 近年来, 随着集成电路的发 展和制造工艺的进步, 半导体器件特征尺寸急剧减 小. 当器件特征尺寸降至深亚微米尺寸时, 栅氧化 层厚度仅有几个 nm, 隔离技术也由原来的 LOCOS 隔离转变为 STI 隔离技术. 随着栅氧化层厚度的 减小, 60Coγ 辐照在栅氧化层中引入的陷阱电荷大 大减少, 栅氧漏电流的变化基本可以忽略, 阈值电 压漂移也可以忽略不计[4],但是隔离氧化层的厚度 相比栅氧化层要大很多, 所以隔离氧化层的敏感性 仍然是深亚微米器件的短板. 但是小尺寸器件本身 带来的功耗降低,工作频率提高等优点使得其在航 空航天领域集成电路中的应用也越来越广泛, 所以 开展小尺寸器件的总剂量效应研究是必要的. 国

内外对 0.18 μm 甚至更小尺寸的宽沟 NMOS 器件进行了研究 [4-6], 但是对于 0.18 μm 窄沟 NMOS 器件<sup>60</sup>Coγ 总剂量辐照试验开展较少. 无论是在集成电路设计还是在工艺参数提参建模应用中, 窄沟器件的作用都不可忽略. 并且窄沟器件由于本身具有窄沟道效应, 其辐照后参数变化趋势、失效模式、损伤机理和宽沟器件是否一致, 都不明确. 因此, 对窄沟 NMOS 晶体管进行<sup>60</sup>Coγ 总剂量辐射效应研究势在必行. 本文主要是对窄沟 NMOS 晶体管进行总剂量辐照实验, 通过提取辐照后的参数来进行提参建模研究.

### 2 总剂量辐照实验

实验样品为国产标准工艺线  $0.18~\mu m$  窄沟 NMOS 晶体管, 其  $W/L=0.22~\mu m/20~\mu m$ , 栅氧化层厚度为 3.981~n m, 器件采用 STI 隔离技术, 工作电压为 1.8~V. 辐照实验在中国科学院新疆理化技术研究所 $^{60}$ Coy 源上进行, 剂量率为 50~r ad/s(Si). 辐照过程中, 器件处于最劣偏置条件: 栅极电压  $(V_G)$  为

<sup>\*</sup>模拟集成电路国家重点实验室 (NLAIC) 基金 (批准号: 9140C090402110C0906) 资助的课题.

<sup>†</sup> 通讯作者. E-mail: luwu@ms.xjb.ac.cn

<sup>© 2013</sup> 中国物理学会 Chinese Physical Society

1.8 V, 源极 (*V*<sub>S</sub>)、漏极 (*V*<sub>D</sub>) 和衬底 (*V*<sub>B</sub>) 全部接地. 每一次辐照完成后, 对被辐照样品进行 *I-V* 曲线测试. 在辐照后测试过程中, 对栅极电流进行了测试, 确保实验样品在辐照及测试过程中栅极没有发生 击穿现象. 曲线测试是在 HP4142 半导体综合参数 分析仪上完成, 每一次测试过程不超过 20 min, 以减小测试所带来的退火效应.

#### 3 实验结果与分析讨论

#### 3.1 辐照前后参数变化

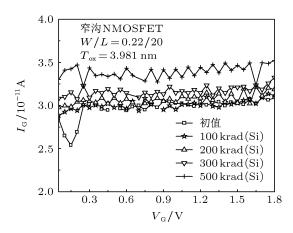

图 1 是不同总剂量下栅极电流随着栅极电压的变化. 整个辐照过程中, 栅极电流变化非常小, 辐照总剂量到 500 krad(Si) 时, 栅极电流也只是从约  $3.0 \times 10^{-11}$  A 增至  $3.5 \times 10^{-11}$  A, 器件功能正常.

图 1  $I_G$ - $V_G$  曲线变化趋势图 ( $V_D = 50$  mV,  $V_B = V_S = 0$  V)

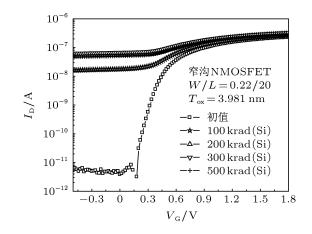

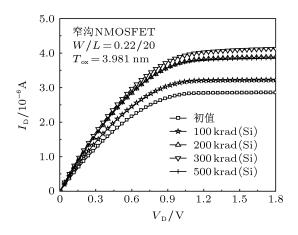

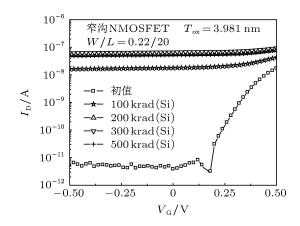

图 2 和图 3 分别为实验样品转移特性曲线和输出特性曲线随辐照总剂量的变化. 从图 2 中我们可以看出,随着辐照总剂量的增加,样品漏电流增大. 总剂量到 100 krad(Si) 时,曲线变化非常明显,之后随着总剂量的增大,曲线变化趋势变缓. 辐照结束后,样品漏电流从初始的 10<sup>-11</sup> A 增大至 10<sup>-7</sup> A,增幅达 4 个数量级. 漏电流的增大使得器件功耗增加,这对工作在辐射环境下的集成电路是非常不利的. 另外,漏电流的增大,也使得 NMOSFET 一直处于 ON 状态,无法进入 OFF 状态,这种现象在数字集成电路应用中是不允许的. 图 3 表明,随着辐照总剂量的增加,饱和区漏电流增幅比较明显,在总剂量达到 300 krad (Si) 时,增幅达到最大,500 krad (Si) 时,输出特性曲线和 200 krad (Si) 时的曲线基本重合. 这一点和转移特性曲线变化一致.

#### 3.2 分析讨论

#### 3.2.1 栅极电流

辐照会在栅氧化层中产生氧化陷阱电荷, 增大栅极到沟道之间的电流. 本实验样品栅氧化层厚度只有 3.981 nm, 对于超薄栅氧化层 (< 6 nm) 来说, 栅极或者 Si/SiO<sub>2</sub> 界面的电子会隧穿至栅氧化层中, 这样辐照过程中栅氧化层产生的氧化陷阱电荷就有可能会被隧穿过来的电子中和 <sup>[7,8]</sup>, 其电子隧穿的距离可以通过下式来确定:

$$X_{\rm m} = (1/2\beta) \times \ln(t/t_0), \tag{1}$$

β 是隧穿因子,和电子的势垒高度有关.对于 SiO<sub>2</sub> 来说,如果陷阱电荷距离界面超过 4 nm,则电子隧穿至 SiO<sub>2</sub> 层中中和陷阱电荷的概率很小,所以陷阱电荷被隧穿电子中和的数量和栅氧化层中陷阱电荷的分布密切相关 <sup>[9]</sup>.本文中实验样品栅极电流变化不明显,说明栅氧化层因辐照产生的氧化陷阱电荷大部分被隧穿电子中和.

图 2 转移特性曲线变化趋势图 ( $V_D = 50 \text{ mV}, V_B = V_S = 0 \text{ V}$ )

图 3 输出特性曲线变化趋势图 ( $V_G = 1.8 \text{ V}, V_B = V_S = 0 \text{ V}$ )

#### 3.2.2 阈值电压、截止漏极电流

根据 MOS 晶体管饱和区漏极电流的公式 [10]

$$I_{\rm D} = \frac{1}{2} \mu C_{\rm OX} \frac{W}{L} (V_{\rm G} - V_{\rm T})^2 \tag{2}$$

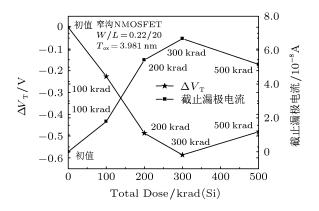

得出饱和区漏电流和阈值电压成平方关系, 我们对饱和区  $\sqrt{I_D}$ - $V_G$  曲线进行线性拟合, 提取样品不同总剂量下的阈值电压值. 定义  $V_G=0$  V 时的漏电流为截止漏极电流. 其变化如图 4 所示. 阈值电压的变化和国内报道 0.18  $\mu$ m 宽沟 NMOS 晶体管阈值电压不随总剂量辐照发生变化的现象不同  $^{[4]}$ , 我们称之为辐射感生窄沟道效应 (radiation-induced narrow channel effect, RINCE).

图 4 辐照前后阈值电压和截止漏极电流变化曲线 ( $V_D=50$  mV,  $V_B=V_S=0$  V)

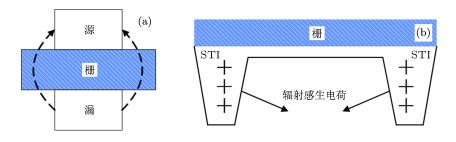

在氧化层中,辐照产生大量电子空穴对,电子被电场迅速扫描出氧化层,留下带正电的空穴.然后空穴迅速被晶体管边缘的 STI 隔离氧化层的陷阱俘获,形成正的氧化物陷阱电荷.随着氧化物陷阱电荷的积累,最终在隔离氧化层形成一个较大的电场. 当电场强度达到一定值,隔离氧化层下衬底表面反型,源漏之间两侧寄生晶体管开启,形成漏电通道,如图 5 所示,从而导致漏电流的增加. 由图 2 可知,100 krad(Si) 时,寄生晶体管已经开启,源漏之间的漏电通道已经形成,之后随着总剂量的增加,寄生晶体管沟道电流逐渐饱和;总剂量从 300 krad(Si) 到 500 krad(Si),辐射产生的界面陷阱电荷占据主导地位,从而使漏电流减小.

隔离氧化层中辐照产生的正氧化物陷阱电荷会导致隔离氧化层下的衬底表面感应出相应的耗尽区电荷,进一步导致栅电极对于沟道边缘部分控制能力减弱. 当沟道宽度 W 很宽时,衬底表面感应出的耗尽区电荷可以忽略;但是当 W 很窄时,这些

电荷在整个沟道耗尽区电荷中所占的比列将增大. 当考虑这些电荷时, 窄沟道 NMOS 晶体管阈值电压  $(V_{\rm T})_{\hat{r}}$  可通过下式描述  $^{[10]}$ :

$$(V_{\rm T})_{\tilde{\gamma}_{\rm F}} = \phi_{\rm MS} - \frac{Q_{\rm OX}}{C_{\rm OX}} - \frac{Q_{\rm A}}{C_{\rm OX}} \times \left(1 + \frac{2\Delta W}{W}\right) + 2\phi_{\rm Fp}. \tag{3}$$

(2) 式中平带电压  $V_{FB} \left(V_{FB} = \phi_{MS} - \frac{Q_{OX}}{C_{OX}}\right)$ , 衬底费米势  $\phi_{Fp}$  在辐照过程中可视为常量. 而栅氧化层电压  $V_{OX} \left(V_{OX} = \frac{Q_{A}}{C_{OX}} \times \left(1 + \frac{2\Delta W}{W}\right), Q_{A}\right)$  为沟道耗尽区电荷 ) 则和辐射相关. 如前所述, 辐照会使隔离氧化层下衬底表面更加耗尽或者反型, 影响主晶体管的电场, 使晶体管沟道耗尽区电荷面密度增加. 当 W 很大时,  $\Delta W/W$  可以忽略, 这部分电荷面密度对阈值电压的影响就可以忽略掉, 所以对于宽沟 NMOS 晶体管, 辐照前后阈值电压基本不变, 这于文献 [4] 中的实验现象相符合. 当 W 很小时,  $\Delta W/W$  不可以忽略, 寄生晶体管耗尽区的电荷面密度对阈值电压的影响也就不可以忽略掉. 众所周知, 辐照过程中, 氧化陷阱电荷的形成很快, 相反, 界面陷阱电荷的形成则是一个慢过程. 氧化陷阱电荷 ( $N_{ot}$ ) 和界面陷阱电荷 ( $N_{it}$ ) 对阈值电压的影响为

$$\Delta V_{\rm T} = (-q/C_{\rm OX}) \times (\Delta N_{\rm ot} - \Delta N_{\rm it}). \tag{4}$$

对于 NMOS 晶体管来说,氧化陷阱电荷带正电,界面陷阱电荷带负电,二者相互补偿.辐照一开始,产生大量的氧化陷阱电荷,界面陷阱电荷产生的数量较小,使得阈值电压减小,当总剂量达到300 krad(Si)时,氧化陷阱电荷和界面陷阱电荷的数量达到了一个平衡,之后,界面陷阱电荷数量占据主导作用,使得晶体管阈值电压开始回漂,并因此降低了截止漏极电流.

#### 3.2.3 亚阈斜率以及跨导

亚國斜率 S 是反映 MOS 晶体管亚阈区特性的一个重要参数, 在半对数坐标中亚阈区  $I_D$ - $V_G$  是一条直线, 其随总剂量的变化如图 6 所示, 随着总剂量的增大, 亚阈斜率增加. 总剂量到 100 krad(Si) 时, 随着栅极电压  $V_G$  变化, 亚阈区漏电流  $I_D$  的变化幅度已达不到一个数量级, 即样品已经不能关断, 这与前面漏电流分析一致. 亚阈斜率的增加意味着  $V_G$  对  $I_D$  的控制能力减弱, 在数字电路中会影响其关态噪声容限, 在模拟电路中影响电路的功耗、增益、信号失真、及噪声特性等. 流过寄生晶体管的辐射

感生电流和主晶体管的电流相比要小得多<sup>[6]</sup>, 所以 辐照后, 漏电流的变化对亚阈区的影响远大于对饱 和区的影响, 这一点从图 1 中的  $I_D$ - $V_G$  曲线可以得到证实.

图 5 NMOS 晶体管源漏之间漏电通道形成示意图 (a) 俯视图; (b) 剖面图

图 6 辐照前后亚阙区  $I_D$ - $V_G$  变化曲线 ( $V_D$  = 50 mV,  $V_B$  =  $V_S$  = 0 V)

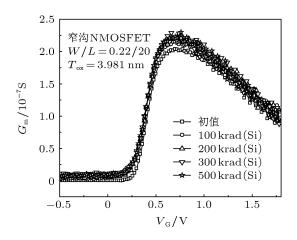

跨导  $G_{\rm m}$  是 MOS 晶体管转移特性曲线的斜率, 在表征 MOS 电路线性区的特性时, 是一个重要参数, 当器件宽长比固定时, 它的性能直接反映了 Si/SiO<sub>2</sub> 界面或界面附近缺陷的散射作用对沟道载流子有效迁移率的影响. 图 7 给出了不同总剂量下跨导的变化趋势图. 对于 NMOS 来说, 当宽长比固定时, 辐照后迁移率变化可以通过下式来表示:

$$\mu = \mu 0/(1 + \beta \Delta N_{\rm ot}), \tag{5}$$

其中 μ<sub>0</sub> 是载流子初始迁移率, β 是常数. 从 (5) 式中可以看出迁移率变化和辐照在 Si/SiO<sub>2</sub> 界面或界面附近感生出的氧化物陷阱电荷成反比, 也就是说辐照在 Si/SiO<sub>2</sub> 界面或界面附近感生出的氧化物陷阱电荷会导致迁移率降低. 仔细观察图 7, 发现辐照后迁移率没有降低, 反而稍微有所增加, 这和前面分析的辐照引起器件有效沟道宽度增加符合. 因此我们可以得出, 样品的有效迁移率没有发生明显变化, 跨导的增加是辐照引起有效沟道宽度增大

导致的.

图 7 辐照前后跨导变化曲线  $(V_D = 50 \text{ mV}, V_B = V_S = 0 \text{ V})$

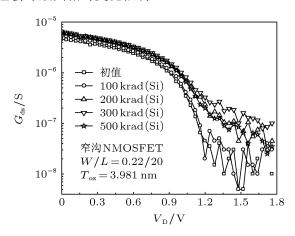

#### 3.2.4 漏源电导

漏源电导  $g_{ds}$  是 MOS 晶体管输出特性曲线的 斜率,它反映 MOS 晶体管的漏极电流随漏源电压 的变化而变化的情况,其随辐照总剂量的变化如图 8 所示. 随着辐照总剂量增加,漏源电导增大. 在辐照过程中,样品有效宽度增大,阈值电压先减小后增大. 根据下式 [11]:

$$g_{\rm ds} = \mu_{\rm n} C_{\rm OX} \frac{W}{L} [(V_{\rm G} - V_{\rm T}) - V_{\rm D}]$$

(6a)

$$g_{\rm ds} = \frac{1}{2} \lambda \mu_{\rm n} C_{\rm OX} \frac{W}{L} (V_{\rm G} - V_{\rm T})^2, \tag{6b} \label{eq:gds}$$

其中 (6a) 式是线性区漏源电导表达式, (6b) 式是饱和区漏源电导表达式, λ为沟道长度调制系数. 有效宽度增大和阈值电压减小会使漏源电导增加, 阈值电压增大会使漏源电导减小, 这和图 8 线性区变化是符合的. 从图 8 中, 我们可看出, 饱和区漏源电导总剂量辐照后相对变化比线性区要明显. 因为理论上讲饱和区漏源电导为 0, 考虑沟道长度调制效

应后,饱和区漏源电导虽不为 0,但也很小,所以辐照后无论是有效宽度还是阈值电压,其微小的变化也会导致其相对变化很明显.

图 8 辐照前后漏源电导变化曲线 ( $V_G = 1.8 \text{ V}, V_B = V_S = 0 \text{ V}$ )

#### 4 结 论

通过对 0.18 µm 窄沟 NMOS 晶体管总剂量效应研究, 结合前人 <sup>[4,6,12,13]</sup> 对宽沟 NMOS 晶体管总剂量效应研究结果, 我们得到以下结论, 如表1所示.

从表 1 中我们可以看出, 栅极电流, 截止漏极电流, 亚阈斜率等电参数宽沟 NMOS 晶体管和窄沟 NMOS 晶体管辐照后变化一致. 分析指出, 栅极

电流不变化主要是因为栅氧化层很薄,辐照引入的 电荷被隧穿过来的电子中和掉,进而降低了辐照引 入的电荷对栅极电流的影响. 截止漏极电流及亚阈 斜率的变化主要是 STI 隔离氧化层在辐照后引入 电荷造成的. 辐照引起寄生晶体管开启, 形成漏电 通道,从而增大漏极电流.对于阈值电压,跨导,漏 源电导等电参数, 窄沟 NMOS 晶体管辐照后变化 趋势和宽沟 NMOS 晶体管不一致. 主要是因为对于 窄沟 NMOS 晶体管来说, 总剂量辐照会引起晶体 管有效宽度变化且不可忽略,有效宽度的变化对阈 值电压, 跨导, 漏源电导等的影响不可忽略. 随着器 件特征尺寸的减小及小尺寸器件在集成电路中的 应用越来越广泛, 辐照感生窄沟道效应的重要性越 来越突出,对此我们应该进一步对此进行更多的研 究,为接下来深亚微米建模提参工作以及设计加固 措施提供更多的有效数据和理论依据.

表 1 0.18 μm 宽沟 NMOS 晶体管和窄沟 NMOS 晶体 管总剂量效应比较

| NMOS 晶体管电参数 | 宽沟 NMOS 晶体管                     | NMOS 窄沟晶体管    |

|-------------|---------------------------------|---------------|

| 栅极电流        | $\rightarrow$ <sup>[4,13]</sup> | $\rightarrow$ |

| 截止漏极电流      | ↑ <sup>[4,12,13]</sup>          | <b>†</b>      |

| 阈值电压        | $\rightarrow^{[4,6]}$           | $\downarrow$  |

| 亚阈斜率        | ↑ <sup>[4,12,13]</sup>          | <b>†</b>      |

| 跨导          | $\rightarrow^{[4,13]}$          | <b>†</b>      |

| 漏源电导        | $\rightarrow^{[4]}$             | <b>†</b>      |

- [6] Faccio F, Cervelli G 2005 IEEE Trans. Nuc. Sci. 52 2413

- [7] Oldham T R, Lelis A J, McLean F B 1986 IEEE Trans. Nucl. Sci. 33

203

- [12] Chatterjee A, Rogers D, McKee J, Ali I, Nag S, Chen I C 1996 International Electron Devices Meeting San Francisco, CA, USA, December 8–11, 1996 p829–832

- [13] Barnaby H J 2006 IEEE Trans. Nucl. Sci. 53 3103

<sup>[1]</sup> He B P, Chen W, Wang G Z 2006 Acta Phys.Sin. **55** 3546 (in Chinese) [何宝平, 陈伟, 王桂珍 2006 物理学报 **55** 3546]

<sup>[2]</sup> Li D M, Wang Z H, Huangpu L Y, Gou Q J, Lei Y H, Li G L 2007 Chinese Journal of Electron Devices. 30 745 (in Chinese) [李冬梅, 王 志华, 皇甫丽英, 勾秋静, 雷有华, 李国林 2007 电子器件 30 745]

<sup>[3]</sup> Winokur P S,Schwank J R,McWhorter P J,Dressendorfer P V, Turpin D C 1984 IEEE Trans. Nuc. Sci. 31 1453

<sup>[4]</sup> Liu Z L, Hu Z Y, Zhang Z X, Shao H, Ning B X, Bi D W, Chen M, Zou S C 2011 *Acta Phys. Sin.* **60** 116103 (in Chinese) [刘张李, 胡志远, 张正选, 邵华, 宁冰旭, 毕大炜, 陈明, 邹世昌 2011 物理学报 **60** 116103]

<sup>[5]</sup> Johnston A H, Swimm R T, Allen G R, Miyahira T F 2009 IEEE Trans. on Nuc. Sci. 56 1941

<sup>[8]</sup> McWhorter P J, Miller S L, Miller W M 1990 IEEE Trans. Nucl. Sci. 37 1682

<sup>[9]</sup> Saks N S, Ancona M G, Modolo J A 1984 IEEE Trans. Nucl. Sci. 31 1249

<sup>[10]</sup> Chen X B, Zhang Q Z 2006 Transistor Principle and Design (Beijing: Publishing House of Electronics Industry) p294 (in Chinese) [陈星弼, 张庆中 2006 晶体管原理与设计 (北京: 电子工业出版社) 第 294 页]

<sup>[11]</sup> Behzad Razavi 2001 Design of Analog CMOS Integrated Circuits (Published by McGraw-Hill) p17–26

# Total ionizing dose effect on 0.18 $\mu$ m narrow-channel NMOS transistors\*

Wu Xue $^{(1)2)3}$  Lu Wu $^{(1)2)\dagger}$  Wang Xin $^{(1)2)3}$  Xi Shan-Bin $^{(1)2)3}$  Guo Qi $^{(1)2)}$  Li Yu-Dong $^{(1)2)}$

1) (Key Laboratory of Functional Materials and Devices for Special Environments, Xinjiang Technical Institute of Physics and Chemistry, Chinese Academy of Sciences, Urumq 830011, China)

2) (Xinjiang Key Laboratory of Electronic Information Material and Device, Urumqi 830011, China)

3) (University of Chinese Academy of Sciences, Beijing 100049, China)

(Received 28 November 2011; revised manuscript received 3 March 2013)

#### **Abstract**

This paper describes the total ionizing dose effect on 0.18  $\mu$ m narrow-channel NMOS transistors which are exposed to a  $\gamma$ -ray radiation. Electrical parameters such as threshold voltage, leakage current, trans-conductance, drain-source conductance, and subthreshold slope extracted from the *I-V* curves are analyzed pre-and post-irradiation. Results show that the threshold voltage, the trans-conductance, and the drain-source conductance are sensitive to radiation compared to wide-channel NMOS transistors—the effect we call radiation induced narrow channel effect(RINCE). The amount of oxide-trapped charges and interface states which would degrade the threshold voltage and leakage current is induced in the STI oxide. The gate oxide is insensitive to irradiation. Combining the structure and process of devices, we finally discuss and analyze the above phenomenon in detail.

**Keywords:** 0.18 μm, narrow-channel NMOS transistor, <sup>60</sup>Coγ, RINCE

**PACS:** 61.80.Ed, 77.84.Bw, 85.30.Tv **DOI:** 10.7498/aps.62.136101

<sup>\*</sup> Project supported by the Foundation of NLAIC (grant No. 9140C090402110C0906).

<sup>†</sup> Corresponding author. E-mail: luwu@ms.xjb.ac.cn