# 基于异质双栅电极结构提高碳纳米管场效应 晶体管电子输运效率\*

刘兴辉1)† 赵宏亮1) 李天宇1) 张仁1) 李松杰1) 葛春华2)

1)(辽宁大学物理学院, 沈阳 110036)2)(辽宁大学化学院, 沈阳 110036)

(2013年3月13日收到; 2013年4月2日收到修改稿)

为改善碳纳米管场效应晶体管 (CNTFET) 器件性能,提高电子输运效率,提出了一种异质双金属栅 (HDMG) 电极结构 CNTFET 器件. 通过对单金属栅 (SMG)-CNTFET 器件输运模型的适当修改,实现了对 HDMG-CNTFET 器件电子输运特性的研究. 研究结果表明,对于所提出的 HDMG 结构器件,如果固定源端金属栅 S-gate 的功函数  $W_{GS}$  使其等于本征 CNT 的功函数,而选取漏端金属栅 D-gate 的功函数  $W_{Gd}$ ,使其在一定范围内小于  $W_{GS}$ ,可优化器件沟道中的电场分布,提高器件沟道电子平均输运速率;同时由于 HDMG-CNTFET 的 D-gate 对沟道电势具有调制作用,使该器件阈值电压降低,导致在相同的工作电压下,HDMG-CNTFET 器件具有更大的通态电流;而 D-gate 对漏电压的屏蔽作用又使 HDMG-CNTFET 与 SMG-CNTFET 相比具有更好的栅控能力及减小漏极感应势垒降低效应、热电子效应和双极导电性等优点. 本研究通过合理选取 HDMG-CNTFET 双栅电极的功函数,有效克服了现有研究中存在的改善 CNTFET 性能需要以减小通态电流为代价的不足,重要的是提高了器件的电子输运效率,进而可提高特征频率、减小延迟时间,有利于将 CNTFET 器件应用于高速/高频电路.

关键词: CNTFET, 异质双栅, 电子输运效率, 双极导电性

**PACS:** 73.63.Fg, 85.35.Kt, 73.23.Ad, 73.23.-b **DOI:** 10.7498/aps.62.147308

#### 1 引言

碳纳米管 (carbon nanotube, CNT) 自 1991 年被发现以来, 因具有独特的准一维几何结构、对称的能带以及其他优异的物理、化学等性质在诸多领域得到广泛应用. 从电子学角度来讲, 根据卷曲手性的不同, CNT 可分别表现出金属性和半导体性 [1-3], 利用半导体性 CNT 做沟道可制作 CNT 场效应晶体管 (CNT field-effect transistor, CNTFET) 器件, 这种器件最早于 1998 年研制成功 [4,5]. CNTFET 器件的出现为将弹道输运理论应用于新材料电子系统的研究提供了良好的平台, 从而引起了相关研究人员的极大兴趣. 目前 CNTFET 研究已取得了较大进展, 已有报道, CNTFET 的沟道长度已可小于 20 nm 尺度 [6], 使该类器件应用于纳米集成电路成

为可能 [7,8]

然而,一方面,随器件尺寸缩小,与硅基 MOS-FET 器件类似,在几十纳米甚至十几纳米尺度范围内,栅控能力下降,短沟道效应、热载流子效应等也不可避免地限制 CNTFET 器件的进一步应用.为此,人们采取多种方法尝试对器件结构进行优化,例如采用源 HALO 结构 <sup>[9]</sup>、源/漏 HALO-LDD结构 <sup>[10]</sup>、线性沟道掺杂 <sup>[11]</sup>、栅与源/漏区交叉重叠 <sup>[12]</sup>等措施,为改善器件性能提供理论指导,但已有的报道中提高器件性能都是以牺牲较大幅度的通态电流为代价的,这将导致器件的驱动能力降低,限制其在电路中进一步的应用.另一方面,CNT具有准弹道电子输运特性 <sup>[13,14]</sup>、高的电子费米速度 (10<sup>6</sup> m/s) <sup>[15]</sup>,利用这些特性将 CNTFET 用于高速/高频电路领域是非常有意义的工作.基于此,如何提高沟道中平均电子输运速率以提高器件特征

<sup>\*</sup>国家自然科学基金(批准号: 21171081)、辽宁省科技厅自然科学基金(批准号: 20082050)和辽宁省教育厅高等学校科研基金(批准号: L2010152)资助的课题.

<sup>†</sup>通讯作者. E-mail: liuxinghuixjtu@sohu.com

频率也是急需解决的问题,需要深入研究.

受硅基 MOSFET 器件研究的启发,本文将异质 双金属栅 (HDMG) 结构引入 CNTFET 器件, 并且通 过合理选择两种不同金属栅电极的功函数,以实现 对 CNTFET 沟道电场分布进行调制, 有利于提高器 件电子输运效率. HDMG-CNTFET 器件的建模求 解采用非平衡格林函数 (non-quilibrium Green function, NEGF) 理论, 通过修改 SMG-CNTFET 的输运 模型来实现. 研究表明, 所得的 HDMG-CNTFET 器 件同 SMG-CNTFET 器件相比, 改善栅控能力 (例如 提高器件跨导、降低关断电流、提高电流开关比、 减小漏电导)的同时,降低了热电子效应、漏极感 应势垒降低效应以及双极性传导特性, 重要的是所 提出的双栅结构提高了通态电流和电子的输运速 率 (合称为电子输运效率), 从而有利于提高器件的 特征频率、减少延迟时间,有利于将器件应用于高 速/高频电路.

#### 2 器件几何结构

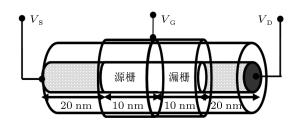

基于 HDMG 结构的 CNTFET 所采用器件结构的剖面图如图 1 所示. 基本结构采用圆柱形结构 (为减少计算量,目前关于 CNTFET 的理论计算通常采用该种结构),该种结构在实际工艺中已可以实现 [16].模型中整个 CNT 器件分为三段区域,CNT 采用手性为 (13,0)的锯齿型管. 两侧各 20 nm长 CNT 采用 N 型均匀重掺杂分别构成源区和漏区,源/漏掺杂浓度均为 2.0/nm (每纳米长度掺杂两个杂质原子),中间一段为本征 CNT 沟道区,长度为 20 nm. 栅介质层采用柱状环绕 CNT 结构,覆盖整个 CNT 表面,其厚度为 2 nm,介质采用 HfO2高 K 材料,其相对介电常数为 16. 栅电极环绕本征沟道区的介质层,与 CNT 形成 MIS 结构. 研究中栅极采用等长度双异质金属电极,即靠近源端的金属栅 S-gate 和靠近漏端金属栅 D-gate 长度相同,

各 10 nm, 并使它们横向接触, S-gate 和 D-gate 的功函数分别用  $W_{GS}$  及  $W_{Gd}$  表示.

图 1 HDMG-CNTTFET 的几何结构

#### 3 模拟方法

处理 CNTFET 器件的电子输运问题,运用 NEGF 理论求解已被公认为合理的方法,对于柱状单环绕栅的单壁 CNTFET 器件的建模已形成了成熟的理论体系 [9-12,17]. 具体思路如下:将单壁 CNT 以及源区 S/漏区 D (CNT 的扩展端) 看成是一个电子系统,在倒格子空间下,描述该电子系统的 NEGF 由 CNT 的哈密顿算符 H 以及源/漏区的自能函数  $\Sigma_{\rm S}/\Sigma_{\rm D}$  矩阵构成 [17]

$$G(E) = [(E + i\eta^+)I - H - \Sigma_S - \Sigma_D]^{-1}$$

, (1) 其中  $G$  为格林函数,  $E$  是能量,  $i$  为虚部,  $\eta^+$  是一个无穷小的正值,  $I$  是单位矩阵,  $\Sigma_S$  和  $\Sigma_D$  分别为 CNTFET 器件的源/漏自能矩阵. 求解思路为, 先设定 CNT 表面静电势的初始解  $U_i$ , 基于 NEGF 求解电荷密度矩阵. 利用确定的电荷密度求解泊松方程以获得 CNT 表面的电势分布, 得到新的  $U_{i+1}$  解, 再计算电荷密度, 这两个步骤不断重复, 直到在设定的误差范围内取得自治. 最后利用收敛的电荷密度计算电势、电场、电流等电学参数.

由于本研究针对的是 HDMG-CNTFET 器件, 需要将描述 SMG-CNTFET 电子系统的非平衡格林 函数 G(E) 进行修改. 而其中的  $\Sigma_S$ ,  $\Sigma_D$  与栅电极无 关, 其表达式与单金属环绕栅 CNTFET 相同  $^{[10,17]}$ , 只需将 H 表达式进行修改:

$$H = \begin{bmatrix} U_{l,1}(z, r_{j}) & b_{t} \\ b_{t} & U_{l,2}(z, r_{j}) & \gamma & & & 0 \\ & \gamma & U_{l,3}(z, r_{j}) & b_{t} \\ & & b_{t} & U_{l,4}(z, r_{j}) & \gamma & & & \\ & & \gamma & \ddots & \ddots & & \\ & & 0 & & \ddots & U_{l,N-1}(z, r_{j}) & b_{t} \\ & & & b_{t} & U_{l,N}(z, r_{j}) \end{bmatrix}_{N \times N},$$

$$(2)$$

H 表达式中的矩阵元 bt 是 CNT 的参数,与 CNT 的手性有关  $[^{10,17}]$ ,  $\gamma$  为相临 A, B 碳原子波函数的交叠积分, N 为 CNT 中碳环的数量,而第 j 个碳环处的电势能  $U_j$  同 SMG-CNTFET 器件相比则发生变化,在此用  $U_{lj}$  来表示,  $U_{lj}(z,r_j)=-eV_{lj}(z,r_j)$ , 其中的  $V_{lj}(z,r_j)$  为 CNT 表面电势,通过求解泊松方程得到,对于 HDMG 器件 CNT 表面电势分布必须根据节点 j 是处于 S-gate 下面还是 D-gate 下面或是处于源/漏扩散区等三个不同区间段需要分段求解决泊松方程, l 表示处于不同的区间段。在不同区间段,沿 CNT 表面电势分布需要在柱坐标下分别求解泊松方程:

$$\frac{1}{r}\frac{\partial}{\partial r}\left[r\frac{\partial}{\partial r}V_{l,j}(r,z_{j})\right] + \frac{\partial^{2}V_{l,j}(r,z_{j})}{\partial z^{2}}$$

$$= -\frac{\rho(r,z_{j})}{\varepsilon_{0}\varepsilon_{r}}, \quad l = 1,2,3, \tag{3}$$

其中当 l 为 1 表示金属栅 S-gate 下的沟道电势, l 为 2 表示金属栅 D-gate 下的沟道电势, l = 3 表示源/漏区的沟道电势,  $\varepsilon_0$  是真空介电常数,  $\varepsilon_r$  是栅介质层相对介电常数, z 表示沿 CNT 沟道方向, r 表示沿 CNT 的径向.  $\rho(r=r_{\text{CNT}},z_j)=e\left[N_{\text{D}}^+-N_{\text{A}}^--n(z_j)+p(z_j)\right]$  是 CNT 表面电荷密度, 其中的电子和空穴浓度  $n(z_j)$ ,  $p(z_j)$  可分别表示为[17]

$$n(z_{j}) = \sum_{q} \frac{2}{\Delta z} \int_{E_{N}}^{+\infty} \frac{1}{2\pi} [D_{S} f(E - E_{FS}) + D_{D} f(E - E_{FD})] dE,$$

$$p(z_{j}) = \sum_{q} \frac{2}{\Delta z} \int_{-\infty}^{E_{N}} \frac{1}{2\pi} [D_{S} f(E - E_{FS}) + D_{D} f(E - E_{FD})] dE,$$

(5)

其中, 对 q 求和表示考虑 CNT 能带存在能谷简并,  $\Delta z = z_{j+1} - z_j$ , 分子中的 2 表示考虑电子自旋,  $E_N$  表示禁带中央能级.  $D_{S(D)} = \text{Diag}\left(G\Gamma_{S(D)}G^+\right)$ , 为源/漏区局域状态密度, 其中的  $\Gamma_{S(D)} = i\left[\Sigma_{S(D)} - \Sigma_{S(D)}^+\right]$  为 CNT 与源/漏电子库耦合后反映源 (漏) 电子能级展宽的级宽函数.

在栅电极处求解泊松方程 (3) 采用 Drichlet 边界条件:

$$V_l = V_{gs} - \phi_{M_l S}/e, \quad (l = 1, 2),$$

(6)

其中, $V_{gs}$  为栅电压,  $\phi_{M,S}$  表示金属栅电极与 CNT 的 功函数差, l 为 1 表示源端金属栅 S-gate, l 为 2 表示漏端金属栅 D-gate. 在源/漏掺杂区处求解泊松方程采用纽曼边界条件:

$$\left. \frac{\partial V_l}{\partial \vec{n}} \right|_{\Gamma} = 0, (l=3),$$

(7)

其中 $\vec{n}$  表示沿 CNT 表面的法线方向,  $\Gamma$  表示在源/漏区处的 CNT 表面. 电流 - 电压关系可由 Landaur-Buttiker 公式得到  $^{[10,18]}$ .

#### 4 结果与讨论

计算中, 沿 CNT 径向和轴向的网格点间距分别取 0.1 nm 和 0.25 nm, 求解电荷和电流的自洽循环误差标准分别取为  $10^{-7}$  和  $10^{-3}$ ,  $\eta^+=10^{-16}$ ,  $\gamma=-3$  eV, 温度 T=300 K.

为研究 HDMG 结构如何能够改善以及可在 多大程度上改善 CNTFET 器件性能尤其是提高 电子输运效率,本文将 HDMG-CNTFET 和 SMG-CNTFET 进行对比研究,除了 HDMG-CNTFET 的 栅极采用两种不同功函数的金属之外,其余参数 均与 SMG-CNTFET 的参数相同 (如图 1 所描述). 为了方便与 SMG-CNTFET 进行定量比较, 首先固 定 HDMG-CNTFET 器件两种栅电极中的一种金 属功函数与 SMG-CNTFET 的栅极金属功函数相 同, 均等于 CNT 的功函数 WCNT (单金属栅 CNT-FET 研究中通常这样选取栅电极, 以保证平带电 压为 0), 而另外引入的一种金属栅其功函数如何 选取,哪种金属栅靠近源端一侧,哪种靠近漏端 一侧,对器件性能会有显著影响,需要仔细分析. 本文经过定性分析和定量比较, 发现令源端的金 属栅 S-gate 功函数  $W_{GS}$  等于本征 CNT 的功函数, 而适当选取漏端金属栅 D-gate 的功函数  $W_{Gd}$  的 数值, 使其在一定范围内小于 WGS, 可提高电子 输运效率,同时也能适当改善器件其他重要性能 (例如增强栅控能力,抑制短沟道效应及双极导电性 等). 本文中图 2—7 以  $W_{GS} = W_{CNT}, W_{Gd} = W_{GS} - 0.3$ eV 为例对此进行了分析;同时在图 8 中讨论了如 何合理选取 WGd 的值以有利于提高电子输运效 率. 需要强调的是, 由(6)式, 模拟过程中仅需确 定 CNT 和金属栅的功函数差值即可, 而在具体工 艺中, 需要确定 CNT 的功函数的具体值, 进而根 据功函数差确定金属栅的功函数 (CNT 的功函数  $W_{\text{CNT}} = E_g/2 + \chi = |2\gamma \cos[\text{round}(2n/3)\pi/n + \gamma]| + \chi$ (round 是取整函数, n 是手性指数,  $\chi$  是电子亲和 势), 对于手性为 (13, 0) 的 CNT,  $W_{\text{CNT}} \approx 4.51 \text{ eV}$ ).

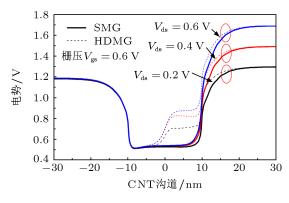

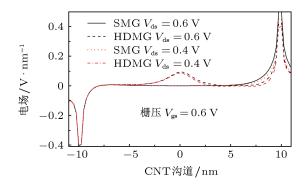

图 2 给 出 了 HDMG-CNTFET 和 SMG-CNTFET 沿沟道的电势分布. SMG-CNTFET 的沟道电势总体呈现较平缓的分布趋势; 而 HDMG-CNTFET 的沟道表面电势存在阶梯分布, 这是由于两种栅电极材料的功函数不连续造成的. 由于

$W_{GS} > W_{GD}$ , 根据 (6) 式, D-gate 金属与 CNT 的功函 数差要小于 S-gate 金属与 CNT 的功函数差, 导致 D-gate 处的沟道表面电势较高, S-gate 处的沟道表 面电势较低,表面电势的最低值位于 S-gate 下沟道 中. 由于表面电势最低值决定着器件的阈值电压, 因此, 靠近源端的金属栅 S-gate 是控制栅. 而由于 D-gate 栅其功函数  $W_{Gd} < W_{GS}$ , 右半沟道区域平带 电压为负,有效栅电压比左半沟道区大,在 D-gate 栅的调制作用下,与 SMG-CNTFET 相比 HDMG-CNTFET 器件沟道表面电势的最低值被相应拉高 (增大). 由于电势最低值越小, 器件阈值电压越大, 所以 HDMG-CNTFET 比 SMG-CNTFET 阈值电压 小,导致在相同的漏电压  $V_{ds}$  和栅电压  $V_{gs}$  的作用 下, HDMG-CNTFET 器件具有更大的漏极输出电 流, 如图 3 所示. 从这个角度来说, 新引入的 D-gate 栅起到对 CNTFET 器件沟道电势进行调整从而减 小阈值电压的作用,可称为调制栅.值得强调的是, 在已有的报道中,器件性能的改善均是以减小通态 电流为代价的[7-10], 通态电流减小将导致器件的 驱动能力降低,限制其在电路中的应用.本研究通 过引入调制栅 D-gate, 能够确保在相同的  $V_{ds}$  和  $V_{gs}$

图 2 HDMG-CNTFET 和 SMG-CNTFET 器件的沟道电势分布

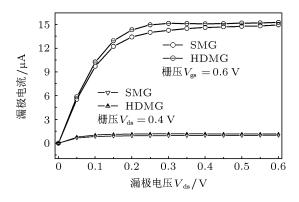

图 3 HDMG-CNTFET 和 SMG-CNTFET 器件的输出特性曲线

条件下,使 CNTFET 器件的输出电流并不减小,而是有所增加. 另一方面,HDMG-CNTFET 器件由于沟道内引入阶梯电势,随着漏偏压  $V_{\rm ds}$  的变化,增加的偏压大多降落在漏端和 D-gate 金属栅之间 (如图 2),因此 D-gate 栅又起到了屏蔽漏电压  $V_{\rm ds}$  的作用,也是屏蔽栅. 当漏偏压  $V_{\rm ds}$  增加时,整个沟道表面电势抬高,而 HDMG-CNTFET 由于 D-gate 栅对  $V_{\rm ds}$  的屏蔽作用,使其与 SMG-CNTFET 相比,电势最低点上移的幅度较小,导致  $V_{\rm gs}$  一定时,随  $V_{\rm ds}$  的增加,HDMG-CNTFET 器件的电流增加较小,因而具有较小的漏电导,如图 3 所示. 而与之相对应的 SMG-CNTFET 沟道由于没有 D-gate 栅的屏蔽,随  $V_{\rm ds}$  的增加,电势最低值上移的幅度要大于 HDMG-CNTFET 器件,因而随  $V_{\rm ds}$  增加电流增加幅度更大,即漏电导更大.

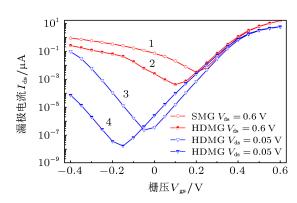

图 4 HDMG-CNTFET 和 SMG-CNTFET 器件的转移特性曲线

图 4 是 HDMG-CNTFET 和 SMG-CNTFET 的 转移特性曲线 (含  $V_{gs} < 0$ ). 由图可见, HDMG-CNTFET 器件的关断电流 ( $V_{gs} = 0$  V,  $V_{ds} = 0.6$ V) 为  $2.44 \times 10^{-3}$   $\mu$ A, 远小于 SMG-CNTFET 器 件的  $7.29 \times 10^{-2}$  μA; 而 DHMG-CNTFET 的通态  $(V_{gs} = 0.6 \text{ V}, V_{ds} = 0.6 \text{ V})$  电流为 15.36  $\mu$ A, 比 SMG-CNTFET 的通态电流 14.95 μA 要大. 使 CNTFET 器件的关断电流减小而导通电流增大的这种特性, 是掺杂工程难以实现的. 从图 4 还可看到, 随着  $V_{gs}$ 从 0 开始增加, 对于 HDMG-CNTFET 器件, 其栅电 压 - 电流曲线各点均具有比 SMG-CNTFET 更大的 斜率, 即具有更大的跨导. 从数据来看, 在  $V_{gs} = 0.4$ V 和  $V_{gs} = 0.6$  V 时, SMG-CNTFET 的跨导分别为 26.5 μS 和 95.7 μS, HDMG-CNTFET 的跨导分别为 28.7 μS 和 99.8 μS. 总之, 更大的通态电流、更小 的关断电流、更大的跨导、更小的漏电导,说明 HDMG-CNTFET 器件的栅控能力更好.

DIBL 效应是 MOS 器件短沟道效应的重要体

现,它可通过线性阈值电压和饱和阈值电压的差值即阈值漂移来衡量.本文计算线性和饱和阈值电压  $V_{ds}$  分别取为 0.05 V 和 0.6 V,而阈值电压定义为漏极电流为 1  $\mu$ A 时所需施加的栅电压.如图 4, HDMG-CNTFET 的阈值漂移为 16.4 mV,小于 SMG-CNTFET 的 20.5 mV. 阈值漂移减小的原因同漏电导类似,也可从图 2 的沟道电势变化趋势来解释:当  $V_{ds}$  增加时, HDMG-CNTFET 器件由于 D-gate 的屏蔽作用,电势最低点向上移动的幅度较小,其漂移的幅度小就决定着阈值电压漂移的幅度小.

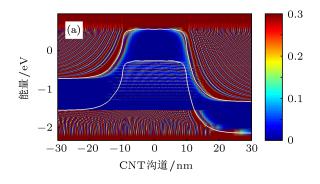

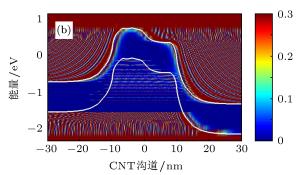

本文还对比了 SMG-CNTFET 以及 HDMG-CNTFET 的双极导电特性 (见图 4 中的  $V_{gs} < 0$  部 分的曲线). 双极导电指的是当 MOS 器件的栅源之 间施加负偏压时,漏极电流并不关断,而是随着栅 源电压  $|V_{gs}|$  的增加而增加. MOS 管的双极导电特 性在传输管以及静态随机存储器等逻辑器件中应 用时是不希望出现的, 应尽可能抑制. 双极导电性 产生的原因可通过图 5 来解释, 在较高的  $V_{ds}$  的作 用下, CNTFET 沟道中价带产生一系列不连续的线, 为分立的电子准束缚态,它们与源/漏区的导带相交 叉, 意味着价带内的准束缚态与掺杂区的源/漏电子 相耦合,形成了电子的带间隧穿.随着栅极施加更 大的负偏压  $V_{gs}$ , CNTFET 靠近源/漏端的导带 - 价 带间势垒变薄, 隧穿概率增大, 这将导致随  $|V_{\rm gs}|$  的 增加,漏极产生更大的隧穿电流.而从图 4 可见,与 SMG-CNTFET 器件相比, HDMG-CNTFET 器件双 极导电性有所减轻,这可通过对比图 5(a) 和图 5(b) 来解释, HDMG-CNTFET 通过引入屏蔽栅 D-gate, 使沟道处的价带电子与源/漏端导带电子耦合减弱, 从而使隧穿电流减小. 通过比较图 4 曲线 1,2 和曲 线 3,4 可见,双极导电特性还与漏电压 Vds 有关,随 着  $V_{ds}$  减少, 双极导电特性减弱.

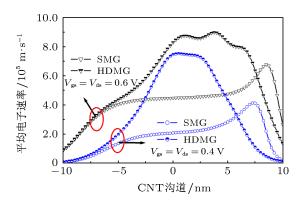

电子输运效率除了由前面提到的通态电流来反映外,主要与沟道中平均电子速率有关. 其中通态电流影响着器件的延迟时间,而平均电子速率决定着器件的特征频率. 电子速率与沿沟道方向的电场分布有关. 由于 HDMG-CNTFET 器件中引入了D-gate 栅极,两种栅电极功函数的不连续导致沟道电势的阶梯分布,使沟道电场产生明显的变化,如图 6. 主要体现在: 1) 在栅电极交界处,由于电势的急剧变化,产生一个附加沟道电场,使得在相同的  $V_{ds}$  下,沟道中部电场高于 SMG-CNTFET 器件; 2) 在靠近漏端处,电场降低,低于 SMG-CNTFET 器

件漏端的电场,有利于抑制热载流子效应.

图 5 SMG-CNTFET 和 HDMG-CNTFET 能带图,  $V_{\rm gs} = -0.4$  V,  $V_{\rm ds} = 0.6$  V (a) SMG-CNTFET 能带图; (b) HDMG-CNTFET 的能带图

图 6 HDMG-CNTFET 和 SMG-CNTFET 器件的沟道电场

HDMG-CNTFET 沟道中附加电场的产生,使沟道内载流子可以以较高的速度进入沟道,更快地达到饱和速度,有利于提高电子在器件中的平均输运速率,减小电子渡越时间. 电子输运速率根据下式计算:

$$v_i = \frac{I_{\rm ds}(V_{\rm gs}, V_{\rm ds})}{Q_i(V_{\rm gs}, V_{\rm ds})}, \tag{8}$$

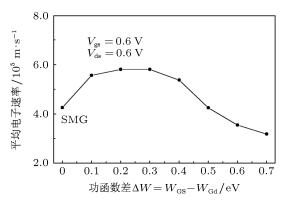

式中  $I_{ds}$  为通态电流,  $Q_i$  为沟道表面电荷密度. 由于电子速率在沟道各处不同, 平均电子速率  $\upsilon$  是将  $\upsilon_i$  在整个沟道范围内取统计平均得到, 即  $\upsilon = \langle \upsilon_i \rangle$ . 经计算, 当  $V_{gs} = 0.6$  V,  $V_{ds} = 0.6$  V 时, HDMG-CNTFET 器件的平均电子速率达到  $5.81 \times 10^5$  m/s, 比 SMG

器件的  $4.26 \times 10^5$  m/s 高出 36.5%; 当  $V_{\rm gs} = 0.4$  V,  $V_{\rm ds} = 0.4$  V 时, DMG-CNTFET 沟道平均电子速率为  $3.42 \times 10^5$  m/s, 比 SMG 器件的  $1.86 \times 10^5$  m/s 高出 83.9%, 见图 7. 与 SMG-CNTFET 相比, HDMG-CNTFET 器件平均电子输运速率增大, 从而减少了电子在沟道中的渡越时间. 而根据特征频率  $f_{\rm T}$  与沟道中平均电子速率 v 的关系  $f_{\rm T} = \frac{v}{2\pi L_{\rm ch}}(L_{\rm ch})$  为沟道长度), 当  $V_{\rm gs} = 0.6$  V,  $V_{\rm ds} = 0.6$  V 时, SMG-CNTFET 器件的特征频率为 3.39 THz, 本文的计算值与文献 [19] 的预测均在几 THz 范围, 说明了结果的合理性. 而与之相对照, HDMG-CNTFET 器件的特征频率可达 4.63 THz, 说明了 HDMG-CNTFET 相对于 SMG-CNTFET 更适合于高频应用.

图 7 HDMG-CNTFET 和 SMG-CNTFET 器件的沟道中平均 电子速率

延迟时间  $\tau$  是反映器件是否适合用作逻辑门电路的一个重要参数. 延迟时间  $\tau$  可根据下式估算:

$$\tau = \frac{Q_{\rm on} - Q_{\rm off}}{I_{\rm ds}},\tag{9}$$

其中  $I_{ds}$  表示通态电流,  $Q_{on}/Q_{off}$  表示导通态/关断状态下的总电荷, 可分别在导通/关断状态下将 (8) 式中的  $Q_i$  对坐标积分得到. 由此可见, 提高导通电流, 有利于减少器件的延迟时间. 计算表明, 当  $V_{gs}=0.6$  V,  $V_{ds}=0.6$  V 时, HDMG-CNTFET 和 SMG-CNTFET 器件的延迟时间分别为:  $9.92\times10^{-14}$  s,  $2.62\times10^{-13}$  s; 而  $V_{gs}=0.4$  V,  $V_{ds}=0.4$  V 时, 延迟时间分别为  $6.91\times10^{-13}$  s,  $9.19\times10^{-13}$  s, 说明 HDMG-CNTFET 具有更短的延迟时间, 如果利用 HDMG-CNTFET 作为门电路可比 SMG-CNTFET 门电路具有更快的速度, 因而更利于应用在高速/高频电路.

需要说明的是, 对于 HDMG-CNTFET 结构的器件, 固定控制栅 S-gate 的功函数  $W_{GS} = W_{CNT}$ , 而作为调整栅和屏蔽栅的 D-gate 其功函数  $W_{Gd}$  的选择范围是受限制的, 当超出一定范围后, 器件输运

效率会变差. 从驱动电流角度看, 如果  $W_{Gd} > W_{Gs}$ , 沟道电势最低值会出现在靠近漏端一侧的沟道区, 则 D-gate 金属栅会失去屏蔽作用, 使得与 SMG-CNTFET 相比, 沟道最低电势降低, 从而导致阈值 电压增大,此时的 HDMG-CNTFET 器件的输出电 流会小于 SMG-MOSCNT 器件; 而从平均电子输运 速率角度看,如图 8 所示,当  $\Delta W = W_{GS} - W_{Gd}$  大于 0.5 eV 以后, HDMG-CNTFET 器件电子输运速率逐 渐开始小于 SMG-CNTFET 器件的. 其原因是, 当引 入 HDMG 后, 在两种金属栅极的交界处产生附加 电场的同时,漏端电场相应减小,电子在沟道中的 运动是附加电场和漏端电场综合作用的结果. 随着 功函数差  $\Delta W = W_{GS} - W_{Gd}$  的增加 (固定  $W_{Gs}$ ), 双金 属栅交界处的电场强度增大,对源区的电子抽取更 快, 而靠近漏端的电场将减小, 对电子的抽取速度 变慢, 当  $\Delta W > 0.5$  eV 以后, 两个电场综合作用的结 果为沟道中的平均电场开始减小. 图 8 表明 ΔW 取 值在 0.1 eV 和 0.4 eV 之间时, 非常有益于提高器件 沟道中的平均电子输运速率.

图 8 不同功函数差  $\Delta W$  对 HDMG-CNTFET 器件沟道平均电子速率的影响

### 5 结论

提出了一种 HDMG 结构 CNTFET 器件,基于量子力学中的 NEGF 理论,构建了该结构器件的电子输运模型.研究表明,异质双栅结构由于栅电极功函数的不连续性可导致在 CNTFET 沟道中引入阶梯电势,对 CNTFET 沟道电场分布进行调制,在栅电极交界处的沟道中产生一个附加电场,同时使漏端附近沟道电场减小.如果固定源端金属栅的功函数 WGS 等于本征 CNT 的功函数 WCNT,而控制漏端金属栅功函数 WGd 在小于 WGS 0.1—0.4 eV 范围以内时,附加电场与漏端附近电场的综合作用使得电子在沟道中的平均输运速率较 SMG-CNTFET 器

件大幅提高,而沟道电子在达到漏极附近提前减速到一个较低的速度,有利于降低热载流子效应;靠近漏端的 D-gate 栅其功函数  $W_{Gd} < W_{GS}$ ,右半沟道区域平带电压为负,有效栅电压比左半沟道区大,对沟道电势起到调制作用,使得 HDMG-CNTFET沟道电势的最低值高于 SMG 器件中沟道电势最低值,从而确保比 SMG 器件具有更低的阈值电压,因此有更大的导通电流。所提出的 HDMG-CNTFET 器件与 SMG-CNTFET 相比还可以一定程度减小阈

值电压漂移、提高器件跨导、减小漏电导、减小关断电流、增加开关态电流比、减弱器件的双极性导电等.本研究通过合理选取 HDMG-CNTFET 栅极金属的功函数,提高了 CNTFET 器件的电子输运效率,进而提高特征频率、减小延迟时间,有利于将 CNTFET 器件应用于高速/高频电路.本研究可为优化 CNTFET 器件性能及拓展其应用起到较好的帮助作用.

- [1] Mintmire J W, Dunlap B I, White C T 1992 Phys. Rev. Lett. 68 631

- [2] Hamada N, Sawada S, Oshiyama A 1992 Phys. Rev. Lett. 68 1579

- [3] Saito R, Fujita M, Dresselhaus G, Dresselhaus M S 1992 Appl. Phys. Lett. 46 1804

- [4] Sander J T, Alwin R M V, Cees D 1998 Nature 393 49

- [5] Martel R, Schmidt T, Shea H R 1998 Appl. Phys. Lett. 73 2447

- [6] Seidel R V, Graham A P, Kretz J, Rajasekharan B, Duesberg G S, Liebau M, Unger E, Kreupl F 2005 Nano Lett. 5 147

- [7] Sébastien F, Hugues C H, Johnny G, Cristell M, Thomas Z, Jean P B, Philippe D, Sylvie G R 2008 IEEE Trans. Electron. Dev. 55 1317

- [8] Li J P, Zhang W J, Zhang Q F, Wu J L 2007 Acta Phys. Sin. 56 1054 (in Chinese) [李萍剑, 张文静, 张琦锋, 吴锦雷 2007 物理学报 56 1054]

- [9] Zahra A, Ali A O 2008 Physica E 41 196

- [10] Liu X H, Zhang J S, Wang J W, Ao Q, Wang Z, Ma Y, Li X, Wang Z S, Wang R Y 2012 Acta Phys. Sin. 61 107302 (in Chinese) [刘兴辉, 张俊松, 王绩伟, 敖强, 王震, 马迎, 李新, 王振世, 王瑞玉 2012 物理

学报 61 107302]

- [11] Ali N, Parviz K, Ali A O 2010 Superlat. Microstruct. 50 145

- [12] Ali N, Keshavarzi P 2012 Superlat. Microstruct. 52 962

- [13] Wind S J, Appenzeller J, Avouris P 2003 Phys. Rev. Lett. 91 058301

- [14] Park J Y, Rosenblatt S, Yaish Y 2004 Nano Lett. 4 517

- [15] Liang W, Bockrath M, Bozovic D, Hafner J H, Tinkham M 2001 Nature 41 665

- [16] Chen Z H, Farmer D, Xu S, Gordon, R F, Avouris P H, Appenzeller J 2008 IEEE Trans. Dev. Lett. 29 183

- [17] Guo J, Datta S, Anantram M P, Mark L 2004 J. Comput. Electron. 3 373

- [18] Fiori G, Iannaccone G, Klimeck G 2006 IEEE Trans. Electron. Dev. 53 1782

- [19] Hasan S, Salahuddin S, Vaydyanathan M, Alam M A 2005 IEEE Trans. Nanotech. 5 14

## Improvement on the electron transport efficiency of the carbon nanotube field effect transistor device by introducing heterogeneous-dual-metal-gate structure\*

Liu Xing-Hui $^{1)\dagger}$  Zhao Hong-Liang $^{1)}$  Li Tian-Yu $^{1)}$  Zhang Ren $^{1)}$  Li Song-Jie $^{1)}$  Ge Chun-Hua $^{2)}$

1) (College of Physics, Liaoning University, Shenyang 110036, China)

2) (College of Chemistry, Liaoning University, Shenyang 110036, China)

(Received 13 March 2013; revised manuscript received 2 April 2013)

#### Abstract

To improve the carbon nanotube field effect transistor (CNTFET) device performance and enhance the electron transport efficiency of the device, a heterogeneous-dual-metal-gate (HDMG)-CNTFET is proposed. By appropriately modifying the transport model for single-metal-gate (SMG)-CNTFET, the electron transport properties of the HDMG-CNTFET device are investigated. The results indicate that the work function  $W_{GS}$  of the metal gate near the source (S-gate) is fixed such that it is equal to that of the intrinsic CNT, and the work function  $W_{GG}$  of the metal gate near the drain (D-gate) is selected to be smaller than  $W_{GS}$  within a certain range, the electric field distribution can be optimised and the average electron velocity in the CNTFET channel can be significantly increased; at the same time, due to the electric potential modulation by the D-gate, the device has a lower threshold voltage. When the same operating voltage is applied, HDMG-CNTFET has a larger on-state current than SMG-CNTFT; and due to the shielding effect of the drain voltage variation by D-gate, the HDMG-CNTFET device exhibits good gate-control ability and can suppress the drain-induced barrier lower effect, hot electron effect and ambipolar conduction behavior compared with SMG-CNTFET. This study, by reasonably selecting the gate electrode work function of the HDMG-CNTFET, can effectively overcome the deficiency of existing research on improving the CNTFET performance at the expense of reducing the on-current, more importantly, can improve the electron transport efficiency, thereby improving the characteristic frequency and reducing the delay time of the device, which will be of benefit to CNTFET application in high-speed/high-frequency circuit.

Keywords: CNTFET, heterogeneous dual metal gate, electron transport efficiency, ambipolar transport property

**PACS:** 73.63.Fg, 85.35.Kt, 73.23.Ad, 73.23.—b **DOI:** 10.7498/aps.62.147308

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (Grant No. 21171081), the Natural Science Foundation of Liaonning Province, China (Grant No. 20082050), and the Liaoning Province Education Department Research Project, China (Grant No. L2010152).

$<sup>\</sup>dagger \ Corresponding \ author. \ E-mail: liuxinghuixjtu@sohu.com$