# 隧道场效应晶体管静电放电冲击特性研究\*

王源<sup>1)2)†</sup> 张立忠<sup>1)</sup> 曹健<sup>1)</sup> 陆光易<sup>1)</sup> 贾嵩<sup>1)2)</sup> 张兴<sup>1)2)</sup>

1)(北京大学微纳电子学研究院, 北京 100871)

2)(微纳电子与集成系统协同创新中心, 北京 100871)

(2014年4月11日收到; 2014年4月30日收到修改稿)

随着器件尺寸的不断减小, 集成度的逐步提高, 功耗成为了制约集成电路产业界发展的主要问题之一。由于通过引入带带隧穿机理可以实现更小的亚阈值斜率, 隧道场效应晶体管(TFET)器件已成为下一代集成电路的最具竞争力的备选器件之一。但是TFET器件更薄的栅氧化层、更短的沟道长度容易使器件局部产生高的电流密度、电场密度和热量, 使得其更容易遭受静电放电(ESD)冲击损伤。此外, TFET器件基于带带隧穿机理的全新工作原理也使得其ESD保护设计面临更多挑战。本文采用传输线脉冲的ESD测试方法深入分析了基本TFET器件在ESD冲击下器件开启、维持、泄放和击穿等过程的电流特性和工作机理。在此基础之上, 给出了一种改进型TFET抗ESD冲击器件, 通过在源端增加N型高掺杂区, 有效的调节接触势垒形状, 降低隧穿结的宽度, 从而获得更好的ESD设计窗口。

**关键词:** 隧道场效应晶体管(TFET), 静电放电(ESD), 传输线脉冲(TLP), 带带隧穿机理

**PACS:** 85.30.Mn, 85.30.Tv, 41.20.Cv, 52.35.Fp

**DOI:** 10.7498/aps.63.178501

## 1 引言

尺寸缩小理论推动着集成电路产业界不断的向前发展, 随着器件尺寸的降低, 集成度的不断提高, 功耗成为了制约集成电路产业发展的瓶颈。为了降低功耗, 突破基于漂移-扩散输运原理的传统金属-氧化物-半导体场效应晶体管(metal oxide semiconductor field effect transistor, MOSFET)在室温下60 mV/dec的亚阈值摆幅的限制, 研究者在场效应晶体管中引入了隧道效应<sup>[1-3]</sup> 并对此展开了广泛的研究, 基于硅纳米线的隧道场效应晶体管(tunnel field effect transistor, TFET)更是以其优越的性能成为下一代的集成电路的最具竞争力的备选器件之一<sup>[4-6]</sup>。对于集成电路器件而言, 从加工、封装、运输、系统集成到用户使用, 所有过程都有可能在器件管脚上产生静电泄放(electrostatic discharge, ESD)冲击现象。而且随着器件尺寸的不断减小, 诸如超薄栅氧化层、超短沟道长度、超浅结

深等先进工艺技术在提高器件性能的同时, 却造成内部电路抗ESD冲击的能力大大降低<sup>[7]</sup>。根据美国可靠性分析中心统计, 在所有电子设备的硬件故障中, ESD冲击导致的失效占15%, 而对静电高敏感度的集成电路器件这一比例高达60%<sup>[8]</sup>。因此, 针对TFET器件的ESD保护问题面临着更多的科学挑战。首先, 由于TFET器件具有更薄的栅氧化层和更短的沟道长度, 使得其ESD设计窗口更难实现。其次, 基于带带隧穿(band-to-band tunneling, BTBT)效应的新工作原理, 使得TFET器件在ESD冲击下的特性不同于传统MOSFET<sup>[9]</sup>。为此, 本文采用传输线脉冲(transmission line pulse, TLP)测试方法, 通过Synopsys公司的Sentaurus Sdevice软件, 模拟和分析了TFET器件在ESD冲击下器件开启、维持、泄放和击穿等过程的电流特性和工作机理。在此基础之上, 给出了一种改进型TFET抗ESD冲击器件, 其具有更好的开启电压和击穿电流的可控性。

\* 国家自然科学基金青年科学基金(批准号: 61106101)资助的课题。

† 通讯作者。E-mail: wangyuan@pku.edu.cn

## 2 ESD 设计窗口和 TLP 测试模型

### 2.1 ESD 设计窗口

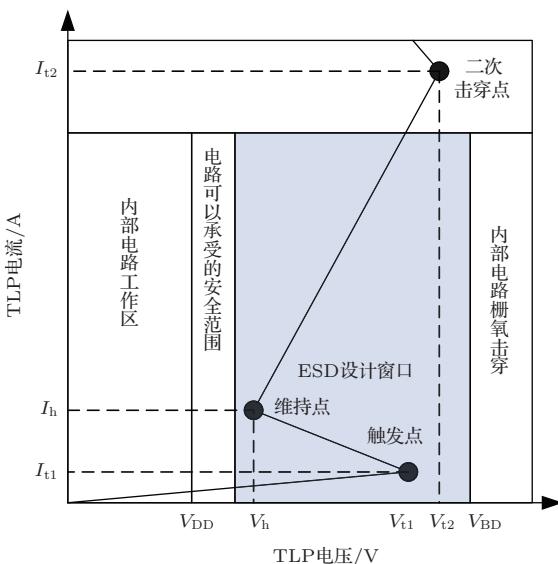

作为 ESD 保护器件设计的重要特性表征指标, ESD 设计窗口如图 1 所示, 主要参数包括: 触发电压  $V_{t1}$  和电流  $I_{t1}$ 、维持电压  $V_h$  和电流  $I_h$ 、二次击穿电压  $V_{t2}$  和电流  $I_{t2}$ 。触发电压  $V_{t1}$  决定了器件在 ESD 冲击下开始工作的初始条件。过低的  $V_{t1}$  容易导致器件发生 ESD 误触发, 影响内部电路正常工作; 过高的  $V_{t1}$  会导致器件在 ESD 冲击来临时无法及时开启泄放 ESD 电荷, 造成内部电路损伤。通常  $V_{t1}$  必须设置在电源电压  $V_{DD}$  和器件栅氧化层击穿电压  $V_{BD}$  之间。维持电压  $V_h$  决定了器件在泄放 ESD 电荷的大电流特性。过低的  $V_h$  容易导致器件发生闩锁效应(latch up); 过高的  $V_h$  会导致泄放过程产生的功耗过大, 提早二次击穿。通常  $V_h$  必须设置在  $V_{DD}$  和  $V_{t1}$  之间。二次击穿电流  $I_{t2}$  决定了器件在 ESD 冲击下能够承受的最大冲击电压, 称为 ESD 阈值电压。通用工业标准人体模型(human body model, HBM)抗 ESD 冲击的 ESD 阈值电压计算方式是  $I_{t2} \times 1500 \Omega$ 。通常 HBM 测试模型下 ESD 阈值电压达到 2 kV 是工业界对集成电路芯片产品可靠性的基本要求。随着集成电路进入纳米时代, MOSFET 的栅氧化层变得很薄, 栅氧化层击穿电压  $V_{BD}$  越来越小, 逐渐接近电源电压  $V_{DD}$ , ESD 设计窗口越来越小<sup>[10]</sup>。

图 1 ESD 设计窗口

### 2.2 TLP 测试模型

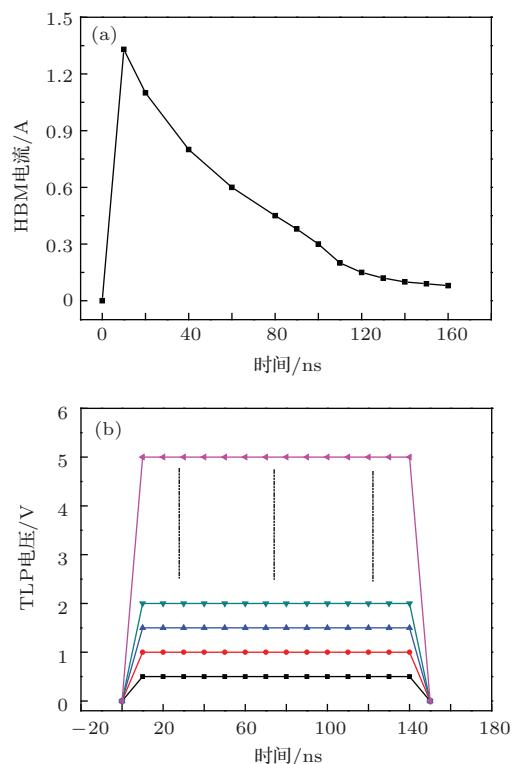

HBM 冲击模型模拟的是带电人体接触半导体器件所造成的 ESD 冲击过程, 通常用一个 100 pF 的电容串联一个 1500 Ω 的电阻来等效。其等效脉冲波形如图 2(a) 所示。HBM 模型的 ESD 冲击会对器件造成不可恢复的损伤。相对而言, TLP 则是一种无损的等效 ESD 冲击测试, 可以准确获得器件的 ESD 特性参数, 如触发点、维持点和二次击穿点的电压、电流等。TLP 测试的基本原理是: 首先, 通过等效电路在大电容  $C_{TLP}$  下生成一个低压  $V_{TLP}$  脉冲方波, 并保持脉冲产生的总电荷量  $Q_{TLP}(= C_{TLP} \times V_{TLP})$  与该时间段 HBM 模型对应的电荷  $Q_{HBM}$  相同, 如图 2(b) 所示。然后, 将脉冲方波施加在待测器件上, 记录待测器件的电压 - 时间值和电流 - 时间值, 并通过不断加大 TLP 脉冲产生电荷量  $Q_{TLP}$  来模拟 HBM 模型的冲击曲线。最后, 将相同时间点的电流值和电压值拟合, 转化成以电压为横坐标、以电流为纵坐标的等效电流 - 电压 ( $I-V$ ) 曲线, 即 TLP 曲线。HBM 冲击模型的等效 TLP 脉冲宽度为 150 ns, 脉冲上升时间为 10 ns。

图 2 ESD 冲击模型脉冲波形示意图 (a) HBM 模型;

(b) TLP 模型

### 3 带带隧穿(BTBT)物理模型

1961年Kane利用微扰理论推导出了局部的带带隧穿效应模型<sup>[11]</sup>。该模型中隧穿复合率 $R_{\text{BTBT}}$ 表示为

$$R_{\text{BTBT}} = A \cdot E^P \exp\left(-\frac{B}{E}\right), \quad (1)$$

其中,  $E$ 为电场强度,  $A$ ,  $B$ ,  $P$ 均为拟合因子, 模型中隧穿复合率的大小仅取决于局部电场的大小。Kane的带带隧穿模型是一个简化的数学模型, 虽然数值求解简单, 但是并未充分考虑隧穿效应对于载流子复合率的影响。于是, Hurkx等对于Kane模型进行了修正<sup>[12]</sup>:

$$R_{\text{BTBT}} = A \cdot D \cdot E^P \exp\left(-\frac{B}{E}\right), \quad (2)$$

其中,  $D$ 是带带隧穿效应的净产生因子:

$$D = \frac{np - n_{i,\text{eff}}^2}{(n + n_{i,\text{eff}})(p + n_{i,\text{eff}})}, \quad (3)$$

其中,  $n$ ,  $p$ 分别是电子和空穴载流子浓度,  $n_{i,\text{eff}}$ 是有效的本征载流子浓度。 $np < n_{i,\text{eff}}^2$ 表示带带隧穿过程中载流子的产生,  $np > n_{i,\text{eff}}^2$ 表示带带隧穿过程中载流子的复合。虽然Hurkx模型考虑了载流子的复合, 但是依旧是一个局部模型<sup>[13]</sup>。类似的局部模型还有Schenk模型<sup>[14]</sup>。在局部模型中, 载流子隧穿的势垒被假设为三角形, 如图3(a)所示。很明显可以看出, 在整个隧穿路径上电场强度 $E$ 和禁带宽度 $E_g$ 均是个常数。但是, 实际情况却如图3(b)所示, 在隧穿路径上的电场强度 $E$ 都在变化, 每个点都有可能不同<sup>[14–16]</sup>, 而且器件在隧穿区域内禁带宽度 $E_g$ 是常量这一假设也不成立。此外, 基于带带隧穿机理的载流子产生复合率不仅取决于隧穿概率, 同时也取决于隧穿结两侧载流子的浓度, 并且载流子带带隧穿的计算不应该对模拟器中器件网格划分的形状及疏密度过于敏感, 这都是上述模型所欠缺的<sup>[15]</sup>。因此, Sentaurus Sdevice软件在带带隧穿模型中, 除了提供前述的Hurkx, Schenk等局部模型之外, 还提供了两种非局部模型: 一种是非局部网格(non-local mesh)模型, 应用于不同材料交界面或不同掺杂区接触形成的pn结处隧穿电流的产生和计算, 采用的是隧道电流计算模型; 另一种是动态非局部路径(dynamic non-local path)模型<sup>[17]</sup>, 根据隧穿路径两侧能带弯曲程度判断电子带带隧穿的产生。ESD冲击是一个瞬时大电流

过程, 这使得器件发生隧穿的位置不仅仅出现在不同材料界面处或是不同掺杂区接触形成的pn结处, 同一种材料、同一区域不同位置的两点同样也存在着由于电场的作用促使能带弯曲而发生电子带带隧穿的可能。相较仅在界面或接触结处使用非局部网格模型的方法, 使用动态非局部路径模型可以根据隧穿路径两侧能带弯曲程度来判断此处是否发生载流子的带带隧穿, 这更符合ESD冲击下器件发生带带隧穿的机理。为了便于理解, Sentaurus Sdevice软件中对动态非局部路径模型进行了化简, 可以得到类似(1)式的表达式:

$$R_{\text{BTBT}} = A \cdot \left(\frac{F}{F_0}\right)^P \exp\left(-\frac{B}{F}\right), \quad (4)$$

其中,  $F_0 = 1 \text{ V/cm}$ 。对于直接带带隧穿  $P = 2$ , 声子辅助带带隧穿  $P = 2.5$ 。由于硅(Si)材料是间接带隙半导体, 因此, 我们选取  $P = 2.5$ 。拟合系数  $A$  和  $B$  表示为

$$A = \frac{g(m_c m_v)^{3/2} [1 + N_{\text{op}}] D_{\text{op}}^2 (q F_0)^{5/2}}{2^{21/4} h^{5/2} m_r^{21/4} \rho \varepsilon_{\text{op}} [E_g + \Delta_c]^{7/4}},$$

$$B = \frac{2^{7/2} \pi m_r^{1/2} [E_g + \Delta_c]^{3/2}}{3 q h}, \quad (5)$$

其中,  $g$ 为简并系数,  $q$ 为单位电子电量,  $h$ 是普朗克常数,  $E_g$ 是禁带宽度,  $m_r$ 是简化隧道质量,  $m_c/m_v$ 分别是导带/价带态密度有效质量,  $N_{\text{op}}$ 是横向光学声子数,  $D_{\text{op}}$ 是横向光学声子的畸变势,  $\varepsilon_{\text{op}}$ 是横向光学声子能量,  $\rho$ 是质量密度,  $\Delta_c$ 是导带带阶。

图3 带带隧穿模型 (a) 局部模型; (b) 非局部模型

当TFET器件受到ESD冲击时的隧穿机理与正常工作时是有所不同的: 首先, 在触发, 维持, 泄放和二次击穿的不同阶段电场强度会发生急剧的变化; 其次, 漏极和栅极氧化层之间因强电场的作用, 能带会发生弯曲, 存在产生栅极隧穿电流的可能; 最后, 器件内部局部电场的变动会导致电子隧穿位置的改变, 局部电场的增强, 进一步引起电子隧穿程度的加深。动态非局部路径模型可以有效地

识别变化电场引起的能带弯曲,从而判断电子隧穿的出现,而在绝缘栅氧化层位置处又可以根据能带弯曲来判断是否存在体硅与绝缘介质层之间的电子隧穿。因此,最终我们选取了动态非局部路径模型进行模拟和分析TFET器件在ESD冲击时发生带带隧穿现象。

#### 4 基本TFET器件TLP模型ESD特性

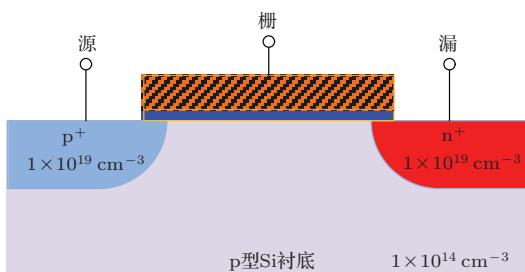

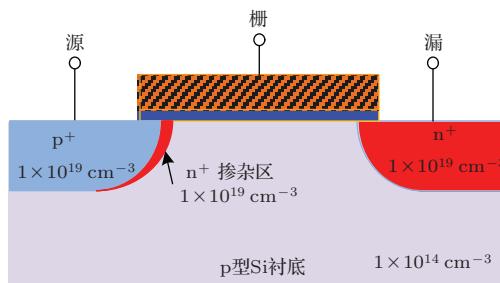

基本TFET器件结构是一个栅控的p-i-n结构,如图4所示。器件参数为:器件栅长 $L_G$ 为100 nm,栅氧化层厚度 $t_{ox}$ 为2 nm,源区 $p^+$ 和漏区 $n^+$ 的掺杂浓度均为 $1 \times 10^{19} \text{ cm}^{-3}$ , p型Si衬底(本征i区)的掺杂浓度为 $1 \times 10^{14} \text{ cm}^{-3}$ 。栅-源电压 $V_{GS}$ 为零时,处于截止状态。虽然漏-源电压 $V_{DS}$ 在沟道区(即本征i区)施加了均匀分布的横向电场,但由于源区与沟道接触处势垒的存在阻止了电流的横向流动。 $V_{GS} > 0$ 时,栅极施加的纵向电场会引起沟道能带弯曲,改变源区与沟道接触势垒的形状,降低隧穿结的宽度。在 $V_{DS}$ 施加的横向电场作用下,发生隧道击穿现象,形成漏-源电流 $I_{DS}$ 。

图4 (网刊彩色) 基本TFET管结构剖面图

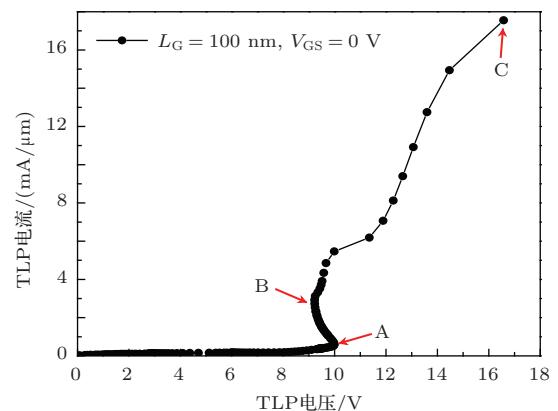

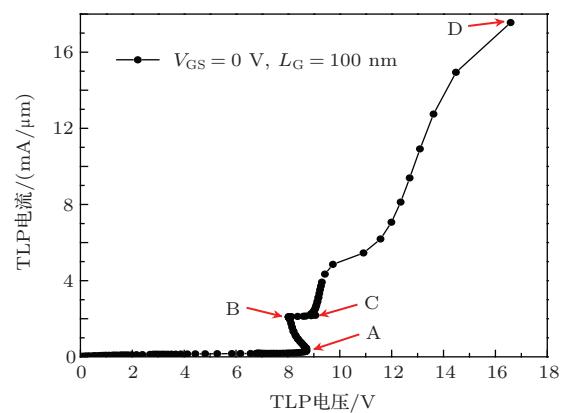

栅接地的MOSFET(gate-ground MOSFET, ggMOS)是传统MOSFET中使用最广泛的ESD保护结构<sup>[18,19]</sup>。因此,我们首先考察了栅接地的基本TFET器件的TLP模型ESD特性,如图5所示。A, B, C三个点分别代表TFET器件在ESD冲击时触发、维持和二次击穿状态。从图中可以看到,器件在A点处被触发开启,触发电压 $V_{t1}$ 约为10 V。随后器件进入回滞(snapback)负阻区,此时电流上升的同时电压下降。电压降至B点时停止,即维持态,维持电压 $V_h$ 约为9.4 V。之后器件进入大电流泄放区,电流随着电压指数型增加。直到电流上升到C点,器件晶格温度达到硅材料的熔点,标志着器件

热失效,即单位宽度的二次击穿电流密度 $I_{t2}$ 约为18 mA/ $\mu\text{m}$ 。

图5 基本TFET器件TLP特性

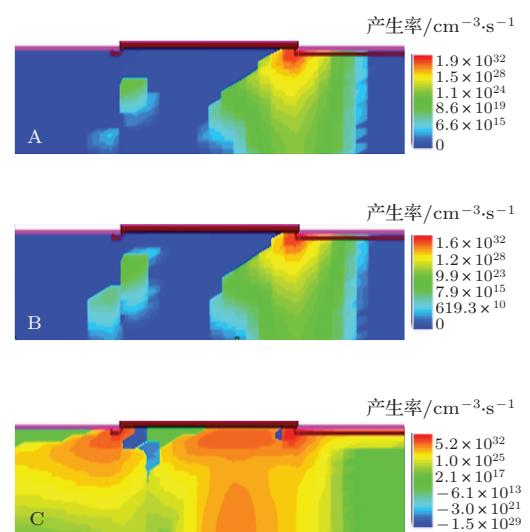

为了进一步了解基本TFET器件在TLP下的内部工作机理,图6给出了A, B, C三个点的带带隧穿电子产生的分布图。在A点处,器件在TLP模式ESD冲击下开启,除了漏区,源区的电子隧穿首先发生在栅极靠近漏区的位置,这是因为在器件开启之前该区域的电场强度要高于源区底部。器件开启之后,器件进入负阻态。电压降至维持态的B点后,进一步的电子隧穿发生在源区底部。此时出现了两处隧穿结,在这之后随着电流的上升电压也在不断上升,最后电流到达了发生二次击穿的C点。源极区域已发生了大面积的隧穿,而且漏极的电子隧穿位置也大面积的向源区扩展,这也有助于获得更高的二次击穿电流。

图6 (网刊彩色) 基本TFET器件TLP模型ESD冲击下电子隧穿产生分布图

## 5 改进型 TFET 器件 TLP 模型 ESD 特性

基本 TFET 器件的源区隧穿结是由 p<sup>+</sup>掺杂的源区和低掺杂的 p 型 Si 衬底构成, 隧穿结较宽, 触发电压  $V_{t1}$  较大。当 TFET 器件尺寸缩小时, 过大的  $V_{t1}$  有可能导致栅氧化层的提前击穿。为了获得更好的 ESD 设计窗口, 需要降低  $V_{t1}$ , 对于 TFET 器件可以通过降低隧穿结的宽度来实现。本文给出了一种改进型的 TFET 器件, 如图 7 所示, 在基本 TFET 器件的 p<sup>+</sup>源区与沟道接触位置加入局部 n<sup>+</sup>掺杂区 (n<sup>+</sup> pocket) 这样可以有效的调节接触势垒的形状, 降低隧穿结的宽度, 从而降低触发电压。

图 7 (网刊彩色) 改进型 TFET ESD 器件结构示意图

### 5.1 栅接地时改进 TFET 器件的 ESD 特性

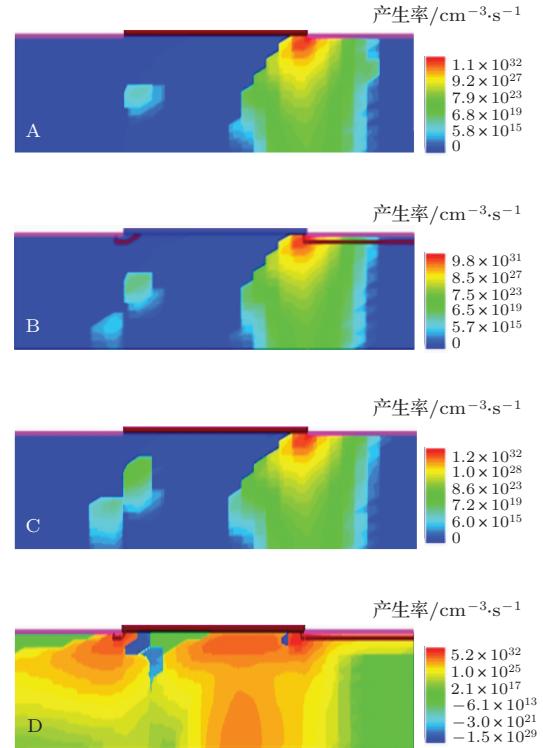

首先, 我们考察改进型 TFET 器件在栅接地时 ESD 特性。改进型 TFET ESD 器件的 n<sup>+</sup> pocket 区掺杂浓度为  $1 \times 10^{19} \text{ cm}^{-3}$ , 宽度为 4 nm。器件的栅长  $L_G$  为 100 nm 时 TLP 模型的 ESD 特性曲线如图 8 所示。A 点为触发点, 触发电压  $V_{t1}$  为 8.7 V, 比基本 TFET ESD 器件低了 1.3 V。器件随后进入回滞负阻区, B 点的维持电压  $V_h$  约为 8 V。与基本 TFET 器件不同的是, 随之器件进入了一个电流饱和区, 在电压上升到 9 V(C 点)之前, 电流保持不变。最后器件进入大电流泄放区, 电流随着电压指数型增加, 直到电流上升到二次击穿失效的 D 点。

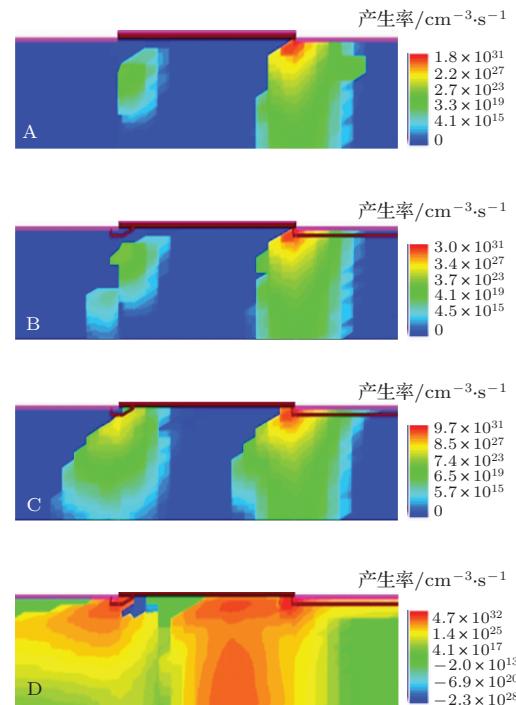

改进型 TFET 器件在 ESD 冲击下的电子隧穿产生分布图如图 9 所示。A 点分布图可以看出在新型 TFET 器件开启时首先在 n<sup>+</sup> pocket 区处发生隧穿, 因此所需的隧穿电压降低, TLP 模型 ESD 冲击下器件触发电压也随之降低。B 点分布图可以看到随

着电压的增加, 源区衬底位置处也逐渐出现电子隧穿, 但隧穿的程度较弱。当电压升至 C 点, 源区衬底位置处电子隧穿很明显, 这之后电压随着电流上升而快速增加, 直到到达二次击穿的 D 点。

图 8 改进型 TFET ESD 器件的 TLP 特性

图 9 (网刊彩色) 改进型 TFET 器件 TLP 模型 ESD 冲击下电子隧穿产生分布图

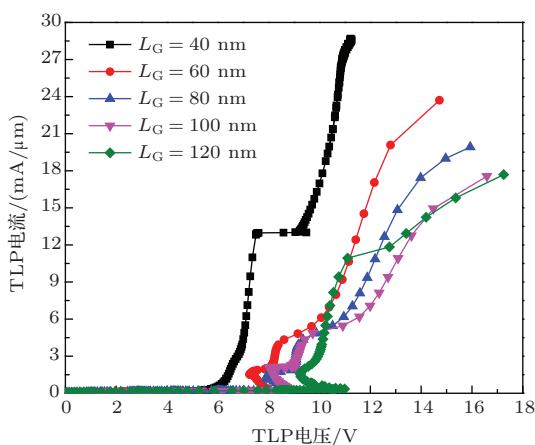

改进型 TFET 器件 TLP 模型 ESD 特性随栅长  $L_G$  的变化如图 10 所示。从仿真结果中可以看到随着  $L_G$  的逐渐减小, 触发电压逐渐减小, 二次击穿电流  $I_{t2}$  逐渐增大 (18—28 mA/μm)。对于不同栅长, 器件 TLP 特性中的 BC 段的电流饱和区形状及长度也有所不同。当  $L_G$  较大时 (120 nm), 器件的 TLP 特性并没有明显的 BC 段电流饱和区, 这是由

于4 nm的n<sup>+</sup> pocket区对在长沟道TFET器件的开启作用并不明显, 漏区产生的等效电压大部分落在本征区, 在n<sup>+</sup> pocket源极隧穿结电压降相对较小, 导致其位置的隧穿作用减弱, ESD特性与常规TFET相近。随着L<sub>G</sub>的不断减小(100 nm, 80 nm, 60 nm), BC段电流饱和效应明显, 且长度相近, 这是由于器件栅长适当的情况下, 在n<sup>+</sup>pocket势垒区隧穿电压降能很好地将势垒结隧穿, 隧穿电流增大到一定程度后就不再随着隧穿结电压降微弱的改变而改变, 隧穿电流几乎保持不变。当L<sub>G</sub>下降至40 nm时, 在TLP模型下漏极区的等效电压更多的降落在n<sup>+</sup> pocket隧穿结, 导致隧穿电流急剧增加, BC电流饱和区的电流值要高于长沟道器件。

图10 (网刊彩色) 改进型TFET器件TLP模型ESD特性随栅长L<sub>G</sub>的变化

## 5.2 正栅压时改进TFET器件的ESD特性

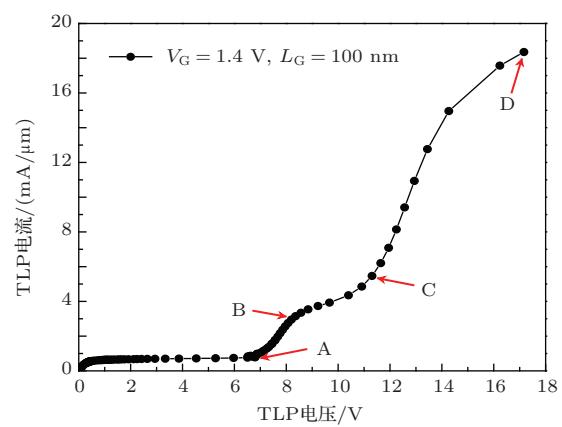

为了进一步降低器件的触发电压, 我们可以采用在TFET ESD器件的栅极施加正向偏压的方式。当栅-源电压V<sub>GS</sub>为1.4 V时, 器件的TLP特性如图11所示: V<sub>GS</sub>辅助隧穿使得器件迅速开启, 当TLP电压在0.1 V附近时电流就迅速已增至1 mA/μm, 随后电压继续增加而电流基本保持不变, 直至A点; 然后电流随着电压的增加而急剧上升, 直至B点; 随后电流随电压的增长速度变缓, 直至C点; 最后电流又随着电压的增加而快速增加, 直到器件发生二次击穿, 即D点。

图12给出了正栅压时改进型TFET器件在ESD冲击时电子带带隧穿产生分布图。在栅极施加电压的情况下电子隧穿的位置在更加的靠近栅极沟道处, 栅极施加电压将辅助栅极以下沟道电子

隧穿的产生, TLP电压很小的情况下就可以产生相对较大的隧穿电流, 即A点所示。随后, 电流随电压急剧增加, B点处可以看到源区靠近衬底一侧出现电子隧穿, 即两个位置发生电子隧穿, 从A到B的过程中可以分析得衬底逐渐发生电子隧穿使得电流随电压的增长速度逐渐增加。到达B点后, 增长速度放缓, 源区隧穿结的面积在扩大, 且倾向于源极附近的沟道处, 如C点所示。最后阶段, 电子隧穿的程度加深, 源区电子隧穿的位置更加的接近源端接触孔, 而漏区隧穿的位置也大面积向源区扩散, 泄放电流达到二次击穿点, 即D点。

图11 正栅压改进型TFET器件的TLP模型ESD特性

图12 (网刊彩色) 正栅压时改进型TFET器件ESD冲击下电子隧穿产生分布图

## 6 结 论

由于通过引入带带隧穿机理可以实现更小的亚阈值斜率, TFET器件已成为下一代集成电路的最具竞争力的备选器件之一。由于TFET器件具有更薄的栅氧化层、更短的沟道长度和全新的工作原理, 其ESD保护问题面临着更多的科学挑战。本文深入分析了基本TFET器件在TLP模型ESD冲击下器件开启、维持、泄放和击穿等过程的电流特性和工作机理。在此基础之上, 给出了一种改进型TFET抗ESD冲击器件。通过在源端增加n<sup>+</sup> pocket区, 有效的调节接触势垒形状, 降低隧穿结的宽度, 从而降低触发电压。同时, 通过调节器件栅压, 获得可调节的触发电压和更高的二次击穿电流, 使之具有更好的ESD设计窗口。

## 参考文献

- [1] Wang P F, Hilsenbeck K, Nirschl T, Oswald M, Stepper C, Weis M, Schmitt-Landsiedel D, Hansch W 2004 *Solid State Electron.* **48** 2281

- [2] Bhuwalka K K, Schulze J, Eisele I 2004 *Jpn. J. Appl. Phys.* **43** 4073

- [3] Appenzeller J, Lin Y M, Knoch J, Avouris Ph 2004 *Phys. Rev. Lett.* **93** 196805

- [4] Uenmura T, Baba T 1996 *Jpn. J. Appl. Phys.* **35** 1668

- [5] Choi W Y, Park B G, Lee J. D, Liu T J K 2007 *IEEE Electron Dev. Lett.* **28** 743

- [6] Mantl S, Knoll L, Schmidt M, Richter S, Nichau A, Trelenkamp S, Schafer A, Wirths S, Blaeser S, Buca D, Zhao Q T 2013 14<sup>th</sup> International Conference on Ultimate Integration on Silicon (ULIS) Coventry, United Kingdom, March 19-21, 2013, p15

- [7] Wang Y, Jia S, Sun L, Zhang G G, Zhang X, Ji L 2007 *Acta Phys. Sin.* **56** 7242 (in Chinese) [王源, 贾嵩, 孙磊, 张钢刚, 张兴 2007 物理学报 **56** 7242]

- [8] Wang A Z 2002 *On-chip ESD protection for integrated circuits: an IC design perspective* (Boston: Kluwer Academic) p2-7

- [9] Woo R 2009 *Ph. D. Dissertation* (California: Stanford University)

- [10] Russ C 2008 *Microelectron. Reliab.* **48** 1403

- [11] Kane E O 1961 *J Appl Phys* **32** 83

- [12] Hurkx G A M, Klaassen D B M, Knuvers M P G 1992 *IEEE Tran. Electron Dev.* **39** 331

- [13] Schenk A 1993 *Solid State Electron.* **36** 19

- [14] Biswas A, Dan S S, Royer C L, Grabinski W, Ionescu A M 2012 *Microelectron. Eng.* **98** 334

- [15] Shen C, Yang L T, Samudra G, Yeo Y C 2011 *Solid State Electron.* **57** 23

- [16] Jiao Y P, Wei K L, Wang T H, Du G, Liu X Y 2013 *J. Semiconductor.* **34** 092002

- [17] Synopsys Corp 2010 *Sentaurus Device User Guide*. Ver. E-201012

- [18] Wu X P, Yang Y T, Gao H X, Dong G, Chai C C 2013 *Acta Phys. Sin.* **62** 047203 (in Chinese) [吴晓鹏, 杨银堂, 高海霞, 董刚, 柴常春 2013 物理学报 **62** 047203]

- [19] Zhang B, Chai C C, Yang Y T 2010 *Acta Phys. Sin.* **59** 8063 (in Chinese) [张冰, 柴常春, 杨银堂 2010 物理学报 **59** 8063]

# Research on electrostatic discharge characteristics of tunnel field effect transistors<sup>\*</sup>

Wang Yuan<sup>1)2)†</sup> Zhang Li-Zhong<sup>1)</sup> Cao Jian<sup>1)</sup> Lu Guang-Yi<sup>1)</sup>

Jia Song<sup>1)2)</sup> Zhang Xing<sup>1)2)</sup>

1) (Institute of Microelectronics, Peking University, Beijing 100871, China)

2) (Innovation Center for MicroNanoelectronics and Integrated System, Beijing 100871, China)

(Received 11 April 2014; revised manuscript received 30 April 2014)

## Abstract

Power consumption has been the major bottleneck in the development of integrated circuits with reduced critical dimensions and improved integrated level. Tunnel field effect transistor (TFET) has been investigated as one of the promising replacements for traditional metal oxide semiconductor field effect transistor (MOSFET), owing to the introduction of band to band tunneling (BTBT) mechanism based on which a smaller subthreshold slope is achieved. However, a thinner oxide layer and a shorter channel length in TFET may induce localization of high current density, high electrical field distribution, and generation of heat, which abate the probability to survive electrostatic discharge (ESD). Besides, the novel BTBT operating principles also present a challenge to TFET ESD protection design. In this paper transmission line pulse test method is adopted to analyze the working principle of conventional TFET at onset, holding, discharge, and second breakdown during an ESD event. Based on these a new TFET ESD device protection design is proposed and characterized with a deeply doped n<sup>+</sup> pocket near the source region beneath the gate, which can make effective adjustments of contact potential barrier, reduce tunneling junction width, thus better ESD design windows are obtained.

**Keywords:** tunnel field Effect transistor (TFET), electrostatic discharge (ESD), transmission line pulse (TLP), band-to-band tunneling

**PACS:** 85.30.Mn, 85.30.Tv, 41.20.Cv, 52.35.Fp

**DOI:** 10.7498/aps.63.178501

\* Project supported by the Young Scientists Fund of the National Natural Science Foundation of China (Grant No. 61106101).

† Corresponding author. E-mail: wangyuan@pku.edu.cn