# 表面离子阱的衬底效应模型研究及 新型离子阱设计

张见<sup>1)</sup> 陈书明<sup>1)2)†</sup> 刘威<sup>1)</sup>

1)(国防科学与技术大学计算机学院, 长沙 410073)

2)(国防科学与技术大学并行与分步处理重点实验室, 长沙 410073)

(2013年10月14日收到; 2013年10月30日收到修改稿)

通过分析表面离子阱衬底的功率损失和电势损失对离子阱阱深和离子加热速率的影响, 提出考虑衬底效应的阱深和离子加热速率的解析分析模型。研究发现, 硅基衬底的电势损失对表面离子阱阱深的降幅达17.19%, 功率损失对离子加热速率的加速达13.37%。为了降低衬底效应的不利影响, 设计了衬底真空隔离结构的表面离子阱, 在离子阱射频电极和直流电极间的衬底表面刻蚀出多条隔离槽, 从而减小衬底的等效电导和等效电容, 达到降低衬底功率和电势损失的目的。模拟结果显示, 相比于一般结构, 真空隔离结构的硅基表面离子阱能够使阱深加深20.22%, 使衬底功率损失降低54.55%。

**关键词:** 表面离子阱, 功率损失, 电势损失, 离子加热

**PACS:** 03.67.Lx, 37.10.Ty, 41.20.-q

**DOI:** 10.7498/aps.63.060303

## 1 引言

目前, 离子阱已经成为实现量子计算的优势方案之一<sup>[1–3]</sup>。Cirac和Zoller<sup>[1]</sup>首次提出经典的线性离子阱结构, 但是, 线性阱难以扩展和大规模集成。表面离子阱芯片方案可以减轻这些缺点, 因此得到了学术界和产业界越来越多的关注。表面离子阱芯片分为单层芯片和多层芯片, 其中单层芯片因为结构简单、易于加工而表现出更好的可扩展性<sup>[4–8]</sup>。

势阱深度和离子加热速率是衡量表面离子阱囚禁稳定性的重要指标。对离子加热速率的现有研究仅考虑势阱高度、离子振动频率的影响<sup>[9–10]</sup>, 提出的离子加热速率解析模型中, 并没有考虑施加在射频(RF)电极上的交变电压的影响。实际上, 在RF电极施加交变电压后, 会有微弱的电流通过衬底, 这些电流在衬底上产生的功率损失会使RF电极的温度升高, 且交变电压的幅值越大温度越高,

温度的升高会引起RF电极上的电压涨落谱密度的变化, 从而导致离子加热速率的增大。本文在考虑电压幅值对RF电极温度的影响后, 重新修正了离子加热速率的解析模型, 使预测结果更加精确。

对于势阱深度, 现有研究主要考虑表面电极尺寸和交变电压幅值的影响<sup>[9]</sup>, 却忽略了衬底耦合电容引起的电势损失对势阱深度的影响。本文提出的表面离子阱阱深的解析模型, 同时考虑了囚禁离子的质量和电荷量、交变电压幅值、衬底电势损失、表面电极绝对尺寸和相对尺寸的影响, 发现恒压缩小电极尺寸和全比例缩小电极尺寸时的阱深变化规律, 并解释了不同衬底材料的表面离子阱阱深的差异。

为了研究衬底的功率损失和电势损失对单层表面离子阱的离子加热速率和势阱深度的影响, 首先需要获得功率损失和电势损失的解析模型。在文献[11]中, 使用等效电路模型研究了双层表面离子阱的热功率损失。类似地, 单层表面离子阱的功率损失和电势损失也可以使用等效电路建模。因

† 通讯作者。E-mail: smchen@163.com

为单层表面离子阱和微波电路在电学特性上有许多相似之处, 所以本文借鉴了用于研究微波电路的“quasi-TEM”模型<sup>[12,13]</sup>的思想, 提出单层表面离子阱的等效电路模型, 得到其功率损失和电势损失的解析表达式.

为了提高囚禁稳定性, 现有表面离子阱芯片大都使用损耗角较低的材料作为衬底. 例如, Ulm 大学采用 BOROFLOAT®33 硼硅酸盐玻璃作为表面离子阱的衬底材料<sup>[14]</sup>, Innsbruck 小组<sup>[15]</sup>使用氮化铝 (AlN) 陶瓷和 Al<sub>2</sub>O<sub>3</sub> 作为表面离子阱的衬底材料. 但是, 玻璃和陶瓷衬底存在诸如机械强度低、高电压承受力弱以及与现有工艺不兼容等缺点, 因此, 如何进一步降低硅基衬底的不利影响, 依然是研究制造表面离子阱的重点. 本文提出真空隔离结构 (vacuum trench insulation structure, VTIS) 的单层表面离子阱, 该结构通过在衬底表面刻蚀多条真空隔离槽, 减小衬底的等效电导和耦合电容, 达到降低衬底的功率损失和电势损失的目的, 从而提高表面离子阱的囚禁稳定性. 为了验证 VTIS 衬底对减小功率损失和电势损失的作用, 本文使用 Ansoft Maxwell 电磁场模拟软件, 模拟分析和对比不同衬底材料的一般表面离子阱结构 (normal structure, NS) 和 VTIS 结构的阱深

和衬底功率损失, 选择的衬底材料有硅-二氧化硅 (silicon-silicon\_dioxide, Si-SiO<sub>2</sub>) 衬底、多孔硅-氧化多孔硅 (porous\_silicon-porous\_silica, PS-PSO) 衬底和玻璃衬底.

## 2 衬底的功率损失与电势损失

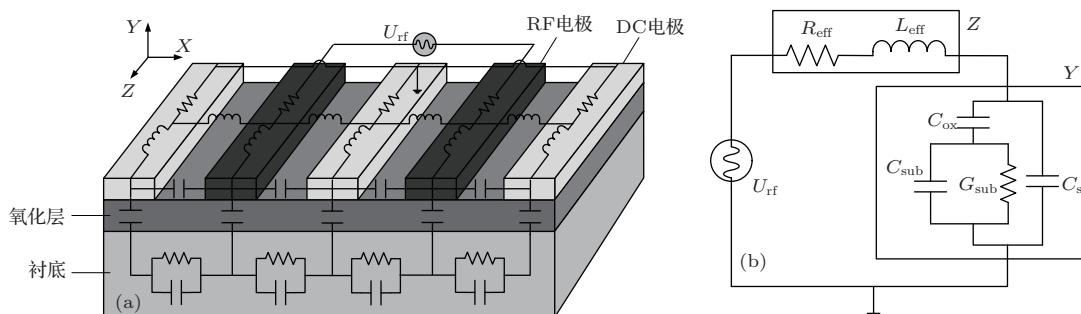

为了研究衬底的功率损失和电势损失, 本文提出使用特征参数——电阻、电感、电导和电容描述的五线表面离子阱的等效电路模型. 图 1(a) 是五线表面离子阱的寄生参数分布, 图中深色电极是 RF 电极, 浅色电极是直流 (DC) 电极, 衬底表面是一层氧化层. RF 电极和 DC 电极可以用集总电阻、电容和电感描述, 衬底可以用电导和电容描述. 简化电路后得到一般等效电路模型, 如图 1(b) 所示, 它包括阻抗  $Z$  和导纳  $Y$  两部分. 在阻抗  $Z$  中,  $R_{\text{eff}}$  是电路等效总电阻, 包括 RF 电极和 DC 电极的电阻;  $L_{\text{eff}}$  是电路等效总电感, 包括 RF 电极和 DC 电极的自感以及它们之间的互感. 在导纳  $Y$  中,  $C_{\text{ox}}$  是电极与衬底之间的氧化阻绝层总电容,  $C_s$  是 RF 电极侧壁与 DC 电极侧壁之间的平行板电容,  $C_{\text{sub}}$  是 RF 电极与 DC 电极之间的衬底耦合电容,  $G_{\text{sub}}$  是衬底的等效电导.

图 1 表面离子阱的等效电路模型 (a) 表面离子阱电学寄生参数分布; (b) 表面离子阱等效电路

在等效电路模型中, 阻抗  $Z$  和导纳  $Y$  的表达式如下:

$$Z = R_{\text{eff}} + j\omega L_{\text{eff}}, \quad (1a)$$

$$Y = G_{\text{eff}} + j\omega C_{\text{eff}}, \quad (1b)$$

其中,  $G_{\text{eff}}$  和  $C_{\text{eff}}$  是  $C_{\text{ox}}$ ,  $C_{\text{sub}}$ ,  $C_s$  和  $G_{\text{sub}}$  组成的电路的等效电导和电纳,  $\omega$  是 RF 电极上施加的交变电压的角频率. 化简电路可得

$$G_{\text{eff}} = \frac{\omega^2 C_{\text{ox}}^2 G_{\text{sub}}}{G_{\text{sub}}^2 + \omega^2 (C_{\text{ox}} + C_{\text{sub}})^2}, \quad (2a)$$

$$C_{\text{eff}} = \frac{C_{\text{ox}} G_{\text{sub}}^2 + \omega^2 C_{\text{ox}} C_{\text{sub}} (C_{\text{ox}} + C_{\text{sub}})}{G_{\text{sub}}^2 + \omega^2 (C_{\text{ox}} + C_{\text{sub}})^2} + C_s, \quad (2b)$$

等效电路模型中相关的电阻、电感、电容和电导的计算方法同“quasi-TEM”模型<sup>[12,13]</sup>. 这样, 等效电路的功率损失  $P_{\text{loss}}$  和电势损失  $U_{\text{loss}}$  的大小可以表示为  $Z$  和  $Y$  的函数:

$$P_{\text{loss}} = \frac{(U_0/\sqrt{2})^2}{|Z^2 + 2Z + 1/Y|} \cos \varphi$$

$$= \frac{(U_0/\sqrt{2})^2 G_{\text{eff}}}{|(Z^2 + 2Z)Y + 1|}, \quad (3a)$$

$$\begin{aligned} U_{\text{loss}} &= \left| \frac{Z}{Z + 1/Y} \right| |U_0| \\ &= \frac{|U_0| |Z| \sqrt{G_{\text{eff}}^2 + (\omega C_{\text{eff}})^2}}{|ZY + 1|}, \end{aligned} \quad (3b)$$

其中,  $U_0$  是  $U_{\text{rf}}$  的幅值,  $\varphi$  是  $Y$  与  $U_{\text{rf}}$  的相位差, 即  $\tan \varphi = G_{\text{eff}}/C_{\text{eff}}$ . 因为  $|(Z^2 + 2Z)Y + 1| \approx 1$ ,  $|ZY + 1| \approx 1$ , 并且  $\omega$  较大时的  $\omega C_{\text{eff}}$  比  $G_{\text{eff}}$  大很多, 所以  $P_{\text{loss}}$  和  $U_{\text{loss}}$  的表达式可简化为

$$P_{\text{loss}} \approx \gamma_p (U_0/\sqrt{2})^2 G_{\text{eff}}, \quad (4a)$$

$$U_{\text{loss}} \approx \gamma_u |U_0| \omega C_{\text{eff}} \sqrt{R_{\text{eff}}^2 + L_{\text{eff}}^2}, \quad (4b)$$

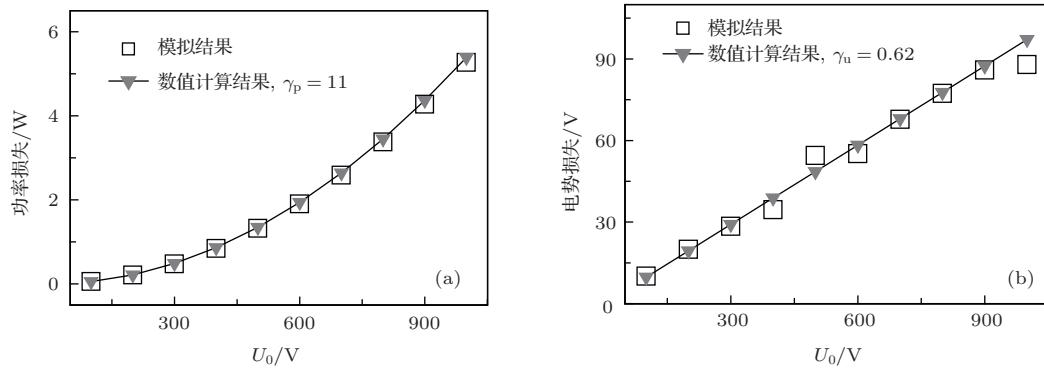

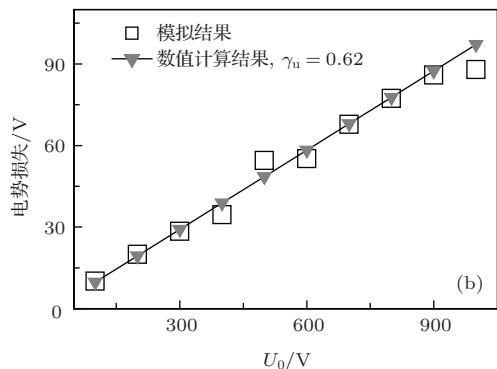

图 2 功率损失和电势损失的模拟和数值计算结果对比, 模拟使用 Ansoft Maxwell (a) 功率损失; (b) 电势损失

### 3 电势损失和功率损失对阱深和离子加热速率的影响

表面离子阱的阱深决定囚禁离子的稳定性, 离子加热速率影响囚禁离子的量子纠缠态退相干时间, 它们都是衡量表面离子阱性能的重要因素. 表面离子阱的衬底通过功率损失和电势损失能够间接影响阱深和离子加热速率的大小.

#### 3.1 电势损失对阱深的影响

为了在表面离子阱上方的  $XY$  平面产生势阱, 在两条 RF 电极上施加交变电压  $U_{\text{rf}} = U_0 \cos(\omega t)$ , 产生的电势场可以用赝势 [17] 等效为

$$\psi_{\text{rf}} = \frac{q^2}{4m\omega^2} |\nabla \phi_{\text{rf}}(x, y, z)|^2, \quad (5)$$

其中,  $q$  是囚禁离子的电荷量,  $m$  是囚禁离子的质量,  $\phi_{\text{rf}}$  是 RF 电极产生的电势场. 蕴势场在  $XY$  平面会产生一个赝势最小点, 囚禁离子在该点处做径

式中,  $\gamma_p, \gamma_u$  是为了补偿对 (3a), (3b) 式进行缩放操作的影响, 它们的取值与电极尺寸、电极材料以及衬底材料有关. 由上式可知, 衬底的功率损失和电势损失与衬底等效电容和等效电导相关, 其中, 功率损失与衬底等效电导正相关, 电势损失与衬底等效电容正相关. 图 2 对比了功率损失和电势损失的模拟结果和数值计算结果, 表面离子阱的电极尺寸选取麻省理工学院 (MIT) 提出的一款表面离子阱 [16] (若无特殊说明, 下文中的模拟实验使用的电极尺寸均选自文献 [16]), 衬底为 Si-SiO<sub>2</sub>. 如图 2 所示, 当  $\gamma_p = 11, \gamma_u = 0.62$  时, 功率损失和电势损失的模拟结果与数值计算结果基本符合.

向简谐振动. 蕴势最小点到离子阱表面的距离是离子阱的阱高, 它的上方存在赝势极大值点, 它们之间的赝势差是离子阱的阱深. 记中间的 DC 电极宽度为  $a$ , RF 电极宽度为  $b$ , 它们之间的间距为  $s$ . 若不考虑两侧直流控制电极的尺寸对  $Z$  轴囚禁势的影响, 在离子阱芯片的面积一定时, 即总的宽度度量  $a + b + s$  为常数时,  $s$  占总宽的比例越小阱深越深, 因此, 已有的研究是在  $s \rightarrow 0$  的情况下寻找最优尺寸设计. 但是, 当考虑衬底电势损失时, 因为衬底等效电容与 RF 电极和 DC 电极的间距成反比, 所以并非  $s$  越小越好. 可以认为  $XY$  平面的电势场是由宽度为  $b + s$  的电极和加反相位电压且宽度为  $s$  的电极共同产生的. 考虑  $s$  的影响后的势阱深度的解析表达比较复杂, 为了简化模型, 这里记  $s$  对阱深的影响因子为  $\chi_s(a, b, s)$  ( $0 < \chi_s < 1$ ), 并考虑电势损失的影响, 则文献 [17] 中的阱深表达式可以重写为

$$T_{\text{trap}} = \frac{q^2 (U_0 - U_{\text{loss}})^2}{\pi^2 m \omega^2}$$

$$\times \left[ \frac{b}{(a+b+s)^2 + (a+b+s)\sqrt{2a(b+s)+a^2}} \right]^2 \\ \times \chi_s(a, b, s). \quad (6)$$

以单位长度  $\lambda$  的大小衡量离子阱的绝对尺寸, 记

$$\begin{cases} a = \alpha\lambda, \\ b = \beta\lambda, \\ s = \gamma\lambda, \end{cases} \quad (7)$$

并

$$\kappa(\alpha, \beta, \gamma) = \chi_s(\alpha, \beta, \gamma) \beta^2 / [(\alpha + \beta + \gamma)^2 \\ + (\alpha + \beta + \gamma) \sqrt{2\alpha(\beta + \gamma) + \gamma^2}]^2,$$

并将  $U_{\text{loss}}$  的表达式 (4b) 代入 (6) 式, 得

$$T_{\text{trap}} = \frac{q^2}{\pi^2 m} \cdot \frac{U_0^2}{\omega^2} \cdot \left( 1 - \gamma_u \omega C_{\text{eff}} \sqrt{R_{\text{eff}}^2 + L_{\text{eff}}^2} \right)^2 \\ \times \frac{1}{\lambda^2} \cdot \kappa(\alpha, \beta, \gamma), \quad (8)$$

(8) 式右边的第一项是囚禁离子物理性质影响因子, 表征囚禁离子的质量和电荷量与阱深的关系; 第二项是交变电压影响因子, 说明阱深与所加电压幅度的二次方正相关, 与频率的二次方反相关; 第三项是衬底电势损失影响因子, 可以看出, 衬底等效电容越小, 阵深越深; 第四项是离子阱绝对尺寸影响因子, 说明阱深与绝对尺寸的二次方反相关; 最后一项是相对尺寸影响因子.

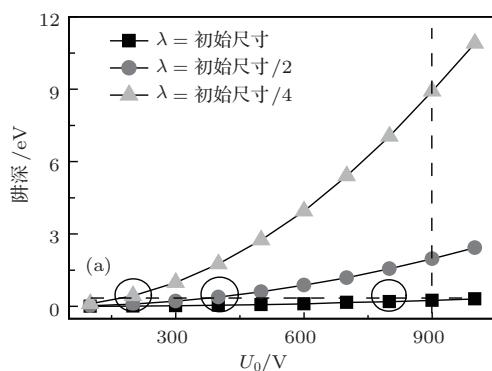

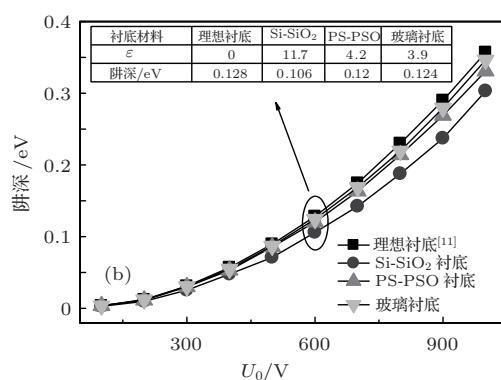

图 3(a) 是使用 Ansoft Maxwell 模拟的三种不同绝对尺寸的表面离子阱的阱深随交变电压幅值的变化. 模拟时假设囚禁的离子是  $^{40}\text{Ca}^+$ , 衬底材料是 Si-SiO<sub>2</sub>, 交变电压的频率是 10.2 MHz, 表面离子阱尺寸分别是初始绝对尺寸以及初始绝对尺寸缩小 1/2 和 1/4 (保持相对尺寸不变) 后的尺寸. 如图 3(a) 所示, 在每一种绝对尺寸下, 离子阱阱深是

图 3 不同绝对尺寸和不同衬底材料的表面离子阱的阱深随交变电压幅值的变化, 模拟使用 Ansoft Maxwell

(a) 不同绝对尺寸; (b) 不同衬底材料

交变电压幅值的二次函数. 垂直虚线说明, 当恒压缩小表面离子阱, 即保持电压幅值不变、缩小绝对尺寸时, 离子阱阱深随绝对尺寸的减小成二次方的增长; 水平虚线说明, 当全比例缩小表面离子阱, 即电压幅值和绝对尺寸等比例缩小时, 离子阱阱深基本保持不变. 这些规律显示, 缩小绝对尺寸或增大电压幅值都可以加深离子阱阱深, 但是在绝对尺寸缩小后, 芯片所能承受的最大电压减小, 电压幅值必须减小, 当它们减小的幅度相当时, 对离子阱阱深的影响甚微.

图 3(b) 是理想绝缘衬底, Si-SiO<sub>2</sub>, PS-PSO 和玻璃衬底的表面离子阱阱深随电压幅值变化的模拟结果. 如图所示, 在相同电压幅值下, 使用理想绝缘衬底的表面离子阱最深. 玻璃衬底对阱深的影响最小, 这得益于它较低的相电常数 (决定衬底等效电容的大小); 其次是 PS-PSO 衬底; 介电常数较大的 Si-SiO<sub>2</sub> 衬底对阱深的影响最大, 在交变电压的幅值为 600 V 时, 使用 Si-SiO<sub>2</sub> 衬底的表面离子阱的阱深为 0.106 eV, 相比于理想绝缘衬底的 0.128 eV, 衬底电势损失使阱深降低了 17.19%. 这些规律与 (8) 式中所描述的衬底电势损失影响因子对阱深的影响一致.

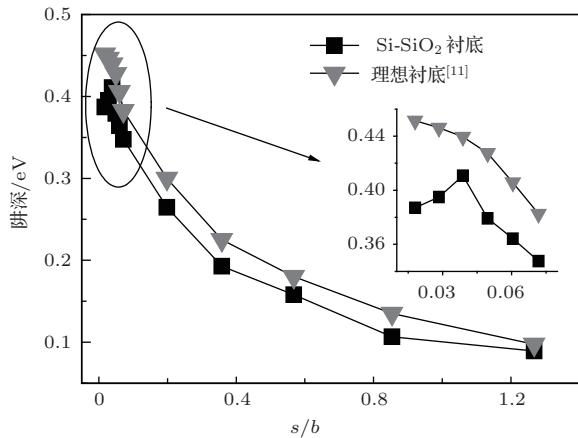

图 4 是阱深随  $s/b$  的变化趋势, 当总的宽度度量  $a + b + s$  为常数时, 对于理想绝缘衬底, 并且忽略电极侧壁电容的影响, 阵深随  $s/b$  的增大而减小. 但是, 对于 Si-SiO<sub>2</sub> 衬底, 当  $s/b \in (0.02, 0.08)$  时, 阵深随  $s/b$  的增大先增大后减小. 这是因为, 在  $s/b$  较小时, (8) 式中的衬底电势损失影响因子的作用大于相对尺寸影响因子, 又  $C_{\text{eff}} \propto 1/s$ , 所以阱深随  $s/b$  的增大而增大; 当  $s/b$  继续增大时, 相对尺寸影响因子起主要作用, 阵深随  $s/b$  的增大而减小. 对于 Si-SiO<sub>2</sub> 衬底, 在  $s/b = 0.04$  时, 阵深最深.

图 4 表面离子阱的阱深随  $s/b$  的变化, 模拟使用 Ansoft Maxwell

### 3.2 功率损失对离子加热速率的影响

离子加热速率是囚禁离子附近电场涨落引起的. 囚禁离子附近的电场涨落谱密度与施加于电极上的电压涨落谱密度有关, 电压涨落是由电极阻抗的约翰逊噪声产生的. 根据文献 [9], 由电极阻抗的约翰逊噪声引起的离子加热速率为

$$\Gamma_{0 \rightarrow 1} = \frac{q^2 k_B T R}{m \hbar \omega_m d^2}, \quad (9)$$

其中,  $k_B$  是玻尔兹曼常数,  $T$  是电极温度,  $R$  是 RF 电极的等效电阻,  $\omega_m$  是囚禁离子的久期频率. 记衬底功率损失对温度的影响大小为  $\Delta T$ , 这样, 由衬底功率损失引起的离子加热速率的改变可以写作

$$\Delta \Gamma_{0 \rightarrow 1} = \frac{q^2 k_B \Delta T R}{m \hbar \omega_m d^2}. \quad (10)$$

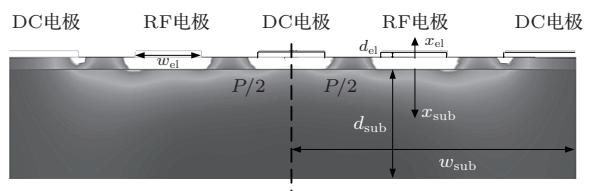

为了求解  $\Delta T$  的大小, 建立衬底温度分布模型. 如图 5 所示, 流过衬底的微电流产生的热功耗主要集

中于 RF 电极下方的  $\text{SiO}_2$  绝缘层中, 可以认为它是焦耳热源. 由对称性, 仅考虑离子阱右半侧的温度分布, 则热源的平均功率为  $P_{\text{loss}}/2$ , 产生的热量分别在 RF 电极和 Si 衬底中沿  $x_{\text{el}}$  和  $x_{\text{sub}}$  方向传导(由于  $\text{SiO}_2$  的导热能力远小于金和 Si, 并且  $\text{SiO}_2$  层很薄, 故忽略热量在  $\text{SiO}_2$  层的横向传热). 记 RF 电极的温度为  $T_{\text{el}}(x_{\text{el}})$ , 衬底的温度为  $T_{\text{sub}}(x_{\text{sub}})$ , RF 电极的长宽厚分别为  $l$ ,  $w_{\text{el}}$  和  $d_{\text{el}}$ , 衬底的厚度为  $d_{\text{sub}}$ , 衬底中心到侧壁的距离为  $w_{\text{sub}}$ . 设真空腔中的温度为  $T_v$ , 衬底底部通过散热系数为  $h$  的紫铜片向外界散热, 外界温度为  $T_0$ . RF 电极通过热辐射向真空腔内传递热量, 因为 RF 电极很薄, 只考虑其上表面的热辐射. 由于周围是近似的真空环境, 不考虑衬底、电极与周围环境的表面对流传热.

图 5 使用 Ansoft Maxwell 模拟的衬底热功耗分布

基于上述分析, RF 电极和衬底中的一维能量方程分别为

$$\begin{cases} \partial^2 T_{\text{el}} / \partial x_{\text{el}}^2 = 0, \\ \partial^2 T_{\text{sub}} / \partial x_{\text{sub}}^2 = 0, \end{cases} \quad (11)$$

因为不同层在边界处与相邻部分的温度相同, 流入和流出边界的热能相同, 所以上述方程的边界条件为

$$\begin{cases} T_{\text{el}}(x_{\text{el}} = 0) = T_{\text{sub}}(x_{\text{sub}} = 0), \\ k_{\text{el}}(\partial T_{\text{el}} / \partial x_{\text{el}})|_{x_{\text{el}}=d_{\text{el}}} = \varepsilon_{\text{el}} \sigma [T_{\text{el}}^4(x_{\text{el}} = d_{\text{el}}) - T_v^4], \\ k_{\text{sub}}(\partial T_{\text{sub}} / \partial x_{\text{sub}})|_{x_{\text{sub}}=d_{\text{sub}}} = -h[T_{\text{sub}}(x_{\text{sub}} = d_{\text{sub}}) - T_0], \\ -k_{\text{el}} l w_{\text{el}} (\partial T_{\text{el}} / \partial x_{\text{el}})|_{x_{\text{el}}=0} - k_{\text{sub}} l w_{\text{sub}} (\partial T_{\text{sub}} / \partial x_{\text{sub}})|_{x_{\text{sub}}=0} = P_{\text{loss}}/2, \end{cases} \quad (12)$$

式中  $k_{\text{el}}$  和  $k_{\text{sub}}$  分别是 RF 电极和衬底的导热率,  $\varepsilon_{\text{el}}$  是 RF 电极的热辐射发射率,  $\sigma$  是黑体辐射常数. 解得 RF 电极和衬底的温度分布为

$$\begin{cases} T_{\text{el}} = Z_1 x_{\text{el}} + Z_3, \\ T_{\text{sub}} = Z_2 x_{\text{sub}} + Z_3. \end{cases} \quad (13)$$

取平均温度为 RF 电极温度, 则有

$$\Delta T = \frac{Z_1 d_{\text{el}}}{2} + Z_3 - T_v, \quad (14)$$

其中,  $Z_1$ ,  $Z_2$  和  $Z_3$  可通过求解以下方程组得到

$$\begin{cases} Z_1 k_{\text{el}} - \varepsilon_{\text{el}} \sigma [(Z_1 d_{\text{el}} + Z_3)^4 - T_v^4] = 0, \\ Z_2 + h(Z_2 d_{\text{sub}} + Z_3 - T_0) = 0, \\ Z_1 k_{\text{el}} l w_{\text{el}} + Z_2 k_{\text{sub}} l w_{\text{sub}} + P_{\text{loss}}/2 = 0. \end{cases} \quad (15)$$

这样, 便得到了衬底功率损失对离子加热速率影响

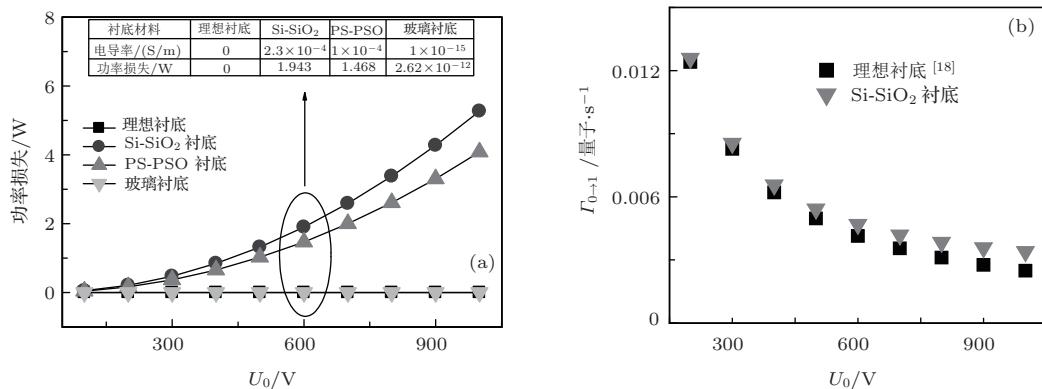

图6 4种衬底材料的离子阱衬底功率损失随交变电压幅值的变化以及Si-SiO<sub>2</sub>衬底的离子阱离子加热速率随交变电压幅值的变化 (a) 衬底功率损失, 模拟使用 Ansoft Maxwell; (b) 离子加热速率,  $T_v = 100$  K,  $f = 10.2$  MHz, 数值计算使用 Matlab

的解析模型. 图6(a)是四种不同衬底材料的表面离子阱衬底功率损失随交变电压幅值的变化, 因为没有电流流过理想绝缘衬底, 所以它的功率损失为零. 玻璃衬底的等效电导较小, 衬底功率损失也较低; PS-PSO衬底和Si-SiO<sub>2</sub>衬底的功率损失较大, 在电压幅值为600 V时, Si-SiO<sub>2</sub>衬底的平均功率损失达1.94 W. 图6(b)是理想绝缘衬底和Si-SiO<sub>2</sub>衬底的表面离子阱离子加热速率随交变电压幅值的变化, 对于理想绝缘衬底, 由于离子振动的久期频率随电压幅值的增大而线性增长, 又 $\Gamma_{0 \rightarrow 1} \propto 1/\omega_m$ , 所以离子加热速率随电压幅值的增大而减小. 对于Si-SiO<sub>2</sub>衬底, 衬底功率损失产生的焦耳热源会加热RF电极, 造成离子加热速率增大. 对每一确定的电压幅值, Si-SiO<sub>2</sub>衬底表面离子阱的离子加热速率大于理想衬底, 且随着电压幅值的增大, 衬底功率损失的影响越来越大. 在电压幅值为600 V时, Si-SiO<sub>2</sub>衬底的功率损失使离子加热速率加速13.37%. 在文献[18]中也观察到类似的现象: 当电压幅值增大到一定程度, 会使离子加热速率大于理论值, 文章指出这可能是由于温度增大造成的.

#### 4 基于模型指导的衬底真空隔离设计

从上文的模型分析可以看出, 衬底的电势损失能够降低势阱深度, 功率损失能够加速离子加热速

率, 且电势损失与衬底耦合电容正相关, 功率损失与衬底等效电导正相关. 为了降低表面离子阱衬底的功率损失和电势损失, 本文提出VTIS衬底表面离子阱, 即在衬底表面的RF电极和DC电极间刻蚀出多条隔离槽, 以达到减小衬底等效电导和耦合电容的目的.

#### 4.1 衬底真空隔离结构设计

衬底表面的隔离槽的制造采用成熟的半导体隔离槽刻蚀工艺或者玻璃刻蚀技术. 为了更好地减小衬底等效电导和耦合电容, 本设计选取介电常数和电导率较小(几种材料的相对介电常数和电导率见表1)的真空填充隔离槽. 因为表面离子阱工作在真空腔中, 所以制造时仅需在衬底相应位置刻蚀出隔离槽即可.

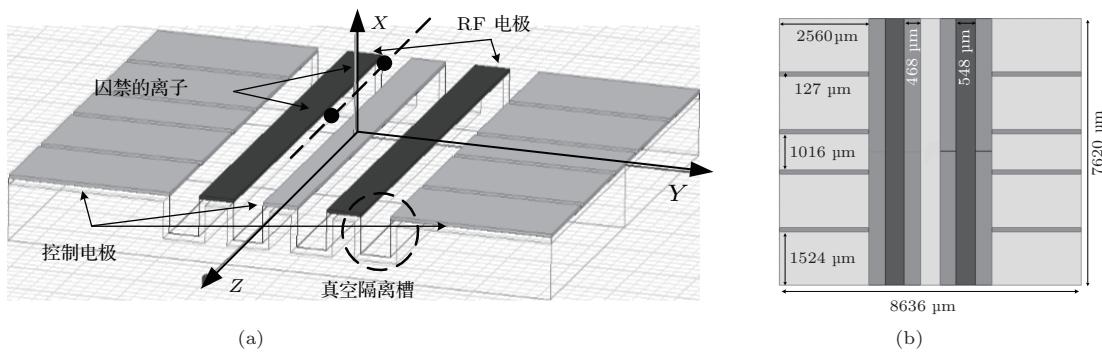

图7(a)是VTIS衬底表面离子阱结构图, 它在五线表面离子阱结构的基础上进一步加工刻蚀出隔离槽. 芯片由电极和衬底两部分构成, 对于Si-SiO<sub>2</sub>和PS-PSO衬底, 衬底的表面是一层二氧化硅或氧化多孔硅绝缘阻隔层; 对于玻璃衬底, 不需要这种氧化的绝缘阻隔层. 在衬底表面, 有四条真空隔离槽将衬底分为五部分, 这五部分上面分别对应五线阱的两条RF电极和三条DC电极, 其中外侧的两条DC电极被分为若干段, 电极材料为金. 图7(b)是VTIS衬底表面离子阱的俯视图, 它的电极尺寸出自文献[14].

表1 材料的相对介电常数和电导率

| 材料                          | 真空                     | 硅                    | 多孔硅                | 玻璃                  |

|-----------------------------|------------------------|----------------------|--------------------|---------------------|

| 相对介电常数 $\epsilon$           | 1                      | 11.7—12.9            | 3.8—4.4            | 3.78—4.2            |

| 电导率 $\sigma/S \cdot m^{-1}$ | $7.69 \times 10^{-17}$ | $2.3 \times 10^{-3}$ | $1 \times 10^{-3}$ | $1 \times 10^{-15}$ |

图7 VTIS衬底的五线表面离子阱结构 (a) 3D结构图; (b) 俯视图

需要指出的是,由于衬底的表面效应<sup>[13]</sup>, 对RF电极有影响的衬底有效深度 $\delta_{\text{sub}}$ 是RF电极上所加的交变电压的频率 $f(=\omega/(2\pi))$ 的函数, 表征如下:

$$\delta_{\text{sub}} = 1/\sqrt{\pi f \sigma_{\text{sub}} \mu_0}, \quad (16)$$

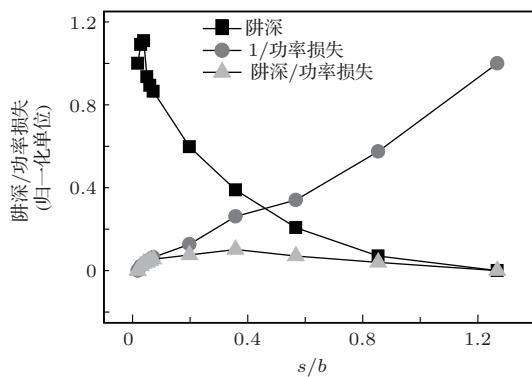

其中,  $\sigma_{\text{sub}}$ 是衬底的电导率,  $\mu_0$ 是真空的磁导率. 因此, 隔离槽深度由衬底材料和交变电压的频率决定. 隔离槽的宽度设计要综合考虑对势阱深度和衬底功率损失的影响. 图8是VTIS结构的Si-SiO<sub>2</sub>衬底表面离子阱的阱深和衬底功率损失的倒数随 $s/b$ 的变化, 图中使用的是归一化后的单位. 如图所示, 阵深随 $s/b$ 先增大后变小,  $1/P_{\text{loss}}$ 随 $s/b$ 的增加而变大, 当 $s/b = 0.36$ 时,  $T_{\text{trap}}/P_{\text{loss}}$ 达到最大值. 针对不同的囚禁离子和不同的衬底材料, 在设计VTIS表面离子阱的隔离槽宽度时, 既要使得阱深满足囚禁离子的需要, 也要尽量减小衬底功率损失.

图8 VTIS表面离子阱的阱深和衬底功率损失随 $s/b$ 的变化, 模拟使用 Ansoft Maxwell

## 4.2 模拟仿真与讨论

为了验证VTIS衬底对减小功率损失和电势损失的作用, 本节使用Ansoft Maxwell电磁模拟

软件, 采用有限元分析方法计算VTIS衬底表面离子阱的势阱分布, 对比VTIS衬底和NS衬底离子阱的势阱深度和衬底功率损失. 选取MIT小组提出的一款五线表面离子阱结构作为对比实验所用的表面离子阱的电极结构, 其尺寸参数如图7(b)所示.

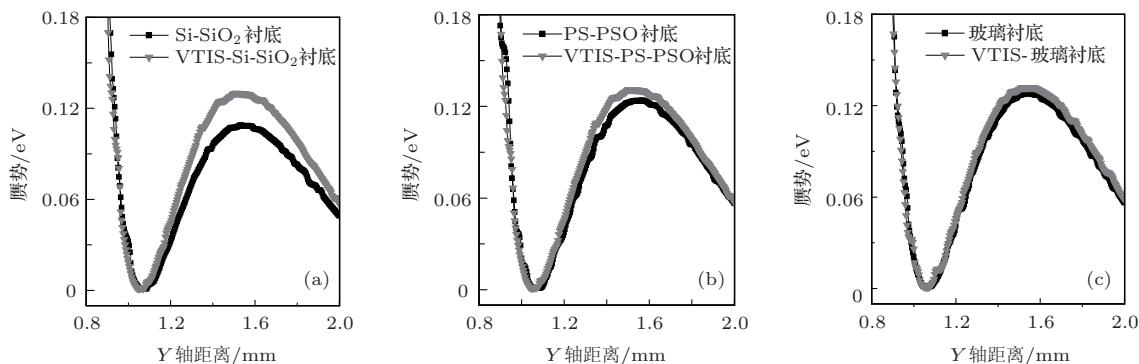

实验中, RF电极上所加的交变电压的幅度 $U_0 = 600$  V, 频率 $f = 10.2$  MHz, 衬底材料选取Si-SiO<sub>2</sub>, PS-PSO以及玻璃三种, 每种材料的衬底又分为NS和VTIS两种结构. 因为Si-SiO<sub>2</sub>衬底具有与现有工艺兼容、适合大规模生产的优点, 是表面离子阱芯片研究与发展的趋势, 所以本节将着重分析VTIS结构对Si-SiO<sub>2</sub>衬底的优化. 图9是VTIS和NS结构Si-SiO<sub>2</sub>, PS-PSO和玻璃衬底的表面离子阱中心处沿Y轴的势阱分布. 因为阱高只与电极的几何尺寸有关<sup>[17]</sup>, 所以VTIS和NS衬底表面离子阱的阱高不变. 但是, VTIS衬底的等效电容较低, 因此, 可以减小衬底的电势损失(见(4b)式), 从而减小衬底对离子阱阱深的影响. 如图所示, VTIS结构的Si-SiO<sub>2</sub>衬底的离子阱阱深为0.127 eV, 相对NS结构的0.106 eV, 加深了20.22%, 并且十分接近理想绝缘衬底的0.128 eV. 因为PS-PSO和玻璃衬底的相对介电常数较小, 它们的电势损失较低, 阵深已经接近理想绝缘衬底, 所以VTIS结构对它们的阱深优化不大, 相比于NS结构, 只加深了0.07%和0.04%.

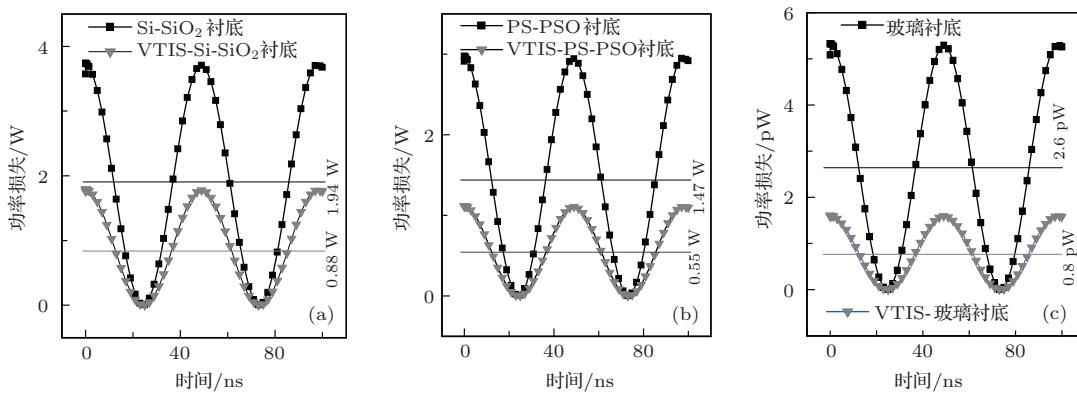

根据(4a)式, 衬底功率损失的大小与衬底的等效电导正相关. VTIS衬底可以减小流经衬底的电流, 降低衬底的等效电导, 因此它的衬底功率损失比NS衬底的小很多. 图10是NS和VTIS结构Si-SiO<sub>2</sub>, PS-PSO和玻璃衬底表面离子阱的衬底瞬时功率损失, 它随交变电压的变化而周期性变化. 由于硅的电导率较高, 通过Si-SiO<sub>2</sub>衬底的

电流较大, 产生的功率损失很大, NS结构Si-SiO<sub>2</sub>衬底的平均功率损失达到1.94 W, VTIS的Si-SiO<sub>2</sub>衬底的平均功率损失相对于NS的降低了54.55%,

为0.88 W. VTIS结构的PS-PSO衬底和玻璃衬底的功率损失分别比NS结构的降低了62.67% 和62.3%.

图9 使用Ansoft Maxwell模拟的VTIS衬底与NS衬底的表面离子阱Y轴电势分布 (a) Si-SiO<sub>2</sub>衬底; (b) PS-PSO衬底; (c) 玻璃衬底

图10 使用Ansoft Maxwell模拟的衬底的瞬时功耗损失 (a) Si-SiO<sub>2</sub>衬底; (b) PS-PSO衬底; (c) 玻璃衬底

## 5 结 论

本文通过分析表面离子阱衬底的功率损失和电势损失对离子阱阱深和离子加热速率的影响, 提出考虑衬底影响的阱深和离子加热速率的解析分析模型. 研究发现, 硅基衬底的电势损失能降低表面离子阱的阱深, 功率损失能加速囚禁离子的加热速率. 为了减小衬底效应的不利影响, 本文提出真空间隔结构的表面离子阱, 该结构可以有效降低衬底的电势损失和功率损失, 从而减小衬底对阱深度和离子加热速率的影响. 本文提出的衬底对阱深和离子加热速率影响的分析模型以及衬底真空间隔结构设计, 对于设计高稳定性、低加热速率的表面离子阱具有很大的指导意义. 在以后的深入研究中, 需要进一步考虑电极对稳定囚禁的影响, 提出综合全面的分析模型和设计指导.

## 参考文献

- [1] Cirac J I, Zoller P 1995 *Phys. Rev. Lett.* **74** 4091

- [2] Jiang Z, Chen P X 2012 *Acta Phys. Sin.* **61** 014209 (in Chinese)[蒋智, 陈平形 2012 物理学报 **61** 014209]

- [3] Seidelin S, Chiaverini J, Reichle R, Bollinger J J, Leibfried D, Britton J, Wesenberg J H, Blakestad R B, Epstein R J, Hume D B, Itano W M, Jost J D, Langer C, Ozeri R, Shiga N, Wineland D J 2006 *Phys. Rev. Lett.* **96** 253003

- [4] Kim T H, Herskind P F, Kim T, Kim J, Chuang I L 2010 *Phys. Rev. A* **82** 043412

- [5] Chiaverini J, Blakestad R B, Britton J, Jost J D, Langer C, Leibfried D, Ozeri R, Wineland D J 2005 *Quant. Inf. Comp.* **5** 419

- [6] Chen L, Wan W, Xie Y, Wu Y, Zhou F, Feng M 2013 *Chin. Phys. Lett.* **30** 013702

- [7] Wan W, Chen L, Wu H Y, Xie Y, Zhou F, Feng M 2013 *Chin. Phys. Lett.* **30** 073701

- [8] Wan J Y, Wang Y Z, Liu L 2008 *Chin. Phys. B* **17** 3565

- [9] Dubessy R, Coudreau T, Guidoni L 2009 *Phys. Rev. A* **80** 031402

- [10] Labaziewicz J, Ge Y, Antohi P, Leibbrandt D, Brown K R, Chuang I L 2008 *Phys. Rev. Lett.* **100** 013001

- [11] Brownnutt M 2007 *Ph. D. Dissertation* (London: Imperial College)

- [12] Zheng J, Hahm Y C, Weisshaar A, Tripathi V K 1999 *Proc. IEEE 8th Topical Meeting Electrical Performance of Electronic Packaging* San Diego, CA, October 25–27 p185

- [13] Kwon Y R, Hietala V M, Champlin K S 1987 *IEEE Trans. Microw. Theory Tech.* **35** 545

- [14] Salvador A B 2008 *M. S. Dissertation* (Ulm: Ulm University)

- [15] Erin F 2009 *Ph. D. Dissertation* (Innsbruck: Innsbruck University)

- [16] Pauli A 2011 *M. S. Dissertation* (Innsbruck: Innsbruck-University)

- [17] House M G 2008 *Phys. Rev. A* **78** 033402

- [18] Turchette Q A, Kielpinski D, King B E, Leibfried D, Meekhof D M, Myatt C J, Rowe M A, Sackett C A, Wood C S, Itano W M, Monroe C, Wineland D J 2000 *Phys. Rev. A* **61** 063418

## Substrate effect on surface-electrode ion trap and hybrid design for ion trap

Zhang Jian<sup>1)</sup> Chen Shu-Ming<sup>1,2)†</sup> Liu Wei<sup>1)</sup>

1) (College of Computer, National University of Defense Technology, Changsha 410073, China)

2) (Science and Technology on PDL, National University of Defense Technology, Changsha 410073, China)

(Received 14 October 2013; revised manuscript received 30 October 2013 )

### Abstract

To analyze the trap depth and ion heating rate of a surface ion trap under the influence of substrate power loss and voltage loss, in this paper we propose analytic expressions of trap depth and ion heating rate. The results show that the voltage loss of Si substrate can reduce the trap depth by 17.19%, and the power loss would accelerate the ion heating rate by 13.37%. In order to reduce the influence of substrate effect, a new surface ion trap with low self-heating and voltage-loss is proposed in this paper, whose substrate is insulated by some vacuum trench to reduce the equivalent conductivity and capacitance. The simulation results illuminate that compared with the surface ion trap with normal Si-SiO<sub>2</sub> substrate, the one with vacuum trench insulation exhibits a 20.22% increase in trap depth and a 54.44% reduction in power loss.

**Keywords:** surface ion trap, power loss, voltage loss, heating rate

**PACS:** 03.67.Lx, 37.10.Ty, 41.20.-q

**DOI:** 10.7498/aps.63.060303

† Corresponding author. E-mail: smchen@163.com