# 基于Cu/SiO<sub>x</sub>/Al结构的阻变存储器多值特性及机理的研究\*

陈然 周立伟 王建云 陈长军 邵兴隆 蒋浩

张楷亮 吕联荣<sup>†</sup> 赵金石<sup>‡</sup>

(天津理工大学电子信息工程学院, 天津市薄膜电子与通信器件重点实验室, 天津 300384)

(2013年11月3日收到; 2013年12月6日收到修改稿)

采用氧化硅材料构建了Cu/SiO<sub>x</sub>/Al的三明治结构阻变存储器件。用半导体参数分析仪对其阻变特性进行测量, 结果表明其具有明显的阻变特性, 并且通过调节限制电流, 得到了四个稳定的阻态, 各相邻阻态的电阻比大于10, 并且具有良好的数据保持能力。在不同温度条件下对各个阻态进行电学测试及拟合, 明确了不同阻态的电子传输机理不尽相同: 阻态1和阻态2为欧姆传导机制, 阻态3为P-F (Pool-Frenkel) 发射机制, 阻态4为肖特基发射机制。根据电子传输机制, 建立了铜细丝导电模型并对Cu/SiO<sub>x</sub>/Al阻变存储器件各个阻态的电致阻变机制进行解释。

**关键词:** 阻变存储器, SiO<sub>x</sub> 薄膜, 多值存储, 阻变机理

**PACS:** 72.60.+g, 72.20.-i, 73.40.Cg, 73.40.Rw

**DOI:** 10.7498/aps.63.067202

## 1 引言

阻变存储器 (resistive switching random access memory, RRAM) 以低功耗、高集成度、快速擦写以及结构简单等优势受到业界的广泛关注, 是新一代非挥发性存储器的有力竞争者之一<sup>[1-4]</sup>。在半导体工艺节点不断向前推进的过程中, 以基于电荷存储机制的浮栅结构Flash为代表的非挥发性存储器遇到了严重的技术瓶颈——由于存在着栅氧化物减薄导致的电荷泄漏以及器件间距减小引起的电荷耦合等问题, 此外还有操作电压大、工作速度慢等缺点, 因此无法满足市场对非挥发性存储器的超高存储密度等要求<sup>[5]</sup>。而阻变存储器是基于非电荷存储机制的新型非挥发性存储器, 非电荷存储机制决定了其具有优秀的可缩小性。并且除了减小

存储单元面积和3D集成能够提高存储器集成度之外, 采用多值存储技术来提升下一代非挥发性存储器的存储密度也是当前发展高密度存储技术的重要途径之一。相比传统的二进制数据存储, 多值存储技术以单个存储单元进行多个数据的存储来实现在存储芯片的高存储密度<sup>[6]</sup>。

目前有关阻变存储器的多值存储技术常见报导<sup>[7-16]</sup>, 然而有关多值存储技术的研究热度虽然很高, 但有关多值存储的操作模式、多值存储的物理机理及多值存储功能材料体系仍存在一定的争议。特别是对其机理的研究还处于探索阶段。目前文献报道的阻变存储器多值存储技术大致可分为两种: 一种是通过改变复位电压获得不同的高阻态, 如中国科学院物理研究所张广宇等<sup>[17]</sup>从石墨烯/SiO<sub>2</sub>/石墨烯平面结构中观察到的多值存储特性, 他们通过逐渐减小复位电压, 获得了逐渐增大

\* 国家自然科学基金(批准号: 61274113, 11204212)、教育部新世纪优秀人才支持计划(批准号: NCET-11-1064)、天津市科技计划项目(批准号: 13JCYBZC15700, 13JCZDJC26100) 和天津市高等学校科技发展基金计划(批准号: 20100703, 20130701) 资助的课题。

† 通讯作者。E-mail: 163lvlianrong@163.com

‡ 通讯作者。E-mail: jinshi58@163.com

的高阻态电阻(即得到了多个高阻态). 另一种是通过改变限制电流得到不同的低阻态, 如德国于利希研究中心的Waser课题组<sup>[7]</sup>从Cu/Cu : SiO<sub>x</sub>/W结构中获得的多值特性, 他们发现随着限制电流的逐渐变大, 对应低阻态电阻值逐渐减小(即得到了多个低阻态). 这种方式在多值离散性方面有所提高<sup>[11,18]</sup>, 但是并未对产生这种对应关系的原因进行探索性分析.

此外, 目前阻变材料的研究主要集中在二元氧化物上, 如HfO<sub>x</sub><sup>[6]</sup>, TiO<sub>x</sub><sup>[19–21]</sup>, VO<sub>x</sub><sup>[22]</sup>, WO<sub>x</sub><sup>[18]</sup>以及SiO<sub>x</sub><sup>[23]</sup>等. 其中, 由于与CMOS集成工艺的高度兼容性使得SiO<sub>x</sub>更加有希望进入硅工艺为主导的半导体市场. 同样, Cu及Al作为金属电极, 也是因为目前铜及铝互连技术已广泛地应用于集成电路工艺<sup>[24]</sup>. 但是, 这些常规材料构成的Cu/SiO<sub>x</sub>/Al结构阻变单元的阻变特性及机理需要进一步的研究.

本文选用了半导体集成工艺中应用非常广泛的氧化硅、铜、铝材料, 构建Cu/SiO<sub>x</sub>/Al三明治阻变结构. 通过调节限制电流, 控制SiO<sub>x</sub>薄膜中铜导电细丝的形成和生长, 获得了4个稳定阻态的多值存储特性. 本文通过对限制电流对多值存储影响的研究, 基于不同阻态的电流-电压(*I-V*)曲线拟合及温度-传导机制关系的分析, 对多值存储技术物理机理做了详细的理论分析.

## 2 实验

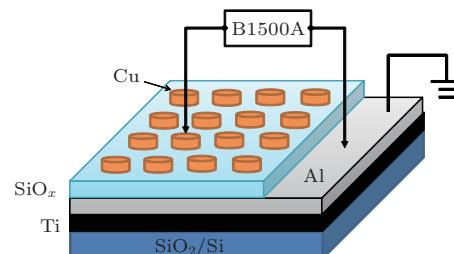

在Al(200 nm)/Ti(5 nm)/SiO<sub>2</sub>/Si衬底上采用射频磁控溅射在室温下沉积了50 nm的SiO<sub>x</sub>薄膜, 表1为沉积参数. 之后, 使用金属掩模板在氧化硅薄膜上沉积出直径为200 μm圆形分立的Cu电极, 下电极Al及上电极Cu都是采用电子束蒸发(SKY EB-500)制备而成, 且厚度都为200 nm. 制备出Cu/SiO<sub>x</sub>/Al三明治结构的阻变器件.

在室温条件下, 采用半导体分析仪(Agilent B1500A)对制备的Cu/SiO<sub>x</sub>/Al三明治结构进行*I-V*特性测试. 利用变温探针台, 通过钨探针连接半导体分析仪与上下电极, 测量不同阻态样品的电流随温度条件下的变化曲线. 如图1所示, 所有*I-V*测试偏压施加在上电极铜, 下电极铝接地. 器件的阻值通过0 V → 0.1 V的电压扫描并在0.1 V处读取. 利用Agilent 5500型多模式扫描探针显微镜(AFM)观察薄膜的表面微观结构并通过Philips

X'Pert MPD型(Cu K)X射线衍射仪(XRD)分析薄膜的结晶取向.

表1 SiO<sub>x</sub>薄膜的沉积条件

| 沉积条件      | 参数                          |

|-----------|-----------------------------|

| 工作气压/Pa   | 0.5                         |

| 沉积温度/°C   | 室温                          |

| 沉积时间/min  | 30                          |

| 氩气流量/sccm | 20                          |

| 溅射功率/W    | 100(射频)                     |

| 靶材        | SiO <sub>1.5</sub> (99.99%) |

图1 Cu/SiO<sub>x</sub>/Al三明治结构阻变器件单元结构及测试示意图

## 3 结果与分析

### 3.1 SiO<sub>x</sub>薄膜微观结构的表征

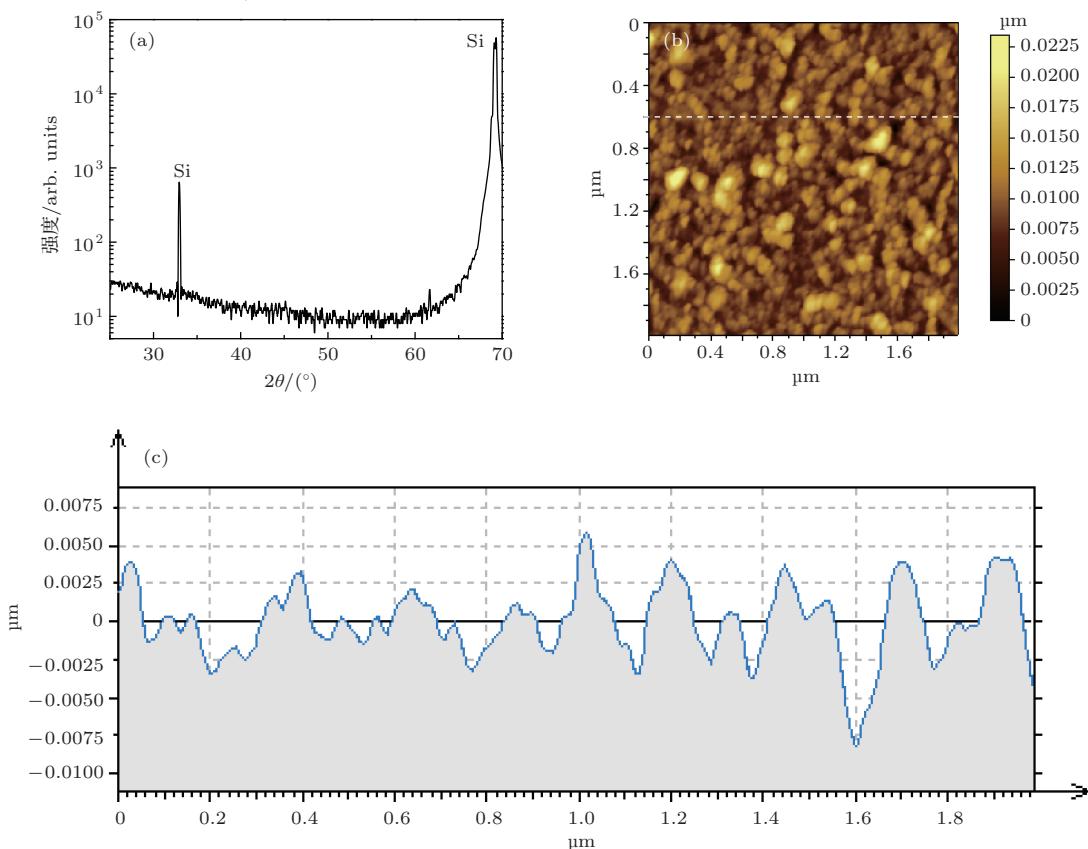

图2(a)是SiO<sub>x</sub>薄膜的XRD测试结果, 从图中没有观察到SiO<sub>x</sub>对应的衍射峰, 说明在室温条件下制备的SiO<sub>x</sub>薄膜是无定型态. 为了进一步了解SiO<sub>x</sub>薄膜的微观结构, 利用AFM在2 μm × 2 μm区域内对SiO<sub>x</sub>/Al样品进行原位表面形貌测试. 图2(b)和(c)分别是AFM形貌及对应(b)中虚线位置的线性扫描图, 可以看出薄膜表面比较粗糙且有凸起的颗粒, 薄膜表面峰与谷之间最高相差14 nm(图2(c)), 测得的均方根粗糙度为2.5 nm. 同时可以观察到SiO<sub>x</sub>薄膜比较疏松, 颗粒与颗粒之间的缝隙也相当明显. 从图2(c)AFM的线性扫描图中可知, 该缝隙水平宽度的平均尺寸达到了30 nm.

### 3.2 电学特性

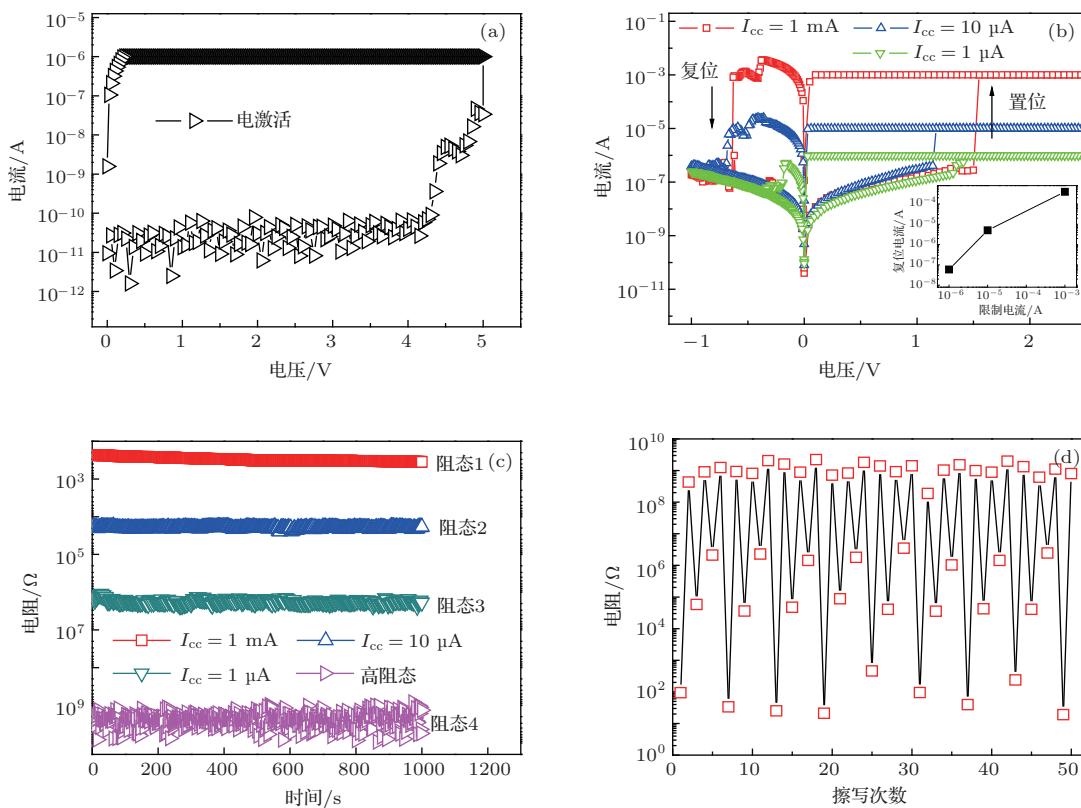

Cu/SiO<sub>x</sub>/Al结构阻变器件的初始态为高电阻态. 为了实现高阻态↔低阻态之间的电阻可逆转变, 首先对器件施加正向扫描电压0 V → 5 V, 当电压达到阈值电压4.4 V时, 发生电流急剧增加的

现象,使得电阻从高阻态变成低阻态,这个操作称之为电激活 (forming) 过程(图3(a)). 这里为了防止器件发生不可修复的硬击穿现象,设定了 $1\text{ }\mu\text{A}$ 的限制电流( $I_{cc}$ ). 接着电激活之后,如图3(b)对器件施加反向扫描电压 $0\text{ V}\rightarrow -1\text{ V}$ ,当电压超过一定负电压时( $-0.7\text{ V}$ ),发生电流急剧减小现象,使得器件从低阻态又转变回高阻态,该过程叫做复位 (reset) 过程. 复位之后,施加正向电压,电阻从高阻态转变为低阻态的过程称为置位 (set). 为了研究置位过程中限制电流( $I_{cc}$ )大小对复位电流( $I_{reset}$ )的影响,在不同限制电流( $1\text{ }\mu\text{A}-1\text{ mA}$ )的条件下,如图3(b)所示,对Cu/SiO<sub>x</sub>/Al结构器件进行了I-V测试,此时采取 $0\text{ V}\rightarrow 3\text{ V}\rightarrow 0\text{ V}\rightarrow -1\text{ V}\rightarrow 0\text{ V}$ 的电压扫描方式.有一个明显的特点是置位过程中设定的限制电流,影响复位电流大小.如图3(b)插图所示,复位电流随着限制电流增加呈现线性增加关系.这样可通过调节限制电流获得电阻值不同的多个阻态.限制电流为 $1\text{ mA}$ 时,阻态1电阻约为 $250\text{ }\Omega$ ;限制电流为 $10\text{ }\mu\text{A}$ 时,阻态2电阻约为 $19\text{ k}\Omega$ ;当限制电流为 $1\text{ }\mu\text{A}$ 时,阻态3电阻约为 $1.7\text{ M}\Omega$ ;对应的所有阻态复位后的阻态称为阻态4.这种随着限制电流不同,得到的各阻态电阻大小也相应变化的特性,被称之为多值存储特性.

此外,本文还对器件的保持特性 (retention) 以及耐擦写特性 (endurance) 进行了测试:保持特性测试结果如图3(c)所示,采用直流测试法,对不同阻态施加 $0.1\text{ V}$ 恒压其阻态持续 $1000\text{ s}$ ,可以看出各阻态之间的电阻比不仅大于 $10$ ,并且保持数据稳定,各阻态阻值没有任何衰减;耐擦写特性测试结果如图3(d)所示,在限流为 $1\text{ mA}\rightarrow 10\text{ }\mu\text{A}\rightarrow 1\text{ }\mu\text{A}\rightarrow 1\text{ mA}$ 循环变化下,对每个限流进行以下操作:采用直流测试法,在上述限流条件下,以 $0\text{ V}\rightarrow 3\text{ V}$ 的扫描电压将器件置位后,读取此时器件的阻值,随后以 $0\text{ V}\rightarrow -1\text{ V}$ 的扫描电压将器件复位并读取阻值.在 $50$ 次的擦写操作中,阻态1在 $113\text{ }\Omega$ 、阻态2在 $48\text{ k}\Omega$ 、阻态3在 $2\text{ M}\Omega$ 、阻态4在 $1.1\text{ G}\Omega$ 左右略有波动,各阻态之间的电阻比仍大于 $10$ ,且没有明显的衰减.由器件的数据保持特性和耐擦写特性,说明Cu/SiO<sub>x</sub>/Al结构具有稳定的非挥发多值存储特性.

### 3.3 机制分析

为了研究Cu/SiO<sub>x</sub>/Al结构阻变存储器的多值存储阻变机制,通过拟合测试得出的I-V曲线,对每一个阻态的电子传输机制进行了分析.

图2 SiO<sub>x</sub>薄膜的XRD及AFM测试结果 (a) XRD谱图; (b) AFM形貌图; (c) 对应(b)图中虚线位置的线性扫描图

图3  $I$ - $V$  测试结果 (a) 电激活曲线; (b) 不同限制电流下  $I$ - $V$  曲线, 插图为复位电流 - 限制电流关系曲线; (c) 各阻态的保持特性测试结果; (d) 多值存储耐擦写特性测试结果

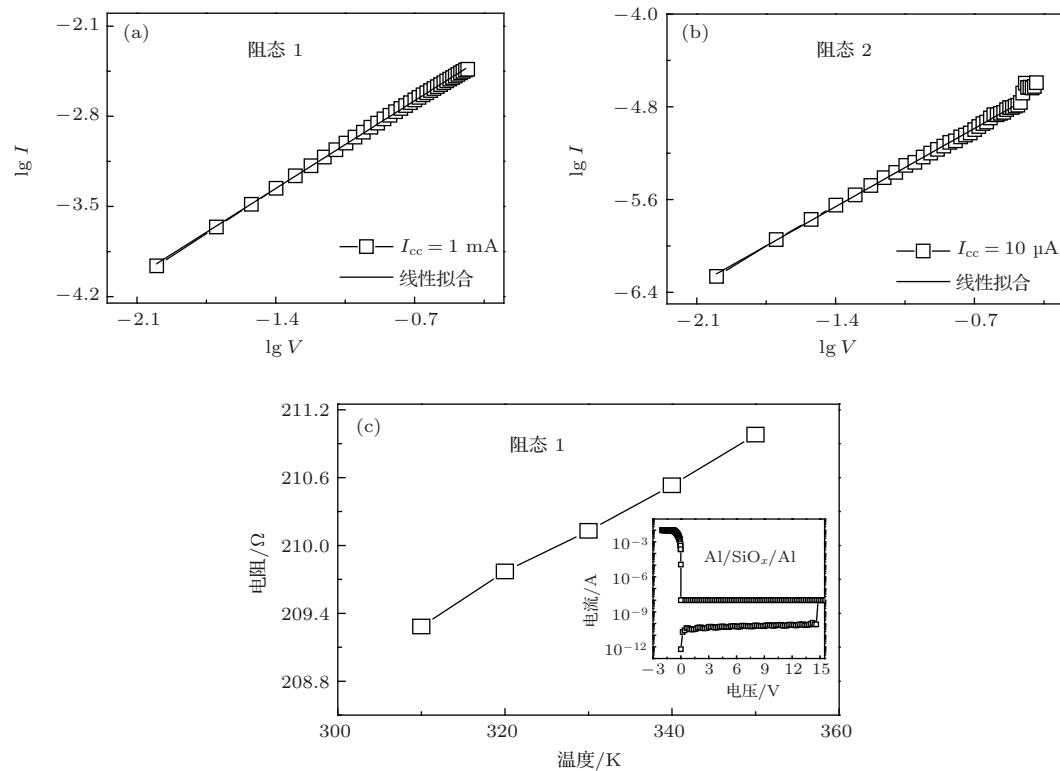

图4 阻态1和阻态2的电学测试拟合 (a) 阻态1欧姆传导机制拟合曲线; (b) 阻态2欧姆传导机制拟合曲线; (c) 阻态1电阻 - 温度关系曲线; 插图为  $\text{Al}/\text{SiO}_x/\text{Al}$  结构的阻变特性测试

如图4(a)和(b)所示, 阻态1及阻态2的Lg-I-LgV曲线成线性关系, 并且斜率为1, 这表示与欧姆传导机制相符。由此可推测 $\text{SiO}_x$ 薄膜由高电阻转变为低电阻, 与薄膜内形成连接上下电极的导电细丝有关。在这里构成导电细丝的可能为Cu(电化学金属化机制)或者氧空位(价态变化机制)。为了进一步确认导电细丝的导电特性, 在不同温度下对阻态1和阻态2的电阻进行了测试, 如果电阻随着温度的增加(温度由300 K升至350 K以10 K的增量递增)而增大, 则表现金属特性(Cu原子导电); 反之为半导体特性(氧空位导电), 如图4(c)是阻态1电阻随温度变化的趋势。随着温度的增加, 电阻呈现明显的上升趋势, 由此推测该阻态的导电方式具有金属导电特性。虽然在这里未显示阻态2的结果, 阻态2的电阻与温度的相关性也呈现出金属导电特性。由此可以推测出构成低阻态(阻态1及阻态2)的导电细丝是由Cu原子组成的。为了进一步排除氧空位导电模式的可能性, 明确Cu细丝导电作用, 用Al代替上电极Cu。图4(c)插图是Al/ $\text{SiO}_x$ /Al结构器件I-V测试结果。虽然限制电流设定在较低的100 nA, Al/ $\text{SiO}_x$ /Al器件电激活

之后,  $\text{SiO}_x$ 薄膜被硬击穿, 器件无法进行可逆操作。该结果说明本实验条件下制备的 $\text{SiO}_x$ 薄膜在缺乏Cu元素的条件下不具有阻变特性, 进一步说明制备的 $\text{SiO}_x$ 薄膜阻变机制不是氧空位模式。同时如图2所示, 由于制备的 $\text{SiO}_x$ 薄膜比较疏松, 有利于Cu在沉积过程中向 $\text{SiO}_x$ 薄膜中扩散。

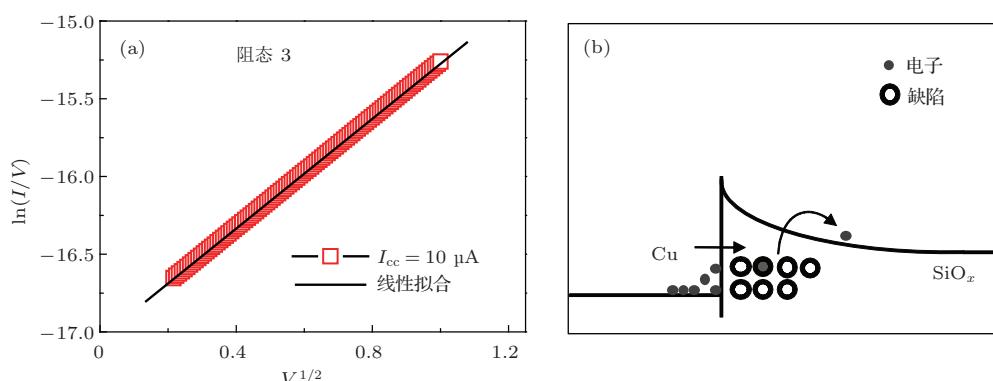

不同于阻态1和阻态2两个阻态, 阻态3不符合欧姆传导机制的拟合。因此对阻态3的I-V曲线进行了几种方式(肖特基发射、空间电荷限制电流、隧穿以及Pool-Frenkel(P-F)发射等)的电子传输机制拟合。如图5(a)所示,  $\ln(I/V)-V^{1/2}$ 关系曲线呈现良好的线性关系, 与P-F发射机制的拟合结果最为符合。P-F发射机制如图5(b)所示, 电子于Cu/ $\text{SiO}_x$ 界面处注入 $\text{SiO}_x$ 薄膜体内时, 由于薄膜体内存在大量的缺陷, 这些缺陷可作为复合中心(陷阱)优先俘获被注入的电子, 随着电场的增加, 这些被俘获的电子获得能量, 从陷阱中激发并跃迁到导带中参与传导。

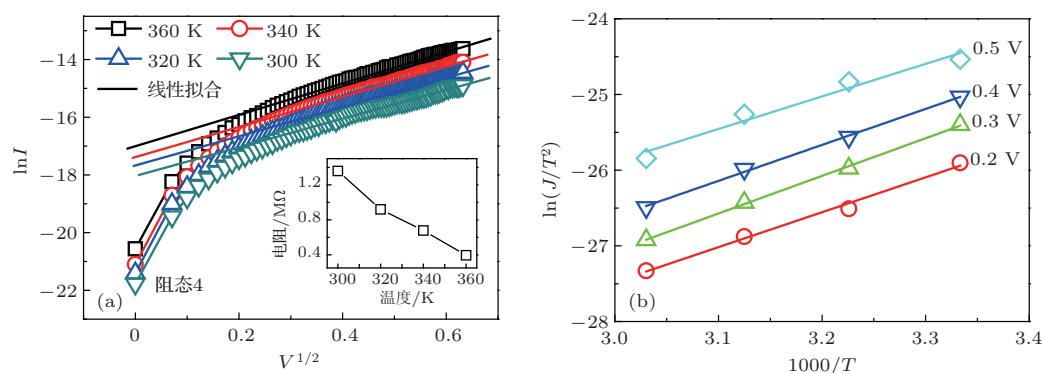

为了证明器件的阻态4(高阻态)的传导特性, 在不同温度下对阻态4的电阻值进行了测量。如图6中的插图所示, 电阻值随着温度的增加而降低,

图5 阻态3的P-F发射机制拟合曲线及P-F发射机制原理示意图 (a) 阻态3 P-F发射机制拟合曲线; (b) P-F发射原理示意图

图6 阻态4(高阻态)不同温度下的肖特基发射机制拟合 (a) 不同温度下在较高电压  $\ln(I)-V^{1/2}$  关系拟合曲线, 插图为阻态4电阻-温度关系曲线; (b) 肖特基发射的  $\ln(J/T^2)-1000/T$  关系拟合曲线

这说明在阻态4高阻态的电子传输机理是非金属特性的。因此可能的电子传输机制为半导体特性的欧姆传导、P-F发射或者肖特基发射机制。为了进一步确定阻态4高阻态的电子传输机制，在不同的温度(300—360 K)条件下，对阻态4高阻态分别进行了I-V测试，并对各个I-V曲线进行 $\ln I - V^{1/2}$ 关系拟合，如图6(a)所示，拟合结果显示在相对较高的电压(大于0.09 V)区域，其呈现较好的线性关系。其结果与肖特基发射机制比较一致，符合高阻态的电子传输过程。此外，如图6(b)所示，在不同电压下的 $\ln(J/T^2) - 1000/T$ 关系拟合结果也呈现线性，这种线性结果进一步证明肖特基发射是主导阻态4高阻态的电子传输机制。

### 3.4 阻变模型

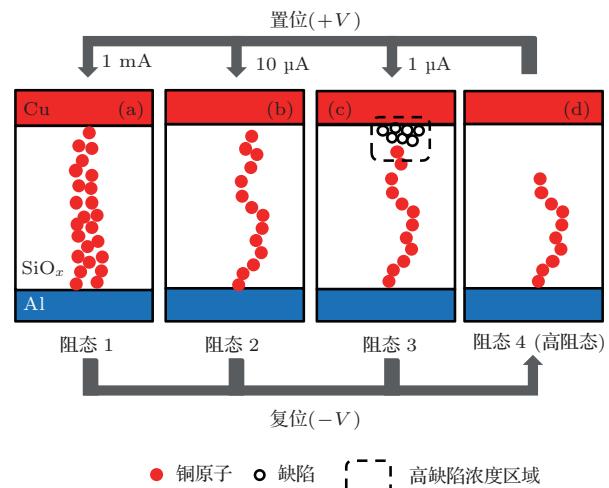

根据以上分析，Cu/SiO<sub>x</sub>/Al结构阻变器件四个阻态的电子传输机制可以解释为：阻态1和阻态2为欧姆传导机制，阻态3为P-F发射机制，阻态4为肖特基发射机制。在此基础上，为了进一步阐述多值阻变存储机理，利用图7建立了Cu/SiO<sub>x</sub>/Al结构阻变器件的多值阻变存储模型。如图7(a)所示，在置位过程中通过铜上电极给器件施加正向偏压，在电场作用下，铜电极的铜原子发生电化学反应失去电子被氧化成铜离子。在电场的驱动下带正电的铜离子向阴极移动，随后与电子结合重新还原为铜原子。由于尖端处电场相对较强，铜原子在尖端处堆积，致使铜细丝不断生长延伸。当限制电流较大时(阻态1和阻态2)，被注入的电子数量多，铜离子获得电子还原为铜原子的概率大，因此由被还原的铜原子组成的导电细丝连通上下电极，使得器件的电阻降低。当限流进一步减小到1 μA时(阻态3)，注入的电子数量受到限制，在一定程度上减小了铜离子与电子结合的概率，抑制了铜导电细丝的生长。如图7(c)所示，当铜导电细丝生长到接近连接Cu上电极时，由于尖端高强度的电场强度，使得尖端周围的缺陷浓度上升，电子更倾向于通过陷阱辅助发射进入导带(P-F发射)，电子一旦以P-F发射为主要传导机制，则更容易被缺陷陷阱所俘获。因此注入的电子与铜离子的结合受到抑制，限制了铜细丝的继续生长。加负向偏压的复位过程中，由于导电通道的大部分电阻集中在铜细丝尖端(阻态1和阻态2)或尖端与电极之间(阻态3)，电压主要集中在这些区域导致铜细丝在尖端的电流密度很

大产生大量焦耳热，在焦耳热的辅助及电场的作用下，在该区域更容易发生电化学分解，使铜原子电离致使导电细丝中断，从而器件回归到高阻状态(阻态4)。此时，由于铜导电细丝与SiO<sub>x</sub>的功函数的差异，电子需要越过两者间的势垒差才能够到达阳极，故此时的电子传输机制表现为肖特基发射。

图7 Cu/SiO<sub>x</sub>/Al结构阻变器件的多值阻变模型 置位时设定不同的限流：(a) 限流为1 mA，置位后为阻态1；(b) 限流为10 μA，置位后为阻态2；(c) 限流为1 μA，置位后为阻态3；(d) 复位后转变回阻态4(高阻态)

## 4 结 论

本文通过射频磁控溅射及电子束蒸发制备了Cu/SiO<sub>x</sub>/Al结构的阻变存储器件。通过调节限制电流可有效地控制复位电流大小，在1 μA—1 mA之间，设置3个不同的限制电流时，可以得到4个稳定的不同阻态，体现该结构具有多值存储特性。各阻态间的电阻比大于10并且表现出良好的数据保持能力及耐擦写能力。此外，进一步探索多值存储特性的物理机制，在不同的温度条件下对不同阻态进行了I-V测试及其曲线拟合。在阻态1和阻态2时，由于限制电流相对较大，注入的电子数量较多，易于形成铜细丝的导电通道，所以电子传输机制为欧姆传导机制；在阻态3时，由于限制电流相对较小，注入电子数量受限，抑制了铜导电细丝的形成和生长，最终导致了以P-F发射为主导的导电机制；在阻态4高阻态时，由于导电细丝完全断裂，所以电子传导是以热激发为主的肖特基发射。本文通过对Cu/SiO<sub>x</sub>/Al结构阻变器件多值特性的研究，揭示了其实现多值存储阻变器件的可行性，同时为多值阻变特性机理的研究提供了理论参考。

## 参考文献

- [1] Waser R, Aono M 2007 *Nat. Mater.* **6** 833

- [2] Waser R 2012 *J. Nanosci. Nanotechnol.* **12** 7628

- [3] Jeong D S, Thomas R, Katiyar R S, Scott J F, Kohlstedt H, Petraru A, Hwang C S 2012 *Rep. Prog. Phys.* **75** 076502

- [4] Yang J J, Strukov D B, Stewart D R 2013 *Nat. Nanotechnol.* **8** 13

- [5] Mikolajick T, Nagel N, Riedel S, Mueller T, Kuesters K H 2007 *Mater. Sci. Pol.* **25** 33

- [6] Wang Y, Liu Q, Long S, Wang W, Wang Q, Zhang M, Zhang S, Li Y, Zuo Q, Yang J, Liu M 2010 *Nanotechnology* **21** 045202

- [7] Schindler C, Thermadam S C P, Waser R, Kozicki M N 2007 *IEEE Trans. Electron Dev.* **54** 2762

- [8] Hwang S K, Lee J M, Kim S, Park J S, Park H I, Ahn C W, Lee K J, Lee T, Kim S O 2012 *Nano Lett.* **12** 2217

- [9] Li Y T, Long S B, Lu H B, Liu Q, Wang Q, Wang Y, Zhang S, Lian W T, Liu S, Liu M 2011 *Chin. Phys. B* **20** 017305

- [10] Liu Z Y, Zhang P J, Meng Y, Li D, Meng Q Y, Li J Q, Zhao H W 2012 *Chin. Phys. B* **21** 047302

- [11] Park J, Biju K P, Jung S, Lee W, Lee J, Kim S, Park S, Shin J, Hwang H 2011 *IEEE Electron Dev. Lett.* **32** 476

- [12] Choi S J, Park G S, Kim K H, Cho S, Yang W Y, Li X S, Moon J H, Lee K J, Kim K 2011 *Adv. Mater.* **23** 3272

- [13] Zhao J W, Liu F J, Huang H Q, Hu Z F, Zhang X Q 2012 *Chin. Phys. B* **21** 065201

- [14] Huang D, Wu J J, Tang Y H 2013 *Chin. Phys. B* **22** 038401

- [15] Russo U, Kamalanathan D, Ielmini D, Lacaia A L, Kozicki M N 2009 *IEEE Trans. Electron Dev.* **56** 1040

- [16] Liu M, Abid Z, Wang W, He X L, Liu Q, Guan W H 2009 *Appl. Phys. Lett.* **94** 233106

- [17] He C L, Shi Z W, Zhang L C, Yang W, Yang R, Shi D X, Zhang G Y 2012 *ACS Nano.* **6** 4214

- [18] Zhang Y, Wu H, Bai Y, Chen A, Yu Z, Zhang J, Qian H 2013 *Appl. Phys. Lett.* **102** 233502

- [19] Yoon J H, Han J H, Jung J S, Jeon W, Kim G H, Song S J, Seok J Y, Yoon K J, Lee M H, Hwang C S 2013 *Adv. Mater.* **25** 1987

- [20] Meng Y, Zhang P J, Liu Z Y, Liao Z L, Pan X Y, Liang X J, Zhao H W, Chen D M 2010 *Chin. Phys. B* **19** 037304

- [21] Wen X Z, Chen X, Wu N J, Ignatiev A 2011 *Chin. Phys. B* **20** 097703

- [22] Wei X Y, Hu M, Zhang K L, Wang F, Liu K 2012 *Acta Phys. Sin.* **61** 047201 (in Chinese) [韦晓莹, 胡明, 张楷亮, 王芳, 刘凯 2012 物理学报 **61** 047201]

- [23] Mehonic A, Cueff S b, Wojdak M, Hudziak S, Jambois O, Labbé C, Garrido B, Rizk R, Kenyon A J 2012 *J. Appl. Phys.* **111** 074507

- [24] Edelstein D, Heidenreich J, Goldblatt R, Cote W, Uzoh C, Lustig N, Roper P, McDevitt T, Motsiff W, Simon A, Dukovic J, Wachnik R, Rathore H, Schulz R, Su L, Luce S, Slattery J 1997 *Int. Electron Dev. Meeting 1997 IEDM Technical Digest* Washington DC, USA, Dec. 10–10, 1997 p773

# Multilevel switching mechanism for resistive random access memory based on Cu/SiO<sub>x</sub>/Al structure\*

Chen Ran Zhou Li-Wei Wang Jian-Yun Chen Chang-Jun Shao Xing-Long

Jiang Hao Zhang Kai-Liang Lü Lian-Rong<sup>†</sup> Zhao Jin-Shi<sup>‡</sup>

(School of Electronics Information Engineering, Tianjin Key Laboratory of Film Electronic and Communication Devices, Tianjin University of Technology, Tianjin 300384, China)

(Received 3 November 2013; revised manuscript received 6 December 2013)

## Abstract

In this paper, resistive switching device based on Cu/SiO<sub>x</sub>/Al structure is fabricated to examine its resistive switching characteristics and explore its resistive switching mechanisms. By adjusting limiting current, four stable resistance states are obtained. All of the resistive ratios between adjacent resistance states are over than 10. Moreover, the retention data of these four states at room temperature keep stable up to 1000 s. The temperature-dependent measurement and *I-V* curves fitting results show that the resistive switching mechanisms of the four states are different: resistance states 1 and 2 are due to Ohmic conduction mechanism, resistance state 3 is due to Pool-Frenkel emission, and resistance state 4 is due to Schottky emission mechanism. Subsequently, a resistive switching model for Cu/SiO<sub>x</sub>/Al structure is proposed.

**Keywords:** resistive random access memory, SiO<sub>x</sub> thin film, multilevel, resistive switching mechanism

**PACS:** 72.60.+g, 72.20.-i, 73.40.Cg, 73.40.Rw

**DOI:** 10.7498/aps.63.067202

\* Project supported by the National Natural Science Foundation of China (Grant Nos. 61274113, 11204212), the Program for New Century Excellent Talents in University, China (Grant No. NCET-11-1064), the Tianjin Natural Science Foundation, China (Grant Nos. 13JCYBJC15700, 13JCZDJC26100), and the Tianjin Science and Technology Developmental Funds of Universities and Colleges, China (Grant Nos. 20100703, 20130701).

† Corresponding author. E-mail: 163lvlianrong@163.com

‡ Corresponding author. E-mail: jinshi58@163.com