# 分子束外延生长 Si/GaP(111) 异质结的 界面特性\*

邓容平<sup>1)</sup> 蒋维栋 孙恒慧

复旦大学物理系

1988年7月14日收到

本文研究了分子束外延(MBE)生长的n-N型Si/GaP(III)异质结的界面特性。采用C-V法测量Si/GaP(III)异质结的表观载流子浓度分布 $n(x)$ ,从中导出了异质界面的导带失配值和界面电荷密度。实验结果表明,n-N型Si/GaP(III)是一种弱整流结构。导带失配 $\Delta E_c=0.10\text{eV}$ ,界面电荷密度 $\sigma_i=8.8\times 10^{10}\text{cm}^{-2}$ 。通过表观载流子浓度 $n(x)$ 的理论计算曲线与实验曲线符合较好,说明了实验结果的可靠性。

## 一、引言

在半导体异质结的研究及应用中,异质界面的能带失配及界面态的分布是两个重要的物理参数。从理论和实验方面确定这些参数是一件有意义的工作。半导体异质结的导带失配和价带失配数值与形成异质结的两种半导体材料、晶面取向及生长方法有关。对于同一种结构的异质结,不同的实验方法给出的能带失配值常不一致<sup>[1]</sup>。目前用于测量异质节能带失配的实验方法主要有下列四种:(1)超晶格光吸收技术<sup>[2,3]</sup>;(2)X射线光电子能谱技术<sup>[4,5]</sup>;(3)C-V测试方法<sup>[6,7]</sup>;(4)用于PIP结构的空穴热发射测量方法<sup>[8]</sup>。其中C-V测试方法是由Kroemer等人在1980年提出来的一种纯电学测量方法,它适用于同型异质结的测量。与其它方法相比较,C-V测试方法的测量手段简便,准确性较好,并且能同时测量能带失配值及界面电荷密度这两个重要物理量。

半导体异质结的界面缺陷分布能影响界面势垒及异质结的性能<sup>[9]</sup>。为了避免形成大量的界面缺陷,要求形成异质结的两种半导体材料应有尽量小的晶格失配。Si与GaP这两种半导体之间的晶格失配为0.36%,可以实现无界面位错的共度生长,因而对它的实验测量可望得到比较可靠的结果。本文采用C-V方法研究n-N型Si/GaP(111)异质结的导带失配和界面电荷密度,并与过去用其它实验方法和理论计算的结果进行了比较。

## 二、样品制备

实验所用的样品为用MBE技术在GaP衬底上外延生长Si的Si/GaP异质结。衬

\* 国家自然科学基金资助的课题。

1) 现在工作单位:新疆大学物理系。

底为 n 型 GaP 单晶片。载流子浓度约为  $4.0 \times 10^{17} \text{ cm}^{-3}$ 。Si 沿 GaP 的 (111) 方向生长。Si 的外延生长是在一台超高真空电子束蒸发装置中进行的，生长室的极限真空度为  $5 \times 10^{-9} \text{ Pa}$ ，生长时的真空度不低于  $1.0 \times 10^{-7} \text{ Pa}$ 。在外延生长之前衬底表面主要存在着 D 和少量 C 的沾污，在经过超高真空中  $620^\circ\text{C}$  的热处理之后，由俄歇电子能谱 (AES) 可知这些沾污已经去除。Si 的沉积速率为  $0.2\text{--}0.4 \text{ \AA/s}$  生长温度为  $450^\circ\text{C}$ ，生长厚度分别为  $0.5 \mu\text{m}$  和  $0.7 \mu\text{m}$ 。在 Si 的外延生长过程中，由 AES 可以观察到衬底的 P 和 Ga 在 Si 的外延表面层发生偏析。当 Si 外延层厚度达  $100 \text{ \AA}$  时，Ga 的讯号已低于 AES 的探测灵敏度，而 P 的讯号要到 Si 外延层的厚度达到  $1500 \text{ \AA}$  时才消失<sup>[10]</sup>。因此 P 偏析比 Ga 偏析严重，这种偏析会在 Si 外延层中造成浓度较大的自动掺杂。对于 Si 外延层厚度为  $0.5 \mu\text{m}$  和  $0.7 \mu\text{m}$  的样品，经检验后确定外延层的导电类型为 n 型。

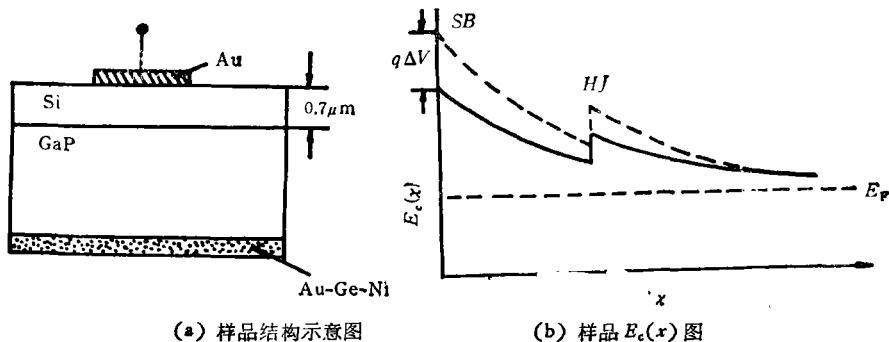

图 1

为了适合于  $C-V$  测试的要求，必须在 Si/GaP 样品的 Si 表面上制作肖特基势垒接触，其结平面与异质结平行，并在 GaP 的背面制作欧姆接触以便引出电极。图 1(a) 表示这样一种结构。样品的欧姆接触制备是先在 GaP 的非抛光面上蒸一层 Au-Ge-Ni 合金，然后将样品置于  $400^\circ\text{C}$  下，氮气保护中合金  $10\text{ min}$  而成。Si/GaP 异质结的生长是在  $450^\circ\text{C}$  下进行，所以在欧姆接触制备中的合金过程将不会影响 Si/GaP 异质结的内部结构特性，而且由于 GaP 的载流子浓度较高，约为  $4.0 \times 10^{17} \text{ cm}^{-3}$ ，因此用上述方法能够做出较好的欧姆接触。Si 表面的肖特基接触可采用在 Si 上蒸 Au 来形成。本文实验样品的 Si 外延层厚度有  $0.5 \mu\text{m}$  和  $0.7 \mu\text{m}$  两种。实验发现，在 Si 外延层厚度为  $0.5 \mu\text{m}$  的样品上采用这种方法制成的肖特基势垒很低。其原因是 Si 表面上存在着一层电子浓度很高的薄层，该薄层的形成可能与样品在 MBE 生长过程中 P 偏析有关。（此时 P 浓度已低于 AES 的探测灵敏度。）为了清除这一薄层，将样品在  $\text{HF:HNO}_3:\text{H}_2\text{O} = 1:3:5$  的溶液中腐蚀  $3\text{ min}$  了后，再于 Si 上蒸 Au，发现这时形成的肖特基势垒高度有明显的增加，适合于进行  $C-V$  测量。在样品的肖特基结制备过程中还发现，这种高电子浓度薄层随着外延层厚度的增加而减弱，对于 Si 层厚度为  $0.7 \mu\text{m}$  的样品，该薄层已基本消失。样品不需经  $\text{HF:HNO}_3$  溶液腐蚀，也能制作良好的肖特基接触。

### 三、表观载流子浓度分布 $\hat{n}(x)$ 与导带失配值 $\Delta E_c$

$C-V$  测试技术常用于测量半导体内部的载流子浓度分布<sup>[11,12]</sup>, 在金属与半导体接触的肖特基结中, 半导体一侧存在一个势垒区, 当施加于肖特基结上的反偏电压  $V$  变化  $\Delta V$  时, 势垒区的宽度由  $x$  变化至  $x + \Delta x$ , 近似认为  $\Delta x$  内的载流子被耗尽, 同时样品的电容发生相应变化。由实验测得样品电容随反偏电压  $V$  的变化曲线, 通过下列公式可求得半导体的载流子浓度分布:

$$n(x) = \frac{1}{q\epsilon\epsilon_0} \left[ C^3 / \left( \frac{\Delta C}{\Delta V} \right) \right], \quad (1)$$

$$x = \epsilon\epsilon_0/C, \quad (2)$$

式中  $\epsilon$  为半导体的相对介电常数,  $C$  表示样品在反偏电压为  $V$  时的单位面积微分电容,  $\epsilon_0$  为真空介电常数,  $q$  为电子电荷。但对于载流子浓度分布  $n(x)$  不均匀的半导体, 尤其是当  $n(x)$  在一个德拜长度内有较大变化时, 上述测量方法所给出的结果不能反映半导体内部真实的载流子浓度分布<sup>[13]</sup>, 而是  $n(x)$  在德拜长度范围内的平均值  $\hat{n}(x)$ ,  $\hat{n}(x)$  被称为表观载流子浓度分布。对于图 1(a) 所示的结构, 根据 Schottky-Anderson 模型, 其内部存在着两个势垒区, 分别位于肖特基接触的半导体一侧及异质结的界面处, 如图 1(b) 所示。在异质结的势垒区内, 德拜长度通常远大于这个区域的宽度, 而且在这个区域附近载流子浓度变化很大, 因此,  $C-V$  法在这个区域附近测得的载流子不代表这个区域内的真实分布, 而是一种表观载流子浓度分布  $\hat{n}(x)$ 。Kroemer 等人提出, 对于同型异质结, 可通过实验上测得的表观载流子浓度分布确定异质结的能带失配, 对于 n-N 型异质结, 采用下列公式计算导带失配  $\Delta E_c$  及界面电荷密度  $\sigma_i$ <sup>[6]</sup>:

$$\Delta E_c = q\Delta\phi - kT \ln \left\{ \frac{n(\infty)/N_c(\infty)}{n(-\infty)/N_c(-\infty)} \right\}, \quad (3)$$

$$\Delta\phi = -q \int_{-\infty}^{\infty} \frac{1}{\epsilon\epsilon_0} [\hat{n}(x) - N_d(x)](x - x_i) dx, \quad (4)$$

$$\sigma_i = - \int_{-\infty}^{\infty} [N_d(x) - \hat{n}(x)] dx, \quad (5)$$

式中  $x_i$  表示异质界面的位置,  $N_c$  为导带的有效态密度,  $n(\pm\infty)$  为远离异质界面处的载流子浓度,  $N_d(x)$  为浅施主杂质浓度。

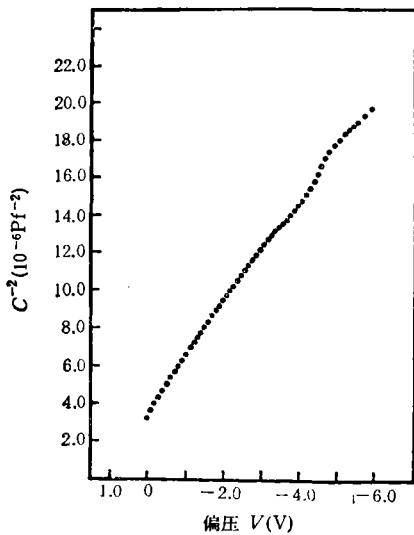

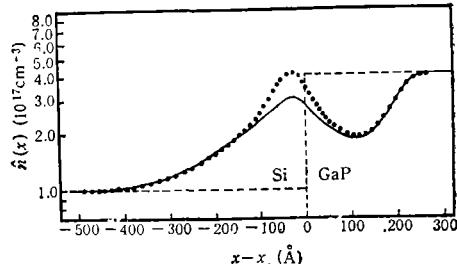

本文采用 HP 公司的 4275A 型多频率 RCL 表测量样品的反向  $C^{-2}-V$  特性, 该仪器能对样品的漏电流及串联电阻引起的电容测量误差进行校正。图 2 为实验测得的 Si 外延层厚度为  $0.7\mu\text{m}$  的样品的反向  $C^{-2}-V$  曲线。测试温度为  $300\text{K}$ , 测试频率为  $1\text{MHz}$ 。图 3 为由  $C-V$  特性及(1)和(2)式计算得到的样品的表观载流子浓度分布。从图 3 可以看出, MBE 生长的 Si/GaP 异质结中 Si 外延层的载流子浓度小于 GaP 的载流子浓度, 在界面处, Si 一侧存在着一个积累区, GaP 一侧为耗尽区。在远离异质界面处, 载流子浓度分布较为均匀。

半导体中的掺杂浓度  $N_d(x)$  通常是不能预先知道的, 这是采用  $C-V$  法测量异质结

图 2  $C^{-2}$ -V 特性曲线  $f = 1\text{MHz}$ ;  $T = 300\text{K}$ 图 3 表观载流子浓度分布  $n(x)$ - $x$  图表 1  $\Delta E_c$  和  $\sigma_i$  的测量结果

|                                 |                      |                      |

|---------------------------------|----------------------|----------------------|

| Si 外延层厚度 ( $\mu\text{m}$ )      | 0.7                  | 0.5                  |

| $\Delta E_c$ (eV)               | 0.10                 | 0.089                |

| $\sigma_i$ ( $\text{cm}^{-2}$ ) | $8.8 \times 10^{10}$ | $6.7 \times 10^{10}$ |

导带失配的一个局限。在应用中，常近似认为样品是突变异结，在界面两侧的半导体分别为均匀掺杂， $N_d(x)$  为常量。由于在远离结区处载流子浓度的分布较为均匀，因此由  $N_d = n(\infty) = \hat{n}(\infty)$  可以确定出界面两侧半导体的掺杂浓度。由图 2 可求得 Si 外延层中的施主杂质浓度为  $1.0 \times 10^{17} \text{cm}^{-3}$ 。GaP 的施主杂质浓度为  $4.0 \times 10^{17} \text{cm}^{-3}$ 。异质界面位于  $\hat{n}(x)$  的峰值附近<sup>[6]</sup>。根据这些数据及表观载流子浓度的分布  $\hat{n}(x)$ ，由(3)–(5) 式可计算出 Si/GaP(III) 异质结的导带失配值  $\Delta E_c$  及界面电荷密度  $\sigma_i$ 。表 1 列出对两种不同外延层厚度的样品的测量结果。

为了检验实验结果的可靠性，本文通过求解 Poisson 方程  $d^2\phi/dx^2 = -(q/\epsilon\epsilon_0)[N_d(x) - n(x)]$  计算表观载流子浓度分布的理论曲线<sup>[14]</sup>，将其与实验测量曲线进行比较。在理论计算中假定样品为突变异质结，在异质界面处有边界条件

$$E_{c1} + \Delta E_c = E_{c2}, \quad (6)$$

$$\epsilon_1\epsilon_0\epsilon_1 + \sigma_i = \epsilon_2\epsilon_0\epsilon_2, \quad (7)$$

式中  $E_{c1}$ ,  $E_{c2}$  分别为界面处 Si 及 GaP 的导带底能量， $\epsilon_1$ ,  $\epsilon_2$  分别为界面处 Si 及 GaP 的电场强度， $N_d(x)$ ,  $\Delta E_c$  和  $\sigma_i$  由实验结果给出。对于 Si 层厚度为  $0.7 \mu\text{m}$  的样品，其表观载流子浓度分布的理论计算结果如图 3 中的点线所示。理论曲线与实验曲线基本符合，仅在界面附近略有偏差，但从总体上看这个偏差是比较小的，说明本文实验结果是可靠的。在理论计算中，本文采用理想的突变异质结模型，并且认为半导体内的施主杂质浓度  $N_d(x)$  在界面两侧分别是均匀的。这些假设与实际样品略有差别，因此反映在  $\hat{n}(x)$  的理

论计算曲线与实验曲线略有差异。

#### 四、讨 论

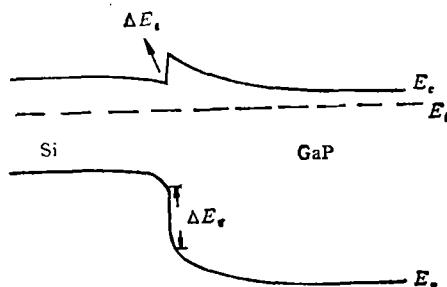

本文的实验结果表明，对于 n-N 型 Si/GaP(111) 异质结， $\Delta E_v = 0.10\text{eV}$ ，导带的失配比较小，它是一种弱整流结构。由于 Si 与 GaP 这两种半导体材料之间的禁带宽度相差较大，

$$\Delta E_g = \Delta E_v + \Delta E_s \approx 1.1\text{eV}. \quad (8)$$

因此，这种结构的能带失配主要发生在价带上。图 4 表示出这样一种能带结构。

关于 Si/GaP 异质结的价带失配，理论计算方面有过许多模型和方法，彼此之间并不相符。其中 Frensel 和 Kroemer 的计算结果为  $\Delta E_v = 0.96\text{eV}$ ，但没有指明 GaP 的晶向<sup>[15]</sup>。黄春晖等人的理论计算结果表明，能带失配从理论上讲是与晶向有关的<sup>[16]</sup>，对于 Si/GaP(111) 结构，价带失配值为  $\Delta E_v = 0.97\text{eV}$ 。这两个计算工作所给出的结果与本文的实验测量符合较好。在实验方面，只有 Margaritondo 小组用 X 射线光电子能谱技术测量过 Si/GaP 的价带失配，但先后发表的数据不同。他们所测量的样品是在 GaP 上淀积  $10\text{\AA}$  厚的 Si 的 Si/GaP(110) 结构，测得的价带失配值为  $\Delta E_v = 0.95\text{eV}$ <sup>[17]</sup> 和  $\Delta E_v = 0.8\text{eV}$ <sup>[18]</sup>。可以肯定 Si/GaP 异质结的能带失配主要发生于价带上。

与 X 射线光电子能谱技术测量方法比较，C-V 方法的测量手段简便，但实验结果的可靠性在一定程度上依赖于模型的正确性。X 射线光电子能谱技术测量结果比较准确，但只能测量外延层厚度为几十埃的结构。用 C-V 方法测量的是外延层厚度达数千埃的异质结，其结果更接近于实际器件。

图 4 Si/GaP(III) 能带结构

- [1] A. G. Milness, *Solid State Electron.*, 29(2), (1986), 99.

- [2] R. Dingl, W. Wiegmann and C. H. Henry, *Phys. Rev. Lett.*, 33(1974), 827.

- [3] R. Dingl, A. G. Gossard and W. Wiegmann, *Phys. Rev. Lett.*, 34(1975), 1327.

- [4] G. Margaritondo, A. D. Katnani, N. G. Stoffel, R. R. Daniel and T. X. Zhao, *Solid State Commun.*, 43(1982), 163.

- [5] E. A. Kront, R. W. Grant, J. R. Ealdrop and S. P. Kowalczyk, *Appl. Phys. Lett.*, 44(1980), 1620.

- [6] H. Kroemer, W. Y. Chen, J. S. Harris, Jr. and D. D. Edwall, *Appl. Phys. Lett.*, 36(1980), 295.

- [7] H. Kroemer, *Appl. Phys. Lett.*, 46(1985), 504.

- [8] S. L. Wright and J. Baley, *J. Appl. Phys.*, 57(1985), 484.

- [9] H. Kromer, *Surface Science*, 132(1983), 543.

- [10] Weidong Jiang, Guoliang Zhuo, Keming Chen, Chi Sheng, Xiangju Zhang and Xun Wang, *Appl. Phys. Lett.*, 51(1987), 1910.

- [11] D. P. Kennedy, P. C. Murley and W. Kleinfelder, *IBM J. Res. Dev.*, 12(1968), 399.

- [12] M. Nishida, *IEEE Trans. Electron Dev.*, ED-26(1979), 1081.

- [13] W. C. Johnson and P. T. Panousis, *IEEE Trans. Electron Dev.*, ED-18(1971), 965.

- [14] M. Missons and E. H. Rhoderich, *Solid State Electron.*, 28(1985), 233.

- [15] W. R. Frensel and H. Kroemer, *Phys. Rev.*, B16(1977), 2642.

- [16] Chunhui Huang, Ling Ye and Xun Wang, *J. Phys.: Condens. Matter*, 1(1989), 907.

- [17] A. D. Katnani and G. Margaritondo, *Phys. Rev.*, B28(1983), 1944.

- [18] P. Perfetti, F. Patella, F. Sette, C. Quaresime, C. Capasso, A. Saroia and G. Margaritondo, *Phys. Rev.*, B30(1984), 4533.

## INTERFACIAL PROPERTIES OF Si/GaP(111) HETEROJUNCTION GROWN BY MOLECULAR BEAM EPITAXY

DENG RONG-PING JIANG WEI-DONG SUN HENG-HUI

*Department of Physics, Fudan University, Shanghai*

(Received 14 July 1988)

### ABSTRACT

In this paper, the interfacial properties of n-N type Si/GaP(111) heterojunction prepared by MBE growth have been studied. The conduction band offset and the interface charge density are derived from the apparent carrier concentration distribution obtained by the *C-V* profiling technique. The experimental result shows that the n-N type Si/GaP(111) forms a weak rectifying contact. The conduction band offset is  $\Delta E_c = 0.10\text{eV}$  and the interface charge density is  $\sigma_i = 8.8 \times 10^{10}\text{cm}^{-2}$ . A theoretical simulation of the apparent carrier concentration distribution coincides well with the experimental curve, this confirms the reliability of our results.