# MOS 结构中薄栅氧化层高场退火效应的研究\*

张进城 郝 跃 朱志炜

(西安电子科技大学微电子研究所, 西安 710071)

(2001 年 2 月 7 日收到, 2001 年 3 月 16 日收到修改稿)

深入研究了 MOS 结构中薄栅氧化层在高电场下的退火效应, 对氧化层陷阱电荷的退陷阱机理进行了深入探讨, 通过实验和模拟对氧化层陷阱电荷的退陷阱机理和生长机理进行了比较, 给出了满意的物理解释, 负栅压退火和正栅压退火的比较表明负栅压退火更为有效.

关键词: MOS 结构, 薄栅氧化层, 高场退火, 退陷阱

PACC: 7360H, 0710

## 1 引 言

随着集成电路集成度的不断增加, MOS 器件尺寸不断等比缩小, 器件的栅氧化层变得越来越薄. 目前主流  $0.25\mu\text{m}$  工艺的氧化层通常为  $4 \sim 5\text{nm}$ . 由于栅氧化层很薄, 为了确保 MOS 器件的良好特性, 对栅氧化层质量的要求会更高.

氧化层陷阱和界面态是引起栅氧化层失效以致器件失效的主要机理. 氧化层缺陷的产生有两种途径 制造工艺和工作状态. 制造工艺中主要是氧化层生长工艺和离子注入会形成氧化层缺陷, 但是通过氧化层生长工艺的改进和高温退火可以大大减少这些缺陷从而提高氧化层的质量, 目前的工艺已经能够制造出质量很好的薄氧化层. 然而 随着器件沟道长度的减小, MOS 器件的内部电场不断增强, 所以工作状态会引起氧化层损伤, 而且工作状态对氧化层的影响越来越严重, 目前工作状态已经成为影响氧化层从而限制器件寿命的主要因素.

在器件工作状态下引起栅氧化层损伤的主要机理是热载流子效应. 由于器件沟道横向电场和纵向电场的作用, 沟道载流子和雪崩产生载流子会向栅氧化层方向发射, 达到栅氧化层的载流子一部分会在  $\text{Si-SiO}_2$  界面产生新的界面态, 有一部分会注入到栅氧化层中, 注入到氧化层中的载流子一部分被氧化层中性陷阱所俘获, 一部分到达栅电极而形成栅

电流. 然而以往有关 MOS 器件热载流子效应的研究已经很多, 而且对于热载流子引起界面态和氧化层陷阱电荷的生长机理已经得到了满意的结果.

不管怎样改进器件工艺、器件结构以及器件的工作条件, 热载流子效应对氧化层的损伤都会随着工作时间的增加而不断积累, 从而使器件到达它的寿命. 为了能够增加器件的寿命, 也可以对已经工作了一段时间的器件进行退火, 使积累的损伤得到一定的恢复. 在制造工艺过程中通常是把还没有做好的裸露器件放在高温的氢气气氛中进行退火, 但是对于已经封装好而且工作了一段时间的器件, 这种方法显然不可行, 需要寻找新的方法.

Brox 等<sup>[1,2]</sup> 已经验证 在栅氧化层两端施加一个高电场可以释放氧化层中的陷阱电荷. 对应力后的器件施加一个高电场, 器件特性可以得到部分恢复. 然而, 不管是 NMOS( n 型 MOS 场效应晶体管) 器件还是 PMOS( p 型 MOS 场效应晶体管) 器件, 主要的氧化层陷阱电荷都是陷阱电子<sup>[3]</sup>. 而且以前的研究<sup>[2]</sup> 已经发现在高场退火过程中氧化层陷阱电子的数量会减少, 但是界面态基本不受高场退火的影响. 然而 到目前为止, 有关氧化层陷阱电子退陷阱的基本机理和不同电场下的退火效应研究得不多, 也不够深入.

为了深入研究不同电场下氧化层陷阱电子的退陷阱机理, 本文首先研究了高场退火期间 MOS 器件参数退化随时间的恢复规律, 由此可以间接得到退火期间氧化层陷阱电子的退陷阱机理, 然后通过器

\* 中国国防科技预研项目(批准号 8.5.3.4).

件模拟软件对上述得到的退陷阱机理进行验证.由于在 NMOS 器件中界面态是主要的退化机理,所以氧化层陷阱电子退陷阱效应对器件特性的影响不是很明显,而 PMOS 器件主要的热载流子退化机理是氧化层陷阱电子,所以本文通过研究 PMOS 器件在退火期间的特性变化来得到氧化层陷阱电子退陷阱的基本机理,这对于其他 MOS 结构器件都有很好的借鉴意义.

## 2 高场退火效应

本文所用器件是采用  $0.8\mu\text{m}$  硅栅 CMOS 工艺制造的表面沟道 PMOS 器件,掩埋沟道长度为  $0.8\mu\text{m}$ ,沟道宽度为  $50\mu\text{m}$ ,栅氧化层厚度为  $17.5\text{nm}$ .

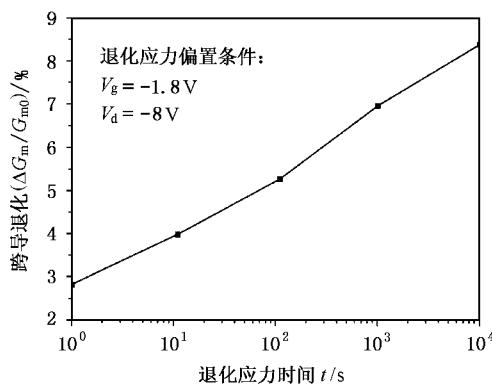

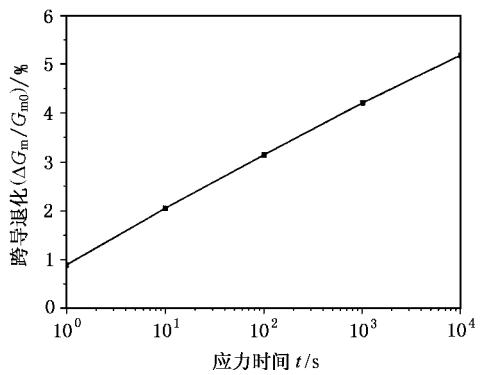

在进行高场退火以前对所有器件施加一个  $10000\text{s}$  的最大栅电流应力.应力期间器件跨导随应力时间的退化如图 1 所示.跨导  $G_m$  为最大线性区跨导,通过线性区特性测量得到.器件线性区特性的测量条件为:  $V_d$  为  $-0.1\text{V}$ ,  $V_g$  从 0 到  $-5\text{V}$  变化.从图 1 可以看出,退化应力期间跨导退化量和时间对数成线性关系,即器件跨导以对数线性时间规律增大.

图 1 最大栅电流应力期间器件跨导的退化

然后对刚刚经历最大栅电流退化应力的器件立即进行高场退火实验.

为了有效地得到退火期间器件参数退化的时间规律,避免其他因素的影响,退火实验所用器件均是在经过热载流子应力后立即进行高场退火实验.本文所加的退火栅电压有两种,一种是  $9\text{V}$  的正栅电压,一种是  $-9\text{V}$  的负栅电压,退火时间均为  $10^5\text{s}$ .退火期间器件其他各端均接地.

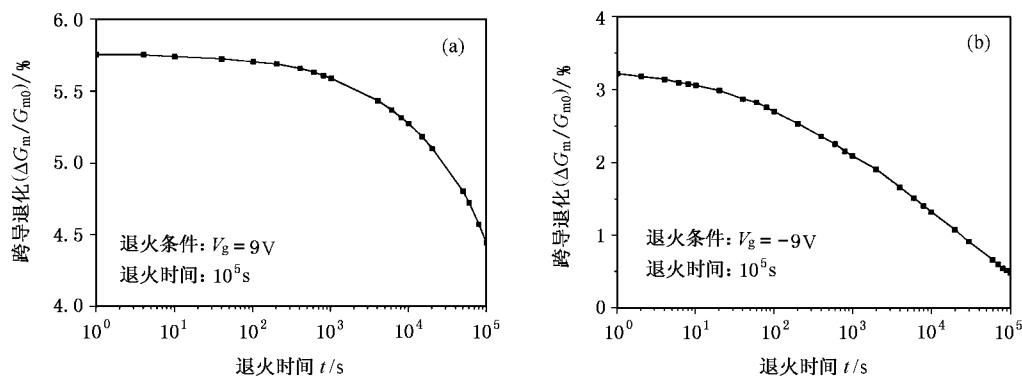

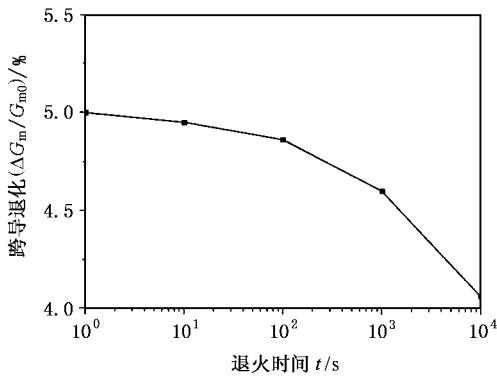

图 2 给出了高场退火期间跨导退化随退火时间的变化规律,其中,图 2(a)给出的是正栅电压退火的情况,而图 2(b)给出的是负栅电压退火情况.表 1 给出了经过  $10^5\text{s}$  高场退火以后器件跨导退化的相对变化量.从图 2 和表 1 中可以得出器件跨导退化随退火时间的变化规律,下面给出详细描述.

表 1 退火期间器件跨导退化量的变化

| $(\Delta G_m / G_{m0}) \%$ | $V_g = 9\text{V}$ |      |       | $V_g = -9\text{V}$ |      |       |

|----------------------------|-------------------|------|-------|--------------------|------|-------|

|                            | 退火前               | 退火后  | 变化量   | 退火前                | 退火后  | 变化量   |

|                            | 5.78              | 4.44 | -1.34 | 3.33               | 0.51 | -2.82 |

从图 2 中可以看出,不管是正栅压退火还是负栅压退火,跨导退化与退火时间对数都不是单纯的线性关系,这与退化应力期间跨导的退化规律有很大的不同.不管是负栅电压退火还是正栅电压退火,器件跨导都是向负向漂移,即器件跨导的退化量不断减小,  $I-V$  特性不断恢复.在线性-对数坐标系中,退火时间不是很长时,退化恢复比较缓慢,当退火时间很长时,退化恢复不断加速.但是负栅电压下跨导退化的恢复明显比正栅压下快.从表 1 可以看出,经高场退火以后,对于正栅压退火,跨导退化恢复  $1.34\%$ ,而对于负栅压退火,跨导退化恢复  $2.82\%$ .这表明,负栅压退火的效果要比正栅压退火的效果好得多.

有一点需要说明,从图 2(a)和(b)的比较可以看出,退火前的器件跨导退化量是不同的,正栅压退火器件的退火前退化量为  $5.78\%$ ,而负栅压退火器件的退火前退化量为  $3.33\%$ ,这主要是因为这两条曲线是通过两个不同器件得到的.虽然两个器件工艺和结构完全相同,但是两个器件处于不同的圆片上,由于国内器件工艺的落后现状,所以不同器件的本征氧化层中性陷阱数量是有差异的,因此在相同应力条件下不同器件所能达到的退化量是有一定差异的,但是其退化机理没有本质的区别,这已经经过大量的实验验证.

## 3 高场退火机理的模拟

从图 1 可以得出最大栅电流应力下 PMOS 器件跨导随时间以对数线性规律退化,这是因为 PMOS 器件的热载流子退化主要受到氧化层陷阱负电荷即陷阱电子的影响,跨导退化表现为正向漂移.在最大

图 2 高场退火期间器件跨导退化与退火时间的关系

栅电流应力下进入栅氧化层的电子会不断地陷落到中性陷阱中,由于在漏结附近注入的电子密度最大,所以漏结附近的栅氧化层中的陷阱首先被填充,很快漏结上面的氧化层陷阱电子填充达到动态饱和,这样随着应力时间的继续,陷阱填充区开始以对数时间规律向源区扩展,正是这种电子填充区向源区的对数扩展决定了跨导退化与应力时间的对数线性关系。

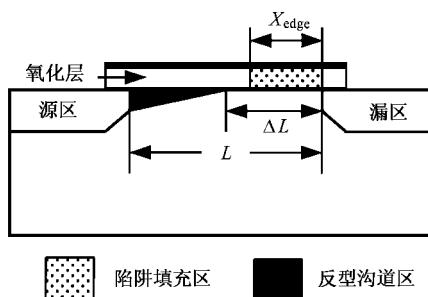

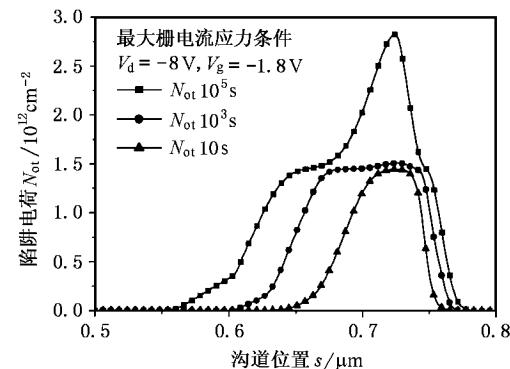

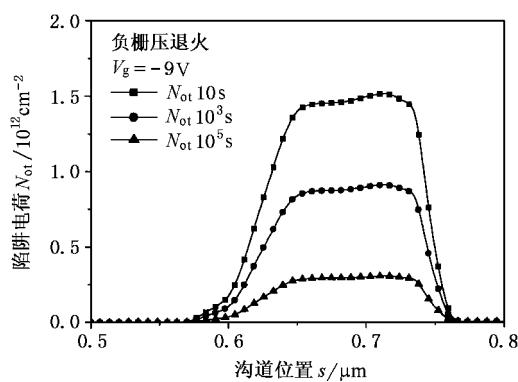

首先通过二维器件模拟器 MEDICI 模拟最大栅电流应力下氧化层陷阱电子的生长规律。模拟时,将栅氧化层分为两部分:未损伤区和损伤区(如图 3 所示)。图 3 中,  $L$  为有效沟道长度,  $\Delta L$  为沟道夹断区长度,  $X_{edge}$  为氧化层陷阱填充区长度。可以假设在未损伤区不存在氧化层陷阱电子,而在损伤区氧化层陷阱电子均匀分布。图 4 和图 5 分别给出了模拟得到的退化应力期间氧化层陷阱电荷  $N_{ot}$  的生长规律和退火期间氧化层陷阱电荷  $N_{ot}$  退陷阱的规律。图 4 和图 5 中给出的氧化层陷阱电荷分布情况是以模拟得到的器件特性曲线和测量得到的特性曲线相互符合为基准的,所以图 4 和图 5 给出的氧化层陷阱电子分布可以反映器件氧化层电荷分布的真实情况。

图 3 退化后的 PMOS 器件

图 4 退化期间氧化层陷阱电荷的生长模拟

从图 5 中可以看出,高场退火期间,器件氧化层陷阱电子退陷阱的规律明显不同于陷阱电荷生长的规律。最大栅电流应力下氧化层陷阱电子的生长主要表现为注入电子首先填充漏结附近的氧化层,然后陷阱填充区逐渐向源区扩展。而高场退火期间,由于所加的应力偏置不同于退化应力,此时只有栅电极上施加电压,所以氧化层纵向电场沿着沟道长度基本呈均匀分布,所以在陷阱填充区陷阱电荷的退陷阱规律表现为陷阱电子密度的整体下降(如图 5 所示)。这也就决定了高场退火期间器件跨导退化随退火时间的变化具有不同的规律。

图 6 和图 7 分别给出了模拟得到的退化应力期间和退火应力期间跨导退化量随时间的变化关系。通过模拟结果和实验测量结果的比较,可以发现模拟结果能够很好反映实验测量得到的器件跨导退化量与时间的关系。

#### 4 不同偏置下的高场退火效应

在讨论了正栅压退火效果的实验基础上,图 8

图 5 退火期间氧化层陷阱电荷退陷阱的模拟

图 6 应力过程中跨导退化的模拟

图 7 退火过程中跨导退化的模拟

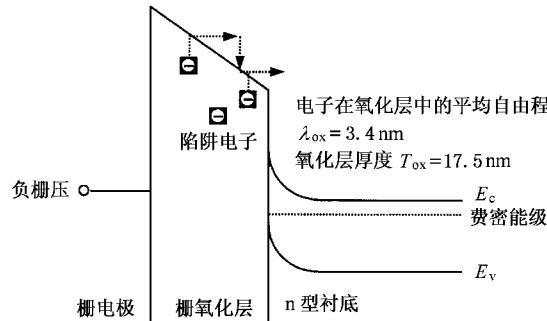

给出了负栅电压退火时氧化层和衬底中的能带图. 图 8 也标出了氧化层陷阱电荷退陷阱的基本机理. 氧化层电场的强弱直接影响氧化层陷阱电子退陷阱的效率和速率, 所以高氧化层电场可以增强退陷阱效应. 从图 8 中可以看出, 氧化层中有电场存在时, 能带就会发生弯曲, 电场越强, 能带弯曲越厉害, 在

氧化层高电场的作用下, 能够摆脱陷阱束缚的电子就会很快地进入衬底中, 使原来带负电性的陷阱电子再次成为中性陷阱, 氧化层陷阱电荷的减少必然引起器件退化的恢复. 高氧化层电场的存在可以增强这种退陷阱效应. 正栅电压下陷阱电子的退陷阱机理和负栅电压下的基本相同, 唯一不同的是在正栅电压下从陷阱中逃逸出来的电子是漂向栅电极, 而在负栅压下是漂向衬底. 由于在退化过程中, 在氧化层中陷落的电子主要来自于从衬底注入栅氧化层的热电子, 所以栅氧化层中邻近衬底一边的氧化层陷阱的填充率较高, 即在氧化层厚度方向上邻近衬底一边氧化层陷阱电荷的密度较高. 在正栅压下, 邻近栅电极一边的陷阱电子容易退陷阱, 而在负栅压下邻近衬底一边的陷阱电子容易退陷阱, 再加上邻近衬底一边的陷阱电荷对器件特性影响较大, 所以这决定了负栅压下器件的退火效果要好于正栅压的退火效果.

图 8 陷阱电子退陷阱的基本机理

这种高场退陷阱效应也与温度有关, 当温度较高时, 陷阱电子更容易逃逸陷阱的束缚, 所以高温下退陷阱效应更强<sup>[2]</sup>.

## 5 结 论

本文首先给出了正负栅电压退火下 PMOS 器件跨导退化恢复的测量结果, 然后通过模拟对氧化层陷阱电荷的生长机理和退陷阱机理进行了深入研究, 并给出了一个满意的结果. 通过比较可以看出, 模拟结果与实验结果的变化规律是一致的, 这说明给出的物理解释能够很好地说明实验结果. 最后从退陷阱的基本物理过程出发给出了负栅压退火好于正栅压退火的本质原因.

- [ 1 ] M. Brox , A. Scherlin , Q. Wang , W. Weber , *IEEE Trans . Electron Devices* , **41** ( 1994 ) , 1184.

- [ 2 ] Y. Pan , Proceeding of the 1993 IEEE International Reliability Physics Symposium ( 1993 ) , p.43.

- [ 3 ] T. C. Ong , P. K. Ko , C. Hu , *IEEE Trans . Electron Devices* , **37** ( 1990 ) , 1658.

## STUDY ON HIGH ELECTRIC FIELD ANNEALING EFFECT IN THIN GATE OXIDE OF MOS STRUCTURE<sup>\*</sup>

ZHANG JIN-CHENG HAO YUE ZHU ZHI-WEI

( Institute of Microelectronics , Xidian University , Xi 'an 710071 , China )

( Received 7 February 2001 ; revised manuscript received 16 March 2001 )

### ABSTRACT

High electric field annealing effect in thin gate oxide of MOS structure is studied in depth , and the detrapping mechanisms of trapped charge in the gate oxide are investigated. Comparison between the growth mechanism and the detrapping mechanism of trapped charge in gate oxide is made by experiments and simulations. A satisfactory physical description is presented for explaining this effect. Comparison between annealing under negative and positive gate voltages shows that the former is more effective .

**Keywords** : MOS structure , thin gate oxide , high electric field annealing , detrapping

**PACC** : 7360H , 0710

<sup>\*</sup> Project supported by the Chinese Defense Advanced Research Program ( Grant No.8.5.3.4 ).