## 研究快讯

# InAs 量子点在肖特基势垒二极管输运特性中的影响 \*

李宏伟 王太宏

(中国科学院物理研究所, 北京 100080)

(2001年6月29日收到 2001年8月4日收到修改稿)

在 77 到 292 K 的范围内, 系统研究了含 InAs 自组装量子点的金属-半导体-金属双肖特基势垒二极管的输运特性。随着温度上升, 量子点的存储效应引起的电流回路逐渐减小。在测试温度范围内, 通过量子点的共振隧穿过程在电流-电压( $I-V$ )曲线中造成台阶结构, 且使电流回路随温度的上升急剧减小。根据肖特基势垒的反向  $I-V$  曲线, 计算了势垒的反向饱和电流密度和平均理想因子。发现共振隧穿效应使肖特基势垒在更大的程度上偏离了理想情况, 而量子点的电子存储效应主要改变了肖特基势垒的有效势垒高度, 从而影响了势垒的反向饱和电流密度。

关键词: 自组装量子点, 肖特基势垒, 电流-电压特性

PACC: 6865, 7360L, 7340S

## 1 引言

因为低维量子结构具有各种新的性质和特点, 在器件方面有很广的应用前景, 得到了人们广泛的研究<sup>[1-3]</sup>。其中, 利用自组装方法生长的半导体量子点结构具有制备方便、与传统半导体器件的工艺兼容性好等优点, 人们对生长<sup>[4]</sup>和光学性质<sup>[5]</sup>和应用的研究不断深入<sup>[6]</sup>。在通过量子点的电学输运性质方面的研究还相对较少<sup>[7,8]</sup>。我们曾经报道含单层量子点的双肖特基势垒二极管的输运特性, 观察到并分析了量子点充放电效应引起的电流回路现象<sup>[9]</sup>。本文中我们将进一步讨论器件的电学输运特性随温度变化的情况。根据肖特基势垒的反向特性, 分析了量子点对肖特基势垒的理想因子和反向饱和电流的影响。观察到了通过量子点的共振隧穿效应减弱了量子点对电子的存储能力, 从而使电流迟滞回路减小。对肖特基势垒而言, 通过量子点的共振

隧穿使其偏离理想状况, 而量子点的电子存储效应主要表现为影响肖特基势垒的有效势垒高度, 从而影响肖特基势垒的反向饱和电流密度。

## 2 器件测试结果

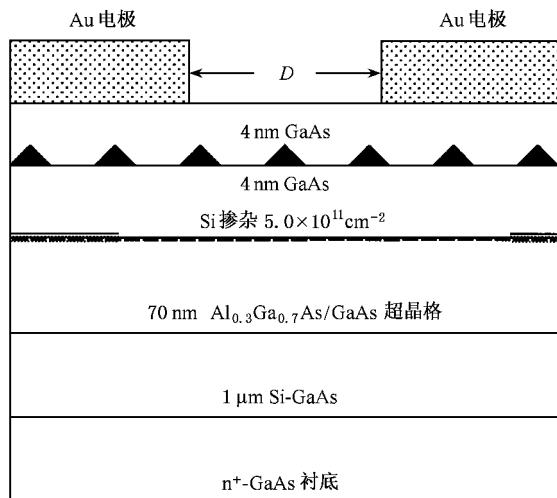

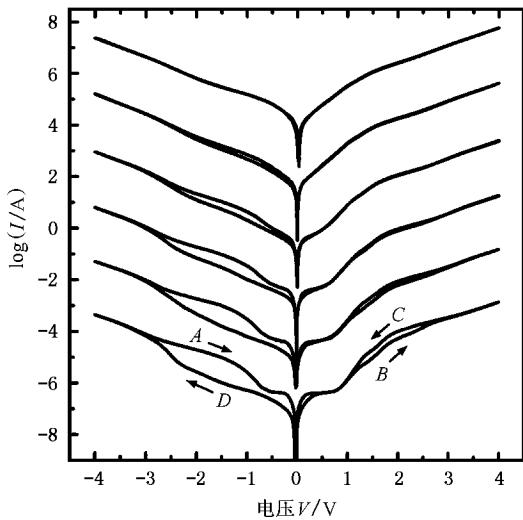

在图 1 中给出了器件的结构示意图, 为金属-半导体-金属(MSM)的双肖特基二极管结构, 测试在表面电极之间进行, 详细的生长和制作过程见文献[9]。图 2 中给出了器件在对数坐标时不同温度下的  $I-V$  曲线, 图 2 中由下向上每条曲线有两个数量级的位移, 对应的温度依次为 77, 110, 160, 205, 255 和 292 K。所有的曲线在多次测量时是重复的。在文献[9]中我们主要讨论了 77 K 下量子点中单电子存储现象所造成的电流回路效应, 这里我们主要研究器件的输运特性随温度的变化情况。

如图 2 所示, 77 K 下的  $I-V$  曲线根据电压扫描方向和电流大小可分为 A, B, C 和 D 四段, 图 2 中

\* 国家自然科学基金(批准号 69925410 和 19904015)资助的课题。

图 1 金属-半导体-金属器件结构示意图

图 2 MSM 二级管在不同温度下的  $I-V$  特性曲线 由下至上依次有两个数量级的平移

箭头示出了电压扫描方向。其他温度下的曲线具有相同特征，也可依此分段。我们已作过讨论<sup>[9]</sup>，电流迟滞回路是由量子点的充放电引起的，在负向电压范围(-4.0—0 V，曲线 A, D 部分)电流较小，对应的是面积较小的元，而在正向电压范围(0—4.0 V 之间，曲线 B, C 部分)电流大，是由面积较大的元决定的，在对数坐标下它对应的电流回路较小，且在这两条曲线上能观察到两个明显的台阶结构。我们在生长量子点的过程中采用了衬底旋转的方法，量子点生长较为均匀。根据我们的 MSM 器件结构，面积较大的元对应的电流回路也应该较大，只有电流对面积归一化之后进行比较，才能保证电流

密度曲线给出类似大小的回路。但从图 2 中可看出，对应电流大的曲线(正向偏压部分)的回路在对数坐标下相对较小，从 1.2 V 延伸到约 2.6 V，随着温度的上升减小较快，在 205 K 时基本上消失。而面积较小的元对应的电流回路从 0 V 延伸到约 3.0 V 且随着温度上升缓慢减小。

### 3 分析讨论

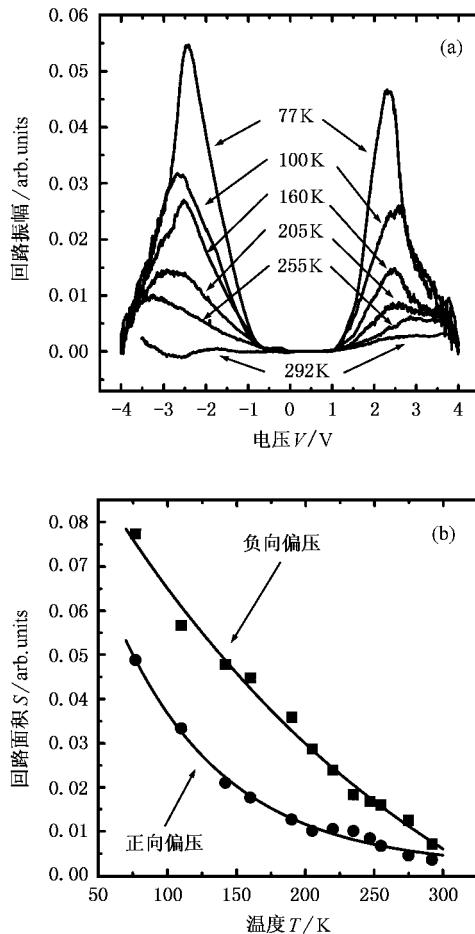

下面我们分析电流回路大小随温度的变化。一般而言，电流回路大小受两个主要因素的影响：1)一定温度时，通过 Au-GaAs 肖特基势垒的平均电流密度；2)样品中量子点的面密度。为了比较不同温度下电流回路的变化，我们对正、负偏压下的电流按其最大电压处的值进行归一化，这样通过肖特基势垒的平均电流密度随温度变化的影响能近似消除。然后，我们据此结果计算了电流回路的大小(正向和负向偏压时，不同电压扫描方向的电流差值)，结果示于图 3(a)。

随着温度的上升，电子的热激活能增大，量子点中俘获的电子更易于激发而逃逸出量子点，致使充电效应减弱，因此随着温度的上升电流回路减小。在一定温度下，电流回路的大小和形状取决于量子点的充电和放电过程。由图 3(a)可看出，归一化之后负向偏压下的回路比正向偏压下的更大(高而且宽)。与图 2 中的曲线不同，正向偏压部分看不到台阶状结构，这是因为图 2 中的台阶结构对于两个扫描方向是几乎相同的，通过作减法可以消除掉它们的影响。我们在实验中观察到当器件的  $I-V$  的特性曲线上有台阶结构时给出的电流回路较小，而没有台阶结构时给出的电流回路都较大。这表明产生电流迟滞回路和台阶结构的物理机理并不相同，迟滞回路是由量子点的充电效应引起的，而台阶结构是由于通过量子点的隧穿效应产生的。当金属栅中的费密能级与量子点能级对齐的时候，通过量子点的隧穿过程发生共振，出现电流峰值。在我们的器件里，因为背景电流的影响只能观察到台阶结构。在正向偏压下的电流回路又窄又小的事实表明，量子点的充电效应受实际的隧穿过程影响很大，当通过量子点的输运发生共振隧穿时，量子点中的电子很容易由隧穿过程逃逸，相对而言这些量子点对电子俘获限制作用减弱。所以在一定的外部偏压下有更多的量子点处于放电状态，导致较小的

电流回路。因此，当电流回路曲线中存在台阶结构时，器件的充电效应减弱，电流回路变小。

图3 (a)不同温度下的器件电流回路(对端点电流归一化后的结果)(b)为(a)图中电流回路面积随温度的变化(图中黑点),实线为按指数衰减的拟合结果

在图3(b)中我们给出了回路面积随温度变化趋势图(图中黑色方点)，面积值是由对图3(a)中曲线进行积分得到的，在图3(b)中我们给出了所有温度下测试数据的结果。图3(b)中实线是我们按指数衰减函数 $A_0 \exp(-T/T_0)$ 拟合的结果。可以看出，正向和负向偏压下的回路大小都可以按指数衰减函数给出很好的拟合。它们给出的参数 $T_0$ 相差很大，正向偏压下的回路给出的值为( $77 \pm 6$ )K，负向偏压部分给出的值为( $258 \pm 78$ )K。这是因为隧穿效应的出现等效于量子点有效限制势垒的下降，因此相应的电子热激活逃逸量子点的温度下降。这种隧穿效应在I-V特性中造成台阶结构，主要来源于共振隧穿过程，其他因素的贡献很小。

下面我们进一步讨论量子点的充放电状态和通

过量子点的隧穿效应对肖特基势垒参量的影响。理想的肖特基势垒可以由热发射模型描述，但实际的金属半导体接触与理想情况有较大的偏离，这些偏离可以由场发射、热场发射、隧穿效应以及各种串、并联电阻等因素造成，并且所有这些因素的影响可以归为肖特基势垒的理想因子 $n$ 。根据热发射模型的肖特基势垒的电流-电压方程<sup>[10]</sup>可写为如下形式：

$$\ln\left(\frac{I \exp(eV/kT)}{\exp(eV/kT) - 1}\right) = \ln(J_0 S) + \frac{e}{nkT} V, \quad (1)$$

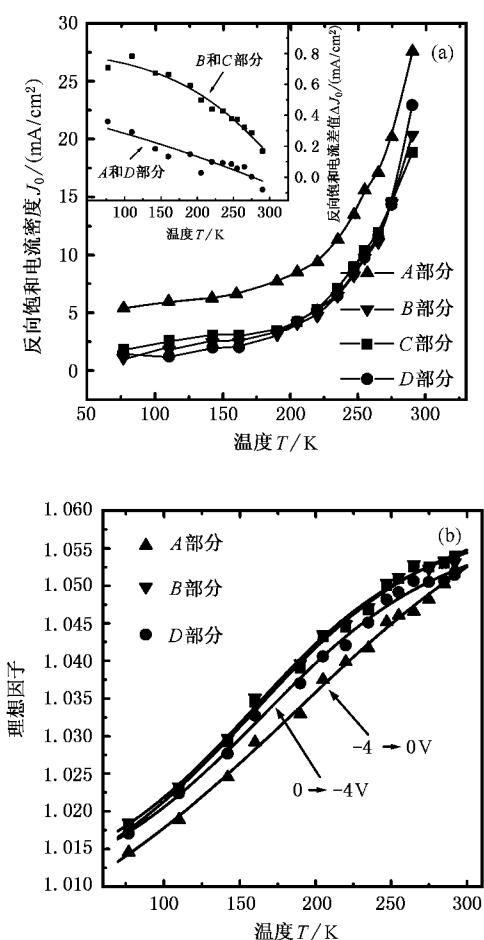

其中 $S$ 为肖特基接触的面积， $n$ 为理想因子， $J_0$ 为肖特基势垒的反向饱和电流密度。由此式可知， $\ln[I \exp(eV/kT) / (\exp(eV/kT) - 1)]$ 对 $V$ 的曲线在所有电压下都应给出一条直线，其斜率为 $e/nkT$ ，零电压对应的截距给出肖特基势垒的反向饱和电流密度 $J_0$ 。在我们的MSM二极管中，反向肖特基势垒的输运特性受到量子点两方面的影响：电子俘获效应和通过量子点能级的共振隧穿效应。根据测试数据，我们计算了 $\ln[I \exp(eV/kT) / (\exp(eV/kT) - 1)]$ 对 $V$ 的依赖关系为一条直线<sup>[11]</sup>。我们利用线性拟合进一步计算了对应的斜率和截距，给出了肖特基势垒的反向饱和电流密度 $J_0$ 和平均理想因子 $n$ 。在图4(a)和图4(b)中，我们分别给出了MSM二极管曲线A,B,C和D四部分对应的 $J_0$ 和 $n$ 随温度的变化曲线。

我们先分析图4(a)中的电流密度曲线 $J_0$ ，正向偏压下的曲线(B和C部分)对应的值较小，而负向偏压下的曲线中A部分对应的电流密度 $J_0$ 较大，D部分对应的电流小，因此它们之间的差值较大。图4(a)中插图给出了正向和负向偏压时的两个扫描方向对应的反向饱和电流之间的差值随温度的变化。随温度的上升差别逐渐减小，这种差别是因为量子点不同的充放电状态对有效肖特基势垒高度的影响不同造成的。量子点充电时，有效势垒高度较大，对应的反向饱和电流密度则较小，这是曲线B和D部分的情况。当量子点放电后，有效势垒高度下降导致饱和电流增大，对应于曲线A和C部分。曲线B与C对应的电流密度之间的差别比A与D之间的差别小，又一次说明在共振隧穿作用下量子点层对电子的俘获能力下降，从而使两个不同扫描方向时的有效势垒高度差别减小。

在图4(b)中我们给出了由反向I-V特性曲线得到的肖特基势垒的平均理想因子，在图4(b)中我们

图 4  $I$ - $V$  曲线中  $A$ ,  $B$ ,  $C$  和  $D$  四部分对应的反向饱和电流密度(a)和平均理想因子(b)随温度的变化 (a) 中插图给出了正负偏压下两个电压扫描方向时反向饱和电流的差别

可以看到, 曲线  $A$  和  $D$  部分对应的理想因子比较小, 但是它们之间的差别比较大。说明曲线  $A$  部分

对应的情况最接近于热发射模型, 这是因为没有量子点影响时的肖特基势垒最接近理想情况。因为曲线  $B$  和  $C$  部分中有较大的通过量子点的共振隧穿成分, 它们偏离理想的情况比较大, 对应的理想因子也较大。

在理想因子的结果中值得注意的一点是, 随着温度的上升理想因子增大(图 4(b))。这种现象与文献报道不同<sup>[12,13]</sup>, 文献中一般观察到金属半导体接触的理想因子随温度上升而下降的情况。我们的结果可以如下解释: 随着温度的上升 InAs 量子点及其漫润层中的能级相对于金属费密能级而言向低能方向移动<sup>[14]</sup>, 因此通过量子点的电流随温度上升增大很快, 使肖特基势垒更加偏离理想特性。由图 2 中我们可以看出, 随温度的上升共振隧穿的台阶结构向低偏压位置移动, 所以在一定偏压下隧穿效应对总电流的贡献随温度上升而增大。

## 4 结语

我们系统研究了含 InAs 自组装量子点的 SMS 二极管电流输运特性随温度的变化。我们观察到通过自组装量子点的共振隧穿效应减弱了量子点对电子的存储能力, 在  $I$ - $V$  曲线中表现为, 当曲线含有台阶结构时, 往返扫描时给出迟滞回路较小。我们通过研究量子点不同状态下的肖特基势垒的反向特性曲线给出的饱和电流和理想因子等参量, 发现通过量子点的共振隧穿过程使肖特基势垒偏离理想状况。同时量子点不同的充放电状态也引起肖特基势垒高度的变化, 从而在很大程度上影响势垒的反向饱和电流。

- [1] H. B. He *et al.*, *Acta Phys. Sin.*, **49**(2000), 1453 (in Chinese) [何红波等, 物理学报, **49**(2000), 1453].

- [2] J. Li, L. Wang, X. F. Huang *et al.*, *Chin. Phys.*, **9**(2000), 537.

- [3] X. L. Yuan *et al.*, *Acta Phys. Sin.*, **49**(2000), 2037 (in Chinese) [袁晓利等, 物理学报, **49**(2000), 2037].

- [4] Z. M. Wang *et al.*, *Acta Phys. Sin.*, **47**(1998), 89 (in Chinese) [王志明等, 物理学报, **47**(1998), 89].

- [5] Z. G. Wang *et al.*, *Chin. J. Semicond.*, **21**(2000), 827 (in Chinese) [王占国等, 半导体学报, **21**(2000), 827].

- [6] I. Tanaka, I. Kamiya, H. Sakaki, N. Qureshi, S. J. Allen, Jr., P. M. Petroff, *Appl. Phys. Lett.*, **74**(1999), 844.

- [7] K. H. Schmidt, M. Versen, U. Kunze, D. Reuter, A. D. Wieck, *Phys. Rev.*, **B62**(2000), 15879.

- [8] S. K. Jung, S. W. Hwang, B. H. Cho, S. I. Kim, J. H. Park, *Appl. Phys. Lett.*, **74**(1999), 714.

- [9] H. W. Li *et al.*, *Acta Phys. Sin.*, **50**(2001), 74 (in Chinese) [李宏伟等, 物理学报, **50**(2001), 74].

- [10] E. H. Rhoderick, *Metal-Semiconductor Contacts* (Clarendon Press, Oxford, 1978).

- [ 11 ] S. Averine , Y. C. Chan , Y. L. Lam , *Appl. Phys. Lett.* , **77** (2000) , 274.

- [ 12 ] M. Nathan , Z. Shoshani , G. Ashkinazi , B. Meyler , O. Zolotarevski , *Solid-State Electron.* , **39** (1996) , 1457.

- [ 13 ] P. G. McCafferty , A. Sellai , P. Dawson , H. Elabd , *Solid-State Electron.* , **39** (1996) , 583.

- [ 14 ] A. Polimeni , A. Patanè , M. Henini , L. Eaves , P. C. Main , *Phys. Rev.* , **B59** (1999) , 5064.

## THE INFLUENCE OF InAs QUANTUM DOTS ON THE TRANSPORT PROPERTIES OF SCHOTTKY DIODE \*

LI HONG-WEI WANG TAI-HONG

( Institute of Physics , Chinese Academy of Sciences , Beijing 100080 , China )

( Received 29 June 2001 ; revised manuscript received 4 August 2001 )

### ABSTRACT

In the temperature range from 77 to 292 K , we investigated the transport properties of metal – semiconductor-metal diode containing InAs quantum dots . With increasing temperature , the current hysteresis loops , which were caused by charged quantum dots , reduced gradually . The resonant tunneling process , which may occur in some Schottky barriers , could induce steps on the *I-V* curves in the measured temperature range and diminish the hysteresis loops intensively . We have calculated the saturation current density and ideality factor of the Schottky barrier with reverse characteristics . We found that the resonant tunneling process would shift the Schottky barrier away from the ideality status , while the charging effect mainly influenced the barrier height and therefore influenced the saturation current density .

**Keywords :** self-assembled quantum dots , Schottky diode , current-voltage characteristics

**PACC :** 6865 , 7360L , 7340S

\* Project supported by the National Natural Science Foundation of China ( Grant Nos. 69925410 and 19904015 ).