# 基于库仑阻塞原理的多值存储器 \*

孙劲鹏 王太宏

(中国科学院物理研究所 北京 100080)

(2002 年 12 月 10 日收到 2003 年 1 月 23 日收到修改稿)

设计了一种基于库仑阻塞原理的新型单电子多值存储器。器件包括两个多隧穿结构和一个单电子晶体管，其中单电子晶体管起到一个静电计的作用来实现数据的读取。两个隧穿结库仑阻塞区域的大小不同使得器件具有三个稳定的存储状态。利用这个原理可以制备出多值的动态随机存储器和非挥发性的随机存储器。这种低功耗的单电子多值存储器可以实现信息的超高密度存储。

关键词：库仑阻塞，单电子晶体管

PACC : 7335C, 7335

## 1. 引言

电子器件经历了从电子管到晶体管，从分立器件到集成电路的发展过程。为了满足迅速发展的信息和计算机技术的需要，集成电路的线宽不断减小，集成度不断提高。高密度、高速度、低功耗是集成电路技术追求的几个主要指标。目前工业化大规模生产的集成电路线宽已经减小到了  $0.13\mu\text{m}$ ，而实验室已可实现  $10\text{nm}$  以内的线宽。减小线宽可以成比例的提高集成电路的密集度，但当器件某一维或多维尺寸减小到纳米量级，以至于特征尺寸小于由外界温度所决定的非弹性散射自由程时，量子效应将十分明显。这将导致宏观概念的失效。因此基于传统宏观概念的器件将不能正常工作。存储器件的发展同样面对着器件进一步减小所带来的困难。以动态存储器(DRAM)的发展为例，存储单元中的电容不能太小，如果这个电容小到不能提供足够多的电子给放大器，那么整个存储器将被噪声所淹没，将不能保证信息存储的可靠性；同时，每个存储单元的电子数目随着存储器件集成度的进一步提高变得越来越小时，存储器中的 MOS 场效应晶体管将会逐渐变得不稳定。

由此可见，不能仅仅依赖工艺的微细化来解决传统产业所面临的问题，所以在一个存储单元中存

入多个比特的多值存储技术将显得越来越重要。因为传统的 CMOS 只有两个状态：开和关，所以基于 CMOS 的传统存储器单元进行多值存储时受到多方面限制。考虑到未来新型计算机的发展将以分子电子学、量子力学和生物技术为基础，所以多值存储器无疑是一种具有广阔发展前景的存储器件。

单电子器件具有不同于传统器件的电学性质，它可以通过精确控制量子点中电荷的数目来实现器件的一定功能。据此研究制备出了具有两个稳定状态的单电子存储器<sup>[1-5]</sup>；同时人们也开始对单电子的多值存储器件进行研究<sup>[6,7]</sup>，希望最大程度的发挥单电子存储器的潜能。本文将要讨论的单电子多值存储器具有三个稳定的存储状态，这些状态可以通过对极少数电子的控制来实现。这种单电子三值存储器体现了单电子器件和多值存储器件的共同特点：低功耗及低散热量和高存储密度。

## 2. 器件的基本结构

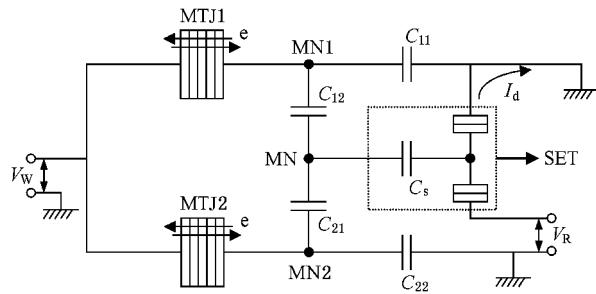

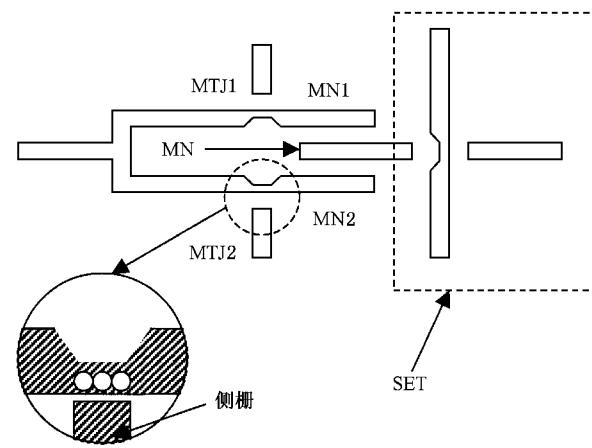

器件的基本结构如图 1 所示。器件包括 MTJ1 和 MTJ2 两个多隧穿结构，两个隧穿结可以控制与之相连的存储点中的电位，即可以在 MN1 和 MN2 中存储一定数目的电子。图 1 中 MN 尽管不存在额外的电子，但是仍然可以看作是整个存储器件的存储点，它与 MN1 和 MN2 通过电容耦合在一起；一个单

\* 国家重点基础研究专项经费(批准号 G2001CB3095)和国家自然科学基金(批准号 69925410 和 60236010)资助的课题。

电子晶体管(SET)同样以电容耦合的方式与MN相连,作为一个静电计,它可以用来探测MN中的电位来实现数据的读取。MTJ1和MTJ2的一端连接在一起通过写电压 $V_W$ 来控制器件数据的写入。单电子器体管的源极接地,在漏极施加写电压 $V_R$ ,通过源漏之间电流 $I_d$ 的特征来判断MN中电位的高低,这样就可以实现数据的读取。

图1 存储单元的结构示意图

### 3. 多隧穿结(MTJ)结构

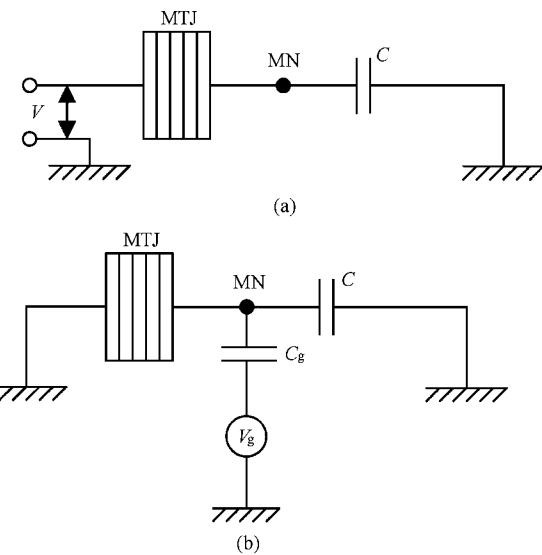

多隧穿结(MTJ)结构是本器件的重要组成部分之一。它的基本结构包括一串纳米量级的库仑岛,这些库仑岛通过隧穿势垒分开。制备的材料主要包括金属和半导体材料。库仑岛的充电能使MTJ存在一个库仑阻塞区域,基于这种性质就可以利用多隧穿结结构实现多种单电子存储器件的制备<sup>[8,9]</sup>。图2显示了MTJ的两种基本的工作方式,一种通过控制多隧穿结一侧的电压使另一侧的存储点在库仑阻塞区域的边缘达到两个稳定的存储状态,其工作方式可以利用图2(a)来描述;另一种则直接通过控制存储点的静电化学势能来达到改变存储点MN中电子数目的目的<sup>[8,9]</sup>。其工作方式可以用图2(b)来描述。在我们设计的存储器件中选取了前一种的工作方式。

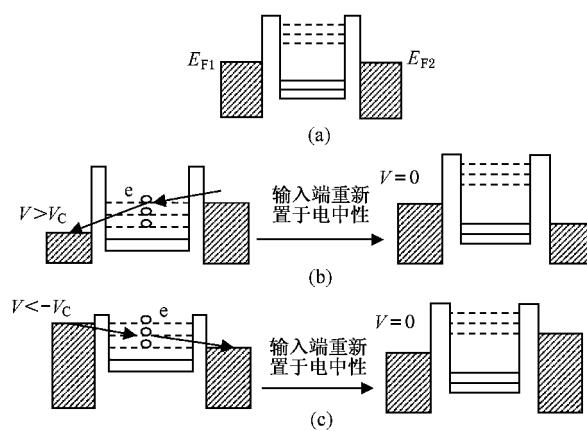

现在讨论本器件中MTJ的基本工作原理。假定MTJ存在一个大小为 $2V_c$ 的库仑阻塞区域,增大电压使得电压输入端电子的费米能级超出库仑阻塞区域时,电子将会通过MTJ在电压输入端和存储点MN之间进行交换,存储点中电子数目的变化引起其费米能级的变化,电子交换的结果是在输入端电压 $V=0$ 时存储点处在 $+V_c$ 或 $-V_c$ 这两个稳定的存储状态。假设在 $V=0$ 时输入端电子的费米能级、存储点MN的费米能级如图3(a)所示,MN初始电位为0。当输入端电压 $V>V_c$ 时,电子将会由存储点

图2 MTJ的两种基本工作方式

MN通过MTJ进入电压的输入端,假定电压的输入端电容足够大,有限电子的变化不会引起电压输入端费米能级的改变;而存储点MN的费米能级会因为电子数目的减少而降低,每减少一个电子,费米能级降低 $e^2/C_\Sigma$ ,其中 $C_\Sigma$ 为MN的总电容,对应的存储点的电压升高 $e/C_\Sigma$ ,最终将会引起存储点MN中N个电子的逃离,此时MN的电位为 $Ne/C_\Sigma$ ,根据MTJ库仑阻塞区域的大小可以得到 $\frac{Ne}{C_\Sigma} = V_c$ ,所以通过MTJ对MN的这个存储过程需要的电子数目N为 $N = \frac{V_c C_\Sigma}{e}$ 。为了最大限度提升器件的存储性能,通常希望N的值越小越好,理想状态下 $N = 1$ ,即MTJ库仑阻塞区域的大小和MN的总电容满足关系 $V_c C_\Sigma = e$ ,因此满足此条件的存储系统只需要控制一个电子的移动就可以实现数据的存储,图3(b)演示了MN达到电位 $V_c$ 这个稳定存储状态的存储原理。同理,可以知道输入端电压 $V < -V_c$ 时,存储点中进入 $N = \frac{V_c C_\Sigma}{e}$ 个电子,MN处在电位为 $-V_c$ 的状态,此过程用图3(c)来描述。

### 4. 静电计

在这种具有三个稳定存储状态的单电子存储器件中,存储点以电容耦合的方式连接了一个SET,此处的单电子晶体管作为静电计,可以探测某区域的

图3 (a)在电压  $V=0$ ,存储点 MN 处在电中性时,电压输入端的费米能级 MTJ 的静电化学势和 MN 的费米能级之间的关系 (b) 在电压  $V>V_c$  时,电压输入端的费米能级 MTJ 的静电化学势和 MN 的费米能级之间的关系,电子通过 MTJ 逃离存储点 MN,当电压  $V=0$  时存储点 MN 最终处在  $V_c$  状态 (c) 在电压  $V<-V_c$  时,电压输入端的费米能级 MTJ 的静电化学势和 MN 的费米能级之间的关系,电子通过 MTJ 进入存储点 MN,当电压  $V=0$  时存储点 MN 最终处在  $-V_c$  状态 ( $E_{F1}$  为电压输入端的费米能级, $E_{F2}$  为 MN 的费米能级,同时假定器件工作时 MTJ 有三个能级可以用来导通电子)

电位高低,以此来实现数据的读取<sup>[10]</sup>. 单电子晶体管的基本结构包括库仑岛、源极、漏极和栅极,其中库仑岛与源漏极极弱耦合在一起,控制栅极电压可以改变库仑岛的静电化学势. 当施加在源漏极上的偏压很小时,源漏之间的电流随栅极电压的变化进行库仑振荡,利用库仑振荡曲线可以判断存储点电位的变化,这是 SET 实现静电计功能的一种工作方式,工作在此区间的 SET 可以实现高精度的电荷探测. 单电子晶体管的另一种工作方式是将源漏极之间的电压设得足够大,此时源漏极之间的电流随栅极电压的变化在一定范围内近似呈现线性关系,此时同样可以根据漏极电流的大小来判断待测区域的电位高低,实现数据的读取. 在我们设计的这种单电子多值存储器中静电计的两种工作方式都可以实现数据的读取,考虑到工作时存储点处电压的变化情况,采用 SET 的后一种工作方式,即将源漏极置于大偏压的状态.

图1所示单电子晶体管具有双隧穿结的结构,即存在单个库仑岛这样的结构通常可以做得很小,因此器件可以实现更高的存储密度,但是它比较容易受电荷补偿效应(*offset charge effects*)的影响,容易导致单电子晶体管中库仑阻塞区域的大小发生改变,甚至消失. 使用 MTJ 结构的单电子晶体管可以

解决这个问题. 器件通常包含高掺杂的硅纳米线或者是  $\delta$  掺杂的 GaAs 纳米线,利用侧栅电压的耗尽作用在纳米线中实现多隧穿结结构,同时利用另一个栅极来控制纳米线中库仑岛的静电化学势能,并将其栅极和待测的区域以电容耦合的方式连接在一起,就可以实现数据的读出功能. 器件的工作原理与具有两个隧穿结的静电计工作原理类似. 基于这种结构制备的存储器集成度受纳米线栅极尺寸的限制,因此器件的存储密度通常会受到影响.

## 5. 器件存储原理

假定多隧穿结 MTJ1 的库仑阻塞区域为  $(-V_{Cl}, V_{Cl})$ , MTJ2 的库仑阻塞区域为  $(-V_{C2}, V_{C2})$ . 由上文讨论可知存储点 MN1 可以处在两个稳定的存储状态,电位为  $-V_{Cl}$  和  $V_{Cl}$ , MN1 中得到或者失去电子的数目即额外电子数目  $\Delta N_1$  为

$$\Delta N_1 = \frac{\Delta Q_1}{e} = \frac{C_{\Sigma 1} V_{Cl}}{e}, \quad (1)$$

其中  $C_{\Sigma 1}$  为 MN1 的总电容,  $C_{\Sigma 1} = C_{11} + C_{12} + C_{m1}$ ,  $C_{m1}$  为 MTJ1 的总电容.

MN2 两个稳定状态的电位为  $-V_{C2}$  和  $V_{C2}$ , 对应的得到或者失去的电子数目  $\Delta N_2$  为

$$\Delta N_2 = \frac{\Delta Q_2}{e} = \frac{C_{\Sigma 2} V_{C2}}{e}, \quad (2)$$

其中  $C_{\Sigma 2} = C_{21} + C_{22} + C_{m2}$  为 MN2 的总电容,  $C_{m2}$  为 MTJ2 的总电容.

器件中存储点 MN 的电位  $V^{MN}$  有可能具有四个不同的值分别为

$$\begin{aligned} V_1^{MN} &= \frac{C_{12} V_{Cl} + C_{21} V_{C2}}{C_{12} + C_{21} + C_s} \\ &= \frac{C_{12}}{C_{12} + C_{21} + C_s} V_{Cl} + \frac{C_{21}}{C_{12} + C_{21} + C_s} V_{C2} \\ &= \alpha \cdot V_{Cl} + \beta \cdot V_{C2}, \end{aligned}$$

其中  $\alpha = C_{12}/C_{MN}$ ,  $\beta = C_{21}/C_{MN}$ ,  $C_{MN} = C_{12} + C_{21} + C_s$  为 MN 处的总电容. 同理, 可以推出

$$V_2^{MN} = \frac{C_{12} V_{Cl} - C_{21} V_{C2}}{C_{12} + C_{21} + C_s} = \alpha \cdot V_{Cl} - \beta \cdot V_{C2},$$

$$V_3^{MN} = \frac{-C_{12} V_{Cl} + C_{21} V_{C2}}{C_{12} + C_{21} + C_s} = -\alpha \cdot V_{Cl} + \beta \cdot V_{C2},$$

$$V_4^{MN} = \frac{-C_{12} V_{Cl} - C_{21} V_{C2}}{C_{12} + C_{21} + C_s} = -\alpha \cdot V_{Cl} - \beta \cdot V_{C2}.$$

同时,还可以很容易判断出 MN1 和 MN2 在不同的稳定状态下, MN 所具有的电位值之间的关系为

$$V_1^{MN} > V_2^{MN} (V_3^{MN}) > V_4^{MN},$$

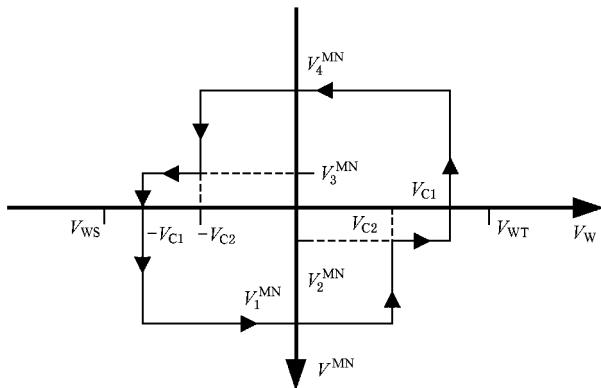

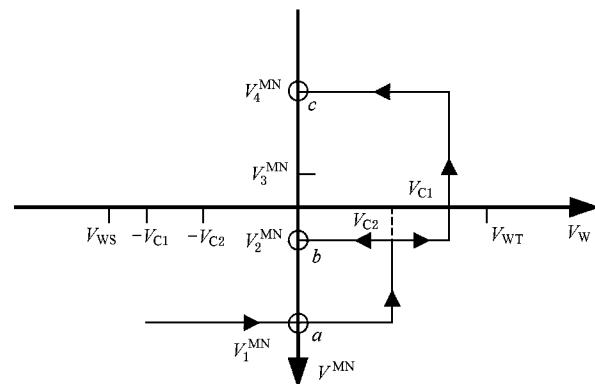

其中  $V_2^{MN}$  和  $V_3^{MN}$  的大小关系需要利用更多器件的参数才能确定出来(两者有可能都为 0),在我们设计的存储器件中将这两个状态选择一个作为器件的一个稳定的存储状态.由此可见,通过控制写电  $V_W$  的大小就可以在器件中实现三个稳定的存储状态,分别对应 MN 处的电位为  $V_1^{MN}$ , $V_2^{MN}$ ( $V_3^{MN}$ )和  $V_4^{MN}$ .器件存储点 MN 中的电位可以通过写电压的扫描来改变.假定  $V_{Cl} > V_{C2}$ , $V_2^{MN} > 0 > V_3^{MN}$ ,电压  $V_W$  先由  $V_{WS}$  到  $V_{WT}$  正向扫描,再由  $V_{WT}$  到  $V_{WS}$  反向扫描,其中  $V_{WS}$  略小于  $-V_{Cl}$ , $V_{WT}$  略大于  $V_{Cl}$ ,MN 的电位  $V^{MN}$  随  $V_W$  的变化情况由图 4 给出.图中没有描述在区间( $V_{WS}$ , $-V_{Cl}$ )和( $V_{Cl}$ , $V_{WT}$ )的 MN 处电位  $V^{MN}$  的变化过程,这是因为这两个过程中 MN 处的电位大小与器件的存储历史等若干因素有关,是一个复杂的动态过程,但这两个区间的不稳定性并不会影响到器件三个稳定存储状态的获得.

图 4  $V_W$  先由  $V_{WS}$  正向扫描到  $V_{WT}$ ,再进行反向扫描,此过程 MN 中电位的变化情况

根据图 4,将器件存储点 MN 电位为  $V_1^{MN}$ , $V_2^{MN}$  和  $V_4^{MN}$  对应的系统状态  $a$ , $b$  和  $c$  作为三个稳定的存储状态,这样就形成了三值的存储器.利用写电压的扫描实现了不同数值的写入,其写入过程如图 5 所示,此时同样忽略了电压处在区间( $V_{WS}$ , $-V_{Cl}$ )和( $V_{Cl}$ , $V_{WT}$ )时存储点 MN 电位的变化过程, $V_W$  由  $V_{WS}$  开始正向扫描到 0 电压时,写入状态  $a$ ,对应的电压为  $V_1^{MN}$ ;正向扫描到  $V_{Cl}$ (实际的电压应略大于此值但小于  $V_{Cl}$ )然后反向扫描到 0 电压,写入状态  $b$ ,对应 MN 的电位为  $V_2^{MN}$ ;正向扫描电压到  $V_{Cl}$ (实际的电压应略大于此值)然后反向扫描到 0 电压,写入状态  $c$ ,对应 MN 的电位为  $V_4^{MN}$ .若想读出器件所存储

的信息,则需要在器件静电计上的源漏极之间施加偏压,不同的  $V^{MN}$  可以通过漏极处不同大小的电流反应出来,这样就利用静电计实现了数据的存储.

图 5 存储器通过写电压的扫描实现  $a$ , $b$  和  $c$  三个稳定存储状态的过程

器件在三个状态下,存储点 MN 中电压差异越明显,并且产生这些差异所需要的电子数越小,器件的存储性能就越好,比如功耗低、散热量小和较高的工作频率等.假设本存储器件中存储点 MN1 和 MN2 状态的改变只需要一个电子,即  $\Delta N_1 = \Delta N_2 = 1$ ,由方程(1)和(2)可以得到其所应该满足的条件是

$$V_{Cl} = \frac{e}{C_{\Sigma 1}},$$

$$V_{C2} = \frac{e}{C_{\Sigma 2}}.$$

由此可见,通过控制存储器件中各个电容的大小和 MTJ 库仑阻塞区域的大小可以改变工作所需要的电子数目,电路中两个电子的运动就可以实现三个稳定的存储状态.

详细研究两个多隧穿结的库仑阻塞区域哪个更大对于器件来说是没有必要的,讨论 MN 的电位  $V_2^{MN}$  和  $V_3^{MN}$  谁为正值谁为负值同样是不必要的,尽管在前面的讨论中规定了它们的大小关系.对于一个确定的存储器件,所要关注的是器件中两个多隧穿结库仑阻塞区域的大小和它们之间的关系.如果两个多隧穿结的库仑阻塞区域大小相同,即  $V_{Cl} = V_{C2}$ ,那么器件就只能有两个稳定的存储状态,根本无法实现器件多值存储的目的.由此可见器件工作有两个必要条件:

1)  $V_{Cl}$  和  $V_{C2}$  的区别要足够的明显.判断的依据是在数据的写入过程中电压源能够通过扫描准确达到不同的存储状态,如果两个区域的差太小以至于

超出了写入电压源所能提供的电压精度,那么根本就无法实现三个稳定状态的写入,数据的存储也就无从谈起了。事实上,如果不考虑对电压源的精度要求,两个多隧穿结的库仑阻塞区域相同大的情形只存在概率上的可能。就现在的工艺水平来看,无论两个隧穿结做得如何相似都不可能是完全相同的。为了降低对写电压控制的难度,即更利于数据的写入,我们可以在多隧穿结的制备过程或工作过程中增大 $|V_{C1} - V_{C2}|$ 的值,这样的目的可以通过改变多隧穿结中量子点的位置和大小来实现。当然,这个控制的过程并不一定需要精确控制MTJ中每一个量子点的位置和大小,只要改变它们的总电容即可。

2)三个稳定状态对应的MN的不同电位可以通过静电计判断出来,即可以实现数据的读取。就目前的单电子器件在探测方面的应用来看,达到这个条件并不苛刻。此外控制器件工作所需要的电子数可以通过调整 $C_{11}, C_{12}, C_{21}, C_{22}$ 和MTJ中总电容的大小来实现。

## 6. 单电子三值动态随机存储器和非挥发性随机存储器

这种结构的单电子三值存储器件的性能很大程度上受限于两个多隧穿结MTJ1和MTJ2的性质,通过制备出不同种类的MTJ就可以实现具有不同存储特点的单电子多值存储器件,可以满足不同的存储要求。下面是利用以上原理设计的两种不同类型的单电子多值存储器。

图6是一个单电子三值动态随机存储器(DRAM)的平面结构示意图,其MTJ的结构可以通过侧栅耗尽 $\delta$ 掺杂的GaAs纳米线来制备。用作数据读出的单电子晶体管同样采用了多隧穿结结构,器件中每个MTJ的电容可以通过侧栅的耗尽电压来改变,因此每个MTJ库仑阻塞区域的大小可以通过侧栅的耗尽电压来改变,原则上电容越小库仑阻塞区域越大,存储的两个稳定状态越明显,但这只能在一定的范围内成立,因为耗尽的偏压太大可能会使纳米线根本无法导通。器件的工作频率与MTJ的 $R_t \cdot C_m$ 的值成反比,其中 $R_t$ 为MTJ的电阻, $C_m$ 为MTJ的总电容。因此如果提高多隧穿结的制备水平是提高器件存储性能的关键性问题。此外,这种多值的DRAM同样可以利用高掺杂的硅纳米线来实现。

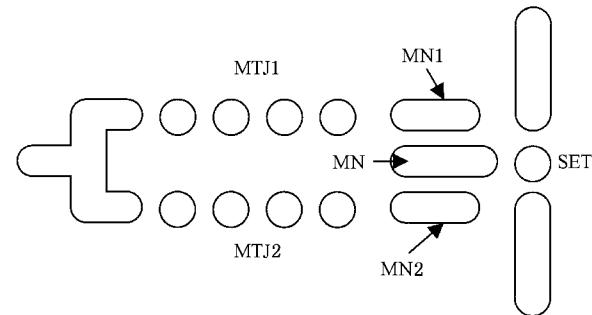

图7是根据以上原理设计的单电子三值非挥发性随机存储器(NOVORAM)的平面结构示意图。我们

图6 单电子三值动态随机存储器的平面结构示意图(圆形插图是侧栅耗尽纳米线形成多隧穿结结构的示意图)

可以采用电子束直写工艺(electron-beam direct writing technique)在绝缘体上的硅(SOI)中制备出多隧穿结结构,每一个MTJ的几何形状是一串被隧穿势垒分割的纳米量级的库仑岛。此器件的单电子晶体管可以采用图7所示的双隧穿结结构,也可以采用类似图6的多隧穿结的结构。这种多值的NOVORAM可以获得更高的存储密度,同时采用SOI还考虑到了与传统半导体工艺的兼容性问题。因为此类型器件中的多隧穿结每个库仑岛的大小和位置是可控的,所以具有很强的可重复性,但是制备的工艺复杂。

图7 单电子三值非挥发性随机存储器的平面结构示意图

## 7. 结 论

总之,我们设计了一种具有三个稳定存储状态的单电子存储器,利用了多隧穿结结构的库仑阻塞效应,同时利用静电计来实现数据的读取。通过改变MTJ的库仑阻塞区域和器件中电容的大小,三个稳定的存储状态之间的变化有可能通过控制极少数的

电子运动就可以实现。利用此原理，采用不同类型的 MTJ 可以实现不同种类的存储器，例如单电子三值动态存储器和单电子三值非挥发性随机存储器。利用平面结构的单电子晶体管(SET)可以实现完全平面结构的单电子存储器。如果利用 SOI 制备这种平面结构的单电子存储器，采用电子束直写工艺制备 MTJ，有可能形成超小的量子点和隧穿势垒，这样制

备的 MTJ 可以控制其中每个量子点的大小和位置，制备出来的器件具有很高的可重复性。

我们设计的这种存储器同时具备了单电子存储器和多值存储器的优点，并充分考虑和传统半导体工艺的兼容性问题，制备出的低功耗的单电子三值存储器有希望实现信息的超高密度存储。

- [1] Dutta A *et al* 1999 *Appl. Phys. Lett.* **75** 1422

- [2] Stone N J *et al* 1998 *Appl. Phys. Lett.* **73** 2134

- [3] Kim J *et al* 2000 *Jpn. J. Appl. Phys. Part 1* **39** 4826

- [4] Zahid A K *et al* 1999 *Appl. Phys. Lett.* **74** 1293

- [5] Tiwari S *et al* 1996 *Appl. Phys. Lett.* **68** 1377

- [6] Yamamura K *et al* 1998 *Jpn. J. Appl. Phys. Part 2* **37** L1440

- [7] Inokawa H *et al* 2001 *Appl. Phys. Lett.* **79** 3618

- [8] Nakazato K *et al* 1995 *Jpn. J. Appl. Phys. Part 1* **34** 700

- [9] Mizuta H *et al* 2001 *Nanotechnology* **12** 155

- [10] Nakazato K *et al* 1994 *J. Appl. Phys.* **75** 5123

## Coulomb blockade three-valued single-electron memory<sup>\*</sup>

Sun Jin-Peng Wang Tai-Hong

( Institute of Physics, Chinese Academy of Sciences, Beijing 100080, China )

( Received 10 December 2002 ; revised manuscript received 23 January 2003 )

### Abstract

We have designed a novel three-valued single-electron memory. This memory comprises two multiple-tunnel junctions (MTJs) and a single-electron transistor which acts as an electrometer. Because the Coulomb gaps of the two multiple-tunnel junctions are different, the device has three stable states. It is possible to fabricate multiple-valued single-electron dynamic random access memories (DRAM) and nonvolatile random access memories (NOVORAM). The memory, which is promising for high frequency and low power-dissipation, can achieve ultradense data storage.

**Keywords** : Coulomb blockade, single-electron transistors

**PACC** : 7335C, 7335

\* Project supported by the Special Foundation for State Major Basic Research Program of China (Grant No. G2001CB3095) and by the National Natural Science Foundation of China (Grant Nos. 69925410 and 60236010).