# 基于模拟电路的新型忆感器等效模型\*

梁燕 于东升<sup>†</sup> 陈昊

(中国矿业大学, 信息与电气工程学院, 徐州 221116)

(2013年3月6日收到; 2013年4月11日收到修改稿)

本文首先利用光敏电阻阻值的可控性, 建立了磁通控制型忆阻器的等效电路模型。通过对忆感器和忆阻器间转换关系的分析, 采用模拟电子元器件设计了磁通控制型忆感器的实用等效电路模型, 给出了理论分析并结合 Pspice 软件进行了仿真验证。忆感器等效电路模型的韦安关系展现出典型的非线性磁滞回线特性。最后, 运用实验手段研究了正弦波和三角波两种典型电压信号激励下忆感器与  $RC$  串联后电路的动态特征, 证明了本文提出忆感器等效电路模型的有效性。

**关键词:** 忆阻器, 忆感器, 磁滞回线特性, Pspice

**PACS:** 85.25.Hv, 07.50.Ek

**DOI:** 10.7498/aps.62.158501

## 1 引言

蔡少棠在 1971 年发表论文推测, 存在衔接电荷和磁通关系的第四种基本电路元件——忆阻器<sup>[1,2]</sup>, 但当时并没有引起足够的研究兴趣。直到 2008 年 5 月, 惠普实验室宣布利用  $TiO_x$  成功合成了具有忆阻器特性的纳米级固态元件<sup>[3]</sup>, 忆阻器的相关研究迅速引起研究者们的重视<sup>[4–6]</sup>。作为一种具有记忆能力的非线性阻性元件, 忆阻器的信息记忆能力使其在非易失存储器、振荡电路等研究领域展现出巨大的应用潜力<sup>[7–9]</sup>。2009 年, 文献[10]进一步提出忆感器和忆容器的概念。因其具有独特的记忆和动态能量存储能力, 有理由相信忆感器和忆容器在电子电路领域将展现更为诱人的应用前景。

因忆阻器元件尚不可购, 建立等效电路并对其动态特性进行深入研究是十分必要的。目前, 已完成了许多有关忆阻器仿真模型<sup>[11–13]</sup> 和等效电路模型<sup>[14–17]</sup> 的研究工作。如文献[14]设计了一种可以模拟  $TiO_2$  型忆阻器的等效电路, 并研究了多忆阻器串联、并联和混联电路的结构及动态特征。文献[15]采用模拟电路与数字电路相结合的方法构

建了忆阻器的等效电路模型, 可通过编写数字芯片内部代码实现对忆阻值的修改。但由于模拟信号与数字信号之间需要进行转换处理, 从而使模型的应用具有一定的局限性。目前对于忆感器的研究仍只停留在理论与仿真层面上, 尚没有可行的物理合成方案。文献[18]在 Pspice 仿真环境下利用受控源与编程模块实现对忆感器的仿真模拟。文献[19]虽提出了一种简单易实现的忆感器和忆容器的等效电路, 但其带有附加电阻且只进行了仿真验证, 在实验研究中仍具有很大的局限性。上述研究虽然提出了忆感器的仿真模型, 但可用于实验研究的忆感器等效电路模型尚未见报道。

本文借助于光耦电阻 XINLD-65 的阻值可控性建立了磁通控制型忆阻器的等效电路模型。在此基础上, 通过分析忆阻器与忆感器之间变量的转换关系, 设计了一种新的易于电路实现且无附加串联电阻的忆感器实用等效电路模型, 并进行了相关理论分析和实验验证。

## 2 磁通控制型忆阻器等效电路模型

电路理论中的四个基本变量(电流  $i$ , 电压  $v$ , 电荷  $q$  和磁通  $\varphi$ ) 经过两两组合可产生六种电路关系。

\* 中央高校基本科研业务费专项资金(批准号: 2013QNB28)资助的课题。

† 通讯作者. E-mail: dongsiee@163.com

其中  $v$  和  $i$ ,  $q$  和  $u$ ,  $\varphi$  和  $i$  的组合关系分别用来描述电阻、电容和电感, 即

$$R: dv = Rdi, C: dq = Cd\varphi, L: d\varphi = Ldi. \quad (1)$$

另外两个关系是法拉第定律和电流的定义,

$$\varphi(t) = \int_{-\infty}^t v(\tau) d\tau, q(t) = \int_{-\infty}^t i(\tau) d\tau. \quad (2)$$

1971 年, 蔡少棠根据缺失的  $q$  和  $\varphi$  的组合关系  $f(\varphi, q) = 0$  推测出第四种电路元件, 并将其命名为忆阻器。如果将这个关系式表达成关于磁通  $\varphi$  的单值函数, 那它描述的就是磁通控制型忆阻器, 可以表示为

$$W(\varphi) = \frac{dq(\varphi)}{d\varphi}. \quad (3)$$

其中,  $W(\varphi)$  称为忆电导。结合 (1) 式, (3) 式可进一步等效为

$$i(t) = W(\varphi)v(t). \quad (4)$$

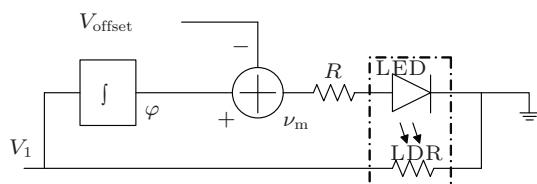

(3) 式和 (4) 式表明, 磁通控制型忆阻器的等效电路模型可以通过一个阻值变化的电阻进行设计, 只要保证其阻值随着电压的积分变化而变化, 且仅与积分大小有关, 与电压波形无关。借助于文献 [17] 提出的忆阻器等效电路建模方法, 图 1 绘制了基于光耦电阻设计的忆阻器的等效电路模型。

图 1 忆阻器等效电路模型示意图

图 1 所示模型包含两部分: 控制电路和可控电阻。控制电路由一个积分器、一个加法器组成。可控电阻采用发光二极管 (LED) 和光敏电阻 (LDR) 耦合而成的 XINLD-65 型光耦。此方法的一大优点是将控制信号与可控电阻隔离, 可以根据需要调节控制端电压进而改变光敏电阻的电导值, 具有较好的灵活性和可操作性。

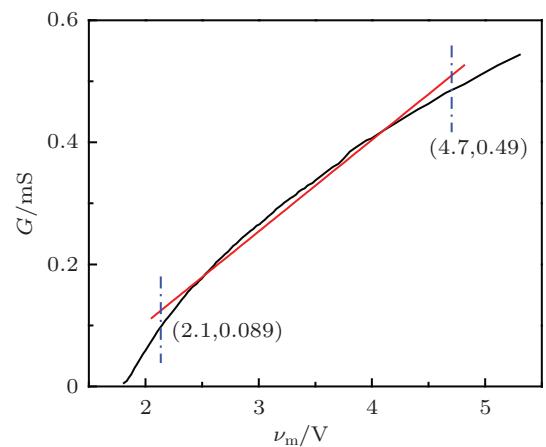

提高模型精度的关键是充分利用光耦电阻的线性变阻区。光耦电阻的电导值  $G$  随耦合 LED 发光强度的增大而增加, 而发光强度又和流过 LED 的电流呈良好的线性正比关系。通过测量光耦电阻值可得到电导值  $G$  随控制电压或电流的变化曲线。为了便于测量流过控制端 LED 的电流, 在电路设计中将一个  $1.5 \text{ k}\Omega$  的电阻  $R$  与 LED 串联, 此电

阻同时起到限流保护作用, 可将  $R$  看作是 LED 内阻的一部分。因是串联关系, 流过  $R$  的电流与流过 LED 的电流相等。因此有必要分析光耦电阻值随  $R$  与 LED 端电压之和的变化关系。在不同大小的端电压激励条件下对 XINLD-65 进行测试, 得到其输出阻值随端电压的变化曲线, 如图 2 中黑色曲线所示。其中, 横坐标  $v_m$  代表电阻  $R$  和 LED 的端电压之和, 纵坐标  $G$  表示光耦电阻的电导值。

图 2 XINLD-65 的可控电导特性

从图 2 黑色曲线可以看出, XINLD-65 的控制端电压和输出电导之间不是精确的线性关系。为了提高控制精度, 控制端电压被限定在蓝色点划线所截取的曲率变化较小的区间内, 即  $2.1 \text{ V}—4.7 \text{ V}$ 。在限定区间内对实验曲线进行拟合, 拟合结果如图中红色直线所示。数值计算表明电导测量值与拟合值之差在  $(-0.03, 0.03)\text{mS}$  范围内, 即红色直线与实测曲线具有很高的拟合度。因此, 在限定区间内可认为电导与控制电压呈线性正比关系。限定区间内对应的电导变化范围为  $0.089 \text{ mS}—0.49 \text{ mS}$ 。拟合所得的电导与控制电压关系式为

$$G = a \cdot v_m + b. \quad (5)$$

其中,  $a = 0.15$ ,  $b = -0.196$ 。

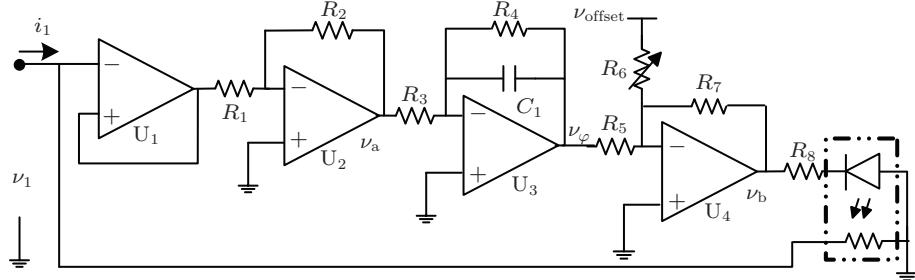

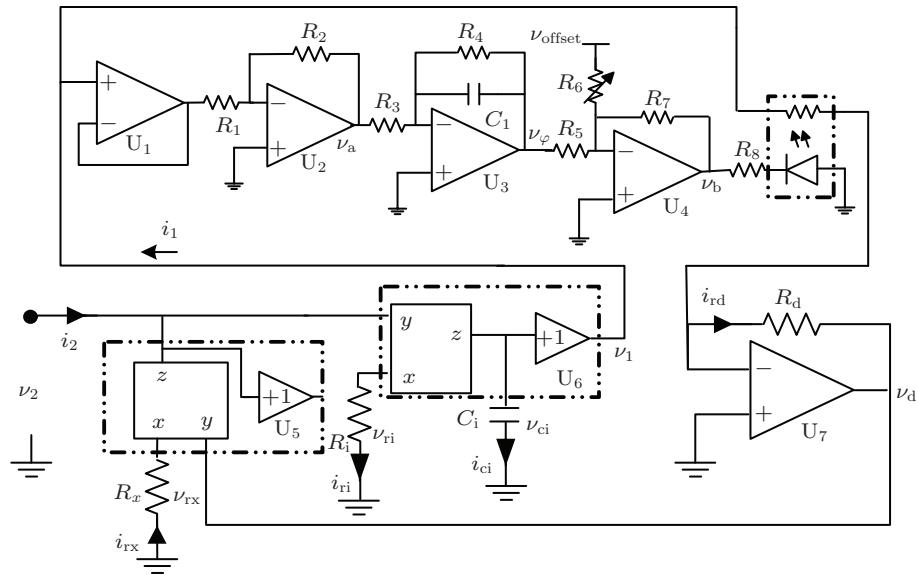

基于光耦 XINLD-65 的输入输出特性, 本文首先利用运算放大器 TL084、电阻、电容等常用元器件搭建了忆阻器的等效电路模型。模型主要包括电压跟随器、反相比例运算电路、积分运算电路、反相求和运算电路四部分, 如图 3 所示。

图 3 中采用的四个运算放大器分别标记为  $U_1$ ,  $U_2$ ,  $U_3$ ,  $U_4$ 。由  $U_1$  构成电压跟随器, 实现电压跟随的同时阻止电流流入控制电路。 $U_2$  构成反相比例

运算电路, 通过改变  $R_2$  或  $R_1$  的阻值可调节输出电压  $v_a$  的大小.  $U_3$  与  $R_3$  和  $C_1$  构成积分运算电路, 根据法拉第定律可知磁通为电压的积分, 因此  $U_3$  的输出端电压  $v_\varphi$  正比于忆阻器磁通  $\varphi_1$ . 电阻  $R_4$  的作用是通过反馈抑制直流偏置电压.  $U_4$  组成的反相求和运算电路中, 可以通过调节电位器  $R_6$  来改变输出电压  $v_b$  的大小, 以保证 XINLD-65 控制端电压处于划定的线性区域内.

图 3 忆阻器等效电路模型

假设运算放大器均为理想器件, 则流入同相输入端和反相输入端的电流为零, 且同相输入端与反相输入端的电压相等. 可以得到以下关系式

$$\begin{aligned} v_a &= -\frac{R_2}{R_1} \cdot v_1, \\ v_\varphi &= -\frac{1}{R_3 C_1} \cdot \int_{t_0}^t v_a d\tau = \frac{R_2}{R_1 R_3 C_1} \cdot \varphi_1, \\ v_b &= -R_7 \left( \frac{1}{R_5} v_\varphi + \frac{1}{R_6} v_{\text{offset}} \right), \end{aligned} \quad (6)$$

其中,  $v_1$  是忆阻器的端电压,  $v_b$  是反相求和运算放大器的输出电压. 求解方程组 (6) 可得光耦电阻的控制端电压

$$v_b = -\frac{R_2 R_7 \varphi_1}{R_1 R_5 R_3 C_1} - \frac{R_7}{R_6} v_{\text{offset}}. \quad (7)$$

将 (7) 式代入 (5) 式, 得到忆阻器的忆导值

$$\begin{aligned} W_M &= a \cdot (0 - v_b) + b \\ &= a \cdot \left( \frac{R_2 R_7 \varphi_1}{R_1 R_5 R_3 C_1} + \frac{R_7}{R_6} v_{\text{offset}} \right) + b. \end{aligned} \quad (8)$$

### 3 磁通控制型忆感器等效电路模型

已有文献表明, 可利用运算放大器、电阻、电容等元器件实现具有传统电感特性的等效电路模型 [20]. 建立忆感器等效电路模型的关键是设计一个转换电路, 实现忆阻器向忆感器的过渡. 忆感器可分为电流控制型和磁通控制型. 其中, 磁通控制型忆感器可以表示为 [10]

$$I(t) = L_M^{-1} \left[ \int_{-\infty}^t \varphi(\tau) d\tau \right] \cdot \varphi(t). \quad (9)$$

其中,  $I(t)$  为  $t$  时刻流过忆感器的电流,  $\varphi(t)$  表示  $t$  时刻忆感器的磁通,  $L_M^{-1}$  为忆感值的倒数. 若定义如下参数

$$\rho = \int_{-\infty}^t \varphi(\tau) d\tau, \quad (10)$$

则 (9) 式可改写为

$$d\rho(\rho) = L_M^{-1}(\rho) d\rho. \quad (11)$$

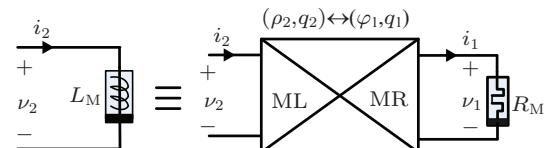

即忆感器可由  $\rho$  与  $q$  的函数关系进行描述, 而忆阻器是由  $\varphi$  和  $q$  定义的. 忆阻器与忆感器之间的转换关系可以通过图 4 示意图进行说明.

图 4 忆阻器与忆感器转换示意图

将忆阻器连接在转换电路的右端口, 经过转换后, 左端口的输出应满足忆感器  $\rho$ - $q$  函数关系. 因此, 转换电路设计的关键是实现忆阻器  $(\varphi_1, q_1)$  关系向忆感器  $(\rho_2, q_2)$  关系的转化.

经过上述的分析可知, 忆感器等效电路模型建立的基础是: 忆阻器的磁通与忆感器的磁通积分之间、忆阻器电荷量与忆感器电荷量之间的关系应满足

$$\rho_2 = k_x \varphi_1, \quad (12)$$

$$q_2 = k_y q_1. \quad (13)$$

在本文设计的忆感器等效电路模型中, 磁通与磁通的积分均由电压表示. 因此  $k_x$  和  $k_y$  均为实系数, 且对于不同的转换电路其取值不同. 对 (12) 式, (13) 式左右同时进行微分运算, 可得

$$\frac{1}{k_x} \int v_2 dt = v_1, \quad (14)$$

$$i_2 = k_y i_1. \quad (15)$$

上式中,  $v_2$  和  $i_2$  表示忆感器的端电压和流过电流,  $v_1$  和  $i_1$  表示忆阻器的端电压和流过电流.

由 (14) 式, (15) 式可以看出, 流过忆感器的电流与流过忆阻器的电流成比例, 同时忆感器的磁通与忆阻器的端电压呈线性比例关系. 因此满足电流-电压磁滞回线特性的忆阻器经过转换电路得到的忆感器, 其电流-磁通相图也必然具有磁滞环特性.

本文设计的转换电路采用两个电流反馈型运算放大器 AD844、一个运算放大器 TL084、若干电阻及电容元器件, 如图 5 中所示.

图 5 忆感器等效电路模型

在图 5 中, 将两个 AD844 分别记为  $U_5$  和  $U_6$ , 运算放大器 TL084 记为  $U_7$ . AD844 由第二代电流传输器 CCII+ 与单位电压增益跟随器组成. 其  $z$  端电流跟随  $x$  端电流, 且  $I_z$  与  $I_x$  方向相同.  $x$  端电压跟随  $y$  端电压.  $y$  端输入电流为 0, 且与  $y$  端电压无关. 单位电压增益跟随器的输出电压与  $z$  端电压相同. 根据 AD844 的输入输出特性, 可以得到以下方程:

$$i_2 = i_{rx}, v_2 = v_{ri}, i_{ri} = i_{ci}, \quad (16)$$

$$v_1 = v_{ci}, i_1 = i_{rd}, v_d = -v_{rx}. \quad (17)$$

上述方程中  $v_{rx}$  和  $i_{rx}$  分别为电阻  $R_x$  两端的电压和流过电流,  $v_{ri}$  和  $i_{ri}$  分别为电阻  $R_i$  两端的电压和流过电流,  $v_{ci}$  和  $i_{ci}$  为电容  $C_i$  两端的电压和流过电流,  $i_{rd}$  代表流过电阻  $R_d$  的电流,  $v_d$  代表  $U_7$  的输出电压.

电容  $C_i$  的端电压  $v_{ci}$  和忆感器端电压  $v_2$  的积

分呈正比关系, 即

$$v_1 = v_{ci} = \frac{1}{R_i C_i} \int v_2 dt. \quad (18)$$

电阻  $R_d$  的端电压正比于流过忆阻器的电流  $i_{rd}$ , 因此  $i_1$  与  $i_2$  同样满足正比关系,

$$i_2 = \frac{i_1 \cdot R_d}{R_x}. \quad (19)$$

对比 (14), (15) 式与 (18), (19) 式可知,  $k_x = R_i C_i$ ,  $k_y = R_d / R_x$ , 由此可推导出等效电路模型的电感倒数

$$L_M^{-1} = W_M \cdot \frac{R_d}{R_x C_i R_i}. \quad (20)$$

将 (8) 式代入 (20) 式, 得

$$L_M^{-1} = \delta \cdot \rho_2 + \gamma. \quad (21)$$

其中,

$$\delta = \frac{a R_2 R_7 R_d}{R_1 R_5 R_3 C_1 R_x \cdot (R_i C_i)^2},$$

$$\gamma = \left( \frac{aR_7}{R_6} v_{\text{offset}} + b \right) \cdot \frac{R_d}{R_x C_i R_i}.$$

忆阻器的显著特点是阻值的受控性, 当对其施加交变电压激励时, 其电流与端电压同时过零点, 且电流-电压相图呈现磁滞环形。同样, 不同于传统电感元件, 忆感器的电流-磁通关系呈非线性, 且电感值可控。

当激励电压  $v_2(t) = U_0 \sin(2\pi ft) = U_0 \sin(\omega t)$ , 根据(2)式, (10)式和(21)式可以得到在正弦波电压激励下, 忆感器的磁通、磁通积分(假设积分初始值均为0)及等效电感倒数为

$$\begin{aligned}\varphi_2(t) &= \int v_2(t) dt = -\frac{U_0}{\omega} \cos(\omega t), \\ \rho_2(t) &= \int \varphi_2(t) dt = -\frac{U_0}{\omega^2} \sin(\omega t),\end{aligned}\quad (22)$$

$$L_M^{-1} = -\frac{\delta \cdot U_0}{\omega^2} \sin(\omega t) + \gamma. \quad (23)$$

根据(9)式, 可以得到磁通控制型忆感器的电流为

$$\begin{aligned}i_2(t) &= \left( -\frac{\delta \cdot U_0}{\omega^2} \sin(\omega t) + \gamma \right) \cdot \left( -\frac{U_0}{\omega} \cos(\omega t) \right) \\ &= \frac{\delta \cdot U_0^2}{2\omega^3} \sin(2\omega t) - \frac{\gamma U_0}{\omega} \cos(\omega t) \\ &= i'_2 + i''_2,\end{aligned}\quad (24)$$

其中

$$i'_2 = \frac{\delta \cdot U_0^2}{2\omega^3} \sin(2\omega t), \quad i''_2 = -\frac{\gamma U_0}{\omega} \cos(\omega t).$$

由(22)式, (24)式可知, 忆感器磁通  $\varphi_2$  的幅值正比于  $U_0/\omega$ 。流过忆感器的电流由二次谐波  $i'_2$  和基波  $i''_2$  组成,  $i''_2$  与  $\varphi_2$  相位相同、幅值呈正比例关系。 $i'_2$  幅值与  $U_0^2/\omega^3$  成正比, 二次谐波的存在使忆感器的电流-磁通相轨迹呈现磁滞环形。通过对(22)式, (24)式分析可知: 在相同的激励电压幅值下, 随着激励频率的增加, 磁通与电流的幅值均减小。对于同一时刻  $t$ ,  $i'_2$  分别与  $i''_2$ ,  $\varphi_2$  相比较, 其幅值减小的程度更大, 因此电流减小的幅度大于磁通减小的幅度。

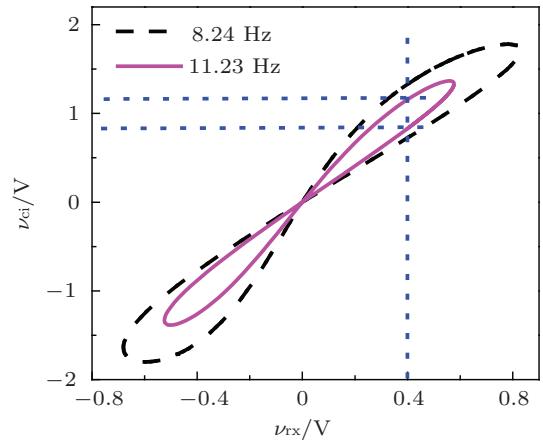

基于上述理论分析, 为了进一步验证本文提出忆感器等效电路模型的正确性, 采用 Pspice 软件进行仿真实验。正弦激励电压  $v_2(t) = \sin(2\pi ft)$ , 电路参数取值为:  $R_1 = R_2 = 10 \text{ k}\Omega$ ,  $R_3 = 51 \text{ k}\Omega$ ,  $R_4 = 680 \text{ k}\Omega$ ,  $C_1 = 100 \text{ nF}$ ,  $R_5 = 51 \text{ k}\Omega$ ,  $R_7 = 3 \text{ k}\Omega$ ,  $v_{\text{offset}} = 15 \text{ V}$ ,  $R_x = 1 \text{ k}\Omega$ ,  $R_d = 3 \text{ k}\Omega$ ,  $R_i = 10 \text{ k}\Omega$ ,  $C_i = 1 \mu\text{F}$ ,  $R_6$  为  $50 \text{ k}\Omega$  电位器。直流供电电压为  $\pm 15 \text{ V}$ 。流过忆感器的电流  $i_2$  与电阻  $R_x$  两端的电压

成比例, 因此用  $v_{rx}$  表示  $i_2$ 。同理, 忆感器的磁通  $\varphi_2$  可用电容  $C_i$  的端电压  $v_{ci}$  表示。当激励电压的频率  $f$  分别取  $11.23 \text{ Hz}$  和  $8.24 \text{ Hz}$  时, 忆感器磁通  $\varphi_2$  和流过电流  $i_2$  的李萨如相轨迹如图 6 所示。

图 6 忆感值在  $v_{rx}$ - $v_{ci}$  平面内相轨迹

图 6 表明, 在同一个不为零的激励电流取值下, 等效电路模型中忆感器的磁通值不唯一。以  $f = 11.23 \text{ Hz}$ ,  $v_{rx} = 0.4 \text{ V}$ (电流  $i_2 = 0.4 \text{ mA}$ ) 条件下的磁通取值为例, 当  $v_{rx} = 0.4 \text{ V}$  且  $dv_{rx}/dt > 0$ (即  $v_{rx}$  增大) 时,  $v_{ci} = 1.16 \text{ V}$ ,  $L_M = 29.02 \text{ H}$ ; 当  $v_{rx} = 0.4 \text{ V}$  且  $dv_{rx}/dt < 0$ (即  $v_{rx}$  减小) 时,  $v_{ci} = 0.83 \text{ V}$ ,  $L_M = 20.75 \text{ H}$ 。

比较频率分别为  $8.24 \text{ Hz}$  和  $11.23 \text{ Hz}$  时的轨迹图, 可以得到忆感器的重要特征: 等效忆感值在  $i_2$ - $\varphi_2$  平面内保持形如斜“8”字形的磁滞环, 且随着激励电压频率的增大, 电流与磁通的幅值将减小, 磁滞环向内收缩。图 6 表明 Pspice 仿真结果与理论分析一致, 证明了本文设计忆感器等效电路模型的正确性。

## 4 忆感器特性实验验证

为了进一步证明模型的正确性和有效性, 依照 Pspice 仿真电路中的参数取值, 搭建了硬件实验电路。忆感器的显著特点是流入的电流与磁通同时过零点, 相轨迹呈现磁滞环形。本节重点分析在不同激励电压频率、电压波形的情况下, 忆感值相轨迹的变化规律。

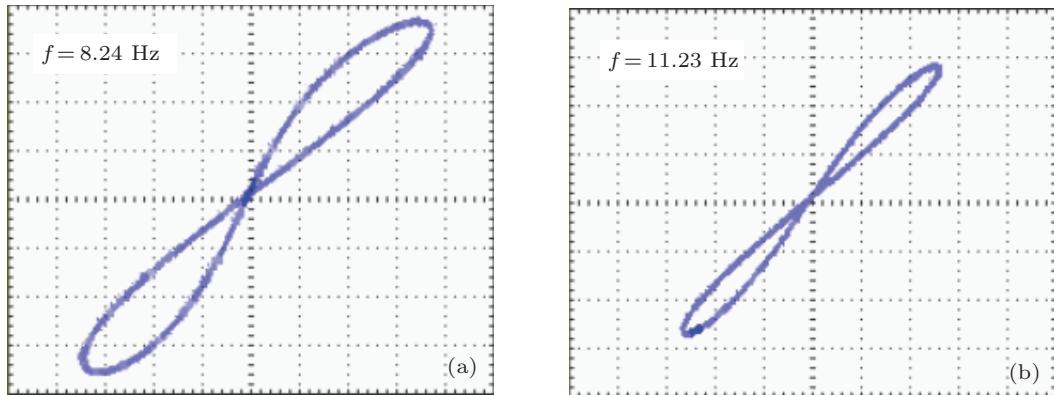

### 4.1 激励电压频率对忆感值相轨迹的影响

加在忆感器两端的正弦电压信号由信号发生器 BXY1-VC2000 产生, 幅值  $U_o = 1 \text{ V}$ , 频率  $f$  分别

取 11.23 Hz 和 8.24 Hz。为了与仿真结果进行比较，采用了示波器 TDS20114 对实验结果进行记录，如图 7 所示。

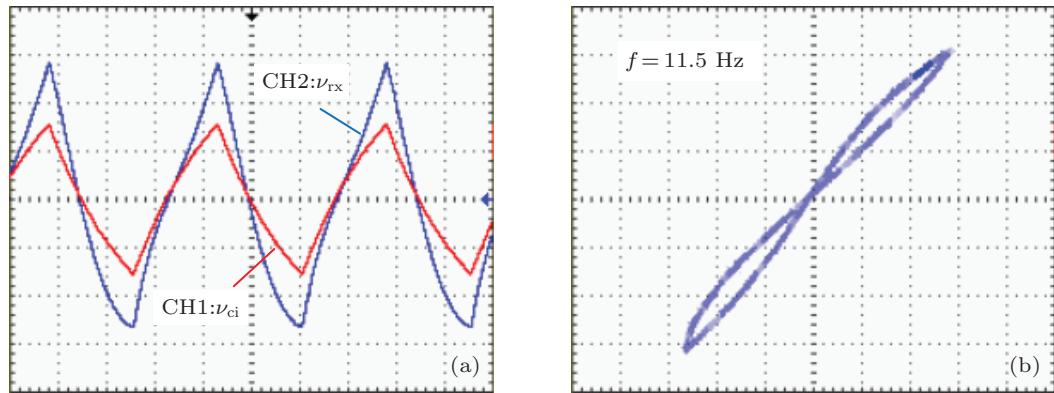

## 4.2 激励电压波形对忆感值相轨迹的影响

忆感器激励电压为方波，幅值  $U_o = 0.86$  V、频率  $f = 11.5$  Hz，实验结果如图 8 所示。图 8(a) 是  $v_{ci}$ (磁通) 和  $v_{rx}$ (电流) 的时域波形，图 8(b) 是忆感值的磁滞环波形  $v_{rx}-v_{ci}$ 。

比较图 7 与图 6 可以看出，硬件实验结果和 Pspice 仿真结果一致。磁通与电流的幅值随着激励

电压频率的增大而减小，磁滞环向内收缩。

比较图 7 与图 8 可知，当激励电压为方波时，忆感器的  $i_2-\varphi_2$  轨迹也呈现磁滞环形。不同的是忆感器等效电路模型在方波激励下， $v_{ci}$  与  $v_{rx}$  的时域波形在峰值点处为非光滑过渡，因此对应于图 8(b) 中  $v_{rx}-v_{ci}$  磁滞环端部呈现尖角状。

忆感器磁通(即电压  $v_{ci}$ )在激励电压为方波时近似为三角波，可以展开成包含不同频率项的傅里叶级数。因此，在各次谐波频率上， $i_2-\varphi_2$  轨迹也表现为基频正弦波激励下的过零磁滞环形。(24) 式同时也表明，在高次谐波点上， $i'_2$  幅值很小，对应的磁滞回线特征可以忽略。

图 7 激励电压为正弦波时，忆感值在  $v_{rx}-v_{ci}$  平面变化轨迹 (a)  $f = 8.24$  Hz; (b)  $f = 11.23$  Hz; (a), (b) 横坐标为 200 mV/div, 纵坐标为 500 mV/div

图 8 激励电压为方波时实验结果 (a)  $v_{rx}$  和  $v_{ci}$  的时域波形，横坐标为 25 ms/div, 纵坐标 CH1: 1 V/div, CH2: 200 mV/div; (b) 磁滞环波形  $v_{rx}-v_{ci}$  横坐标规格为 200 mV/div, 纵坐标为 500 mV/div

## 5 $RL_M C$ 串联电路

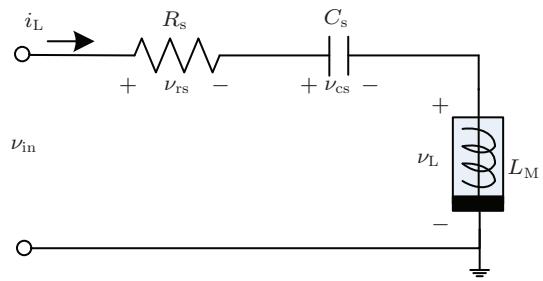

将本文设计的忆感器等效电路模型与电阻、电容串联组成  $RL_M C$  串联电路，其电路结构如图 9 所示。

根据欧姆定律，电阻  $R_s$ ，电容  $C_s$  两端的电压可以表示为

$$v_{rs} = i_L R_s, v_{cs} = \frac{q_L}{C_s}. \quad (25)$$

其中， $i_L$  为流过  $RL_M C$  串联电路的电流， $q_L$  为  $i_L$  的

积分. (11) 式两端进行积分可得

$$q_L(t) = \frac{1}{2} \delta \cdot \rho_L^2(t) + \gamma \rho_L(t). \quad (26)$$

根据基尔霍夫电压定律, (25) 式, (26) 式和 (9) 式可以将  $RL_M C$  串联电路两端的电压  $v_{in}$  表示为

$$v_{in} = L_M^{-1} \cdot \varphi_L \cdot R_s + \frac{\frac{1}{2} \delta \cdot \rho_L^2(t) + \gamma \rho_L(t)}{C_s} + v_L. \quad (27)$$

定义以下变量

$$x_1 = \rho_L(t), x_2 = \varphi_L(t), \quad (28)$$

从而得到描述此  $RL_M C$  串联电路的微分方程

$$\begin{aligned} \frac{dx_1}{dt} &= x_2, \\ \frac{dx_2}{dt} &= v_{in} - (\delta x_1 + \gamma) \cdot x_2 \cdot R_s \\ &\quad - \frac{\frac{1}{2} \delta \cdot x_1^2(t) + \gamma x_1(t)}{C_s}. \end{aligned} \quad (29)$$

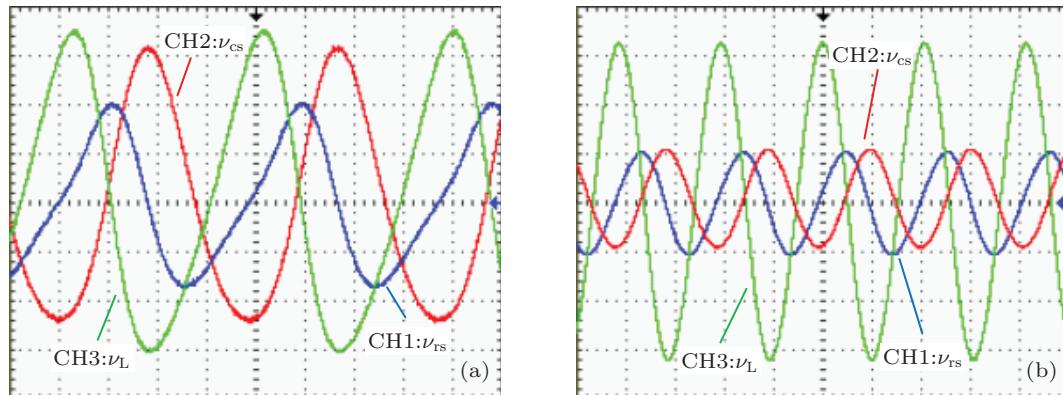

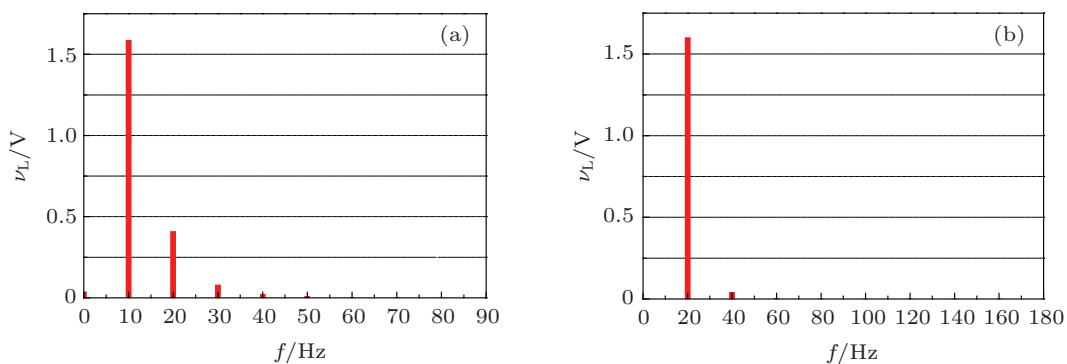

方程 (29) 表明由忆感器组成的  $RL_M C$  串联电路为二阶动态电路. 为了更好地观测其动态特性, 搭建硬件实验电路. 参数取值为  $R_s = 1 \text{ k}\Omega$ ,  $C_s = 10 \mu\text{F}$ . 当  $RL_M C$  电路两端激励电压为正弦波  $v_{in} = 1.42 \sin(2\pi ft)$ , 频率  $f$  分别取 10 Hz 和 20 Hz 时得到的实验波形如图 10 所示; 当激励电压为幅值 1.5 V 的三角波, 频率  $f$  分别取 10 Hz 和 20 Hz 时得到的实验波形如图 11 所示. 其中蓝色为电阻  $R_s$  两端的电压  $v_{rs}$ , 红色为电容  $C_s$  两端的电压  $v_{cs}$ , 绿色为忆感器两端的电压  $v_L$ .

图 9  $RL_M C$  串联电路

图 10 激励电压为正弦波时  $v_{rs}$ ,  $v_{cs}$ ,  $v_L$  的波形 (a)  $f = 10 \text{ Hz}$ ; (b)  $f = 20 \text{ Hz}$  横坐标规格为 25 ms/div, 纵坐标三个通道 CH1, CH2, CH3 均为 500 mV/div

图 11 激励电压为三角波时  $v_{rs}$ ,  $v_{cs}$ ,  $v_L$  的波形 (a)  $f = 10 \text{ Hz}$ ; (b)  $f = 20 \text{ Hz}$  横坐标规格为 25 ms/div, 纵坐标三个通道 CH1, CH2, CH3 均为 500 mV/div

图 10 和图 11 所示实验结果表明, 在给定频率条件下, 忆感器两端的电压  $v_L$  超前于电阻两端的电压  $v_{rs}$ , 电阻两端的电压  $v_{rs}$  又超前于电容两端的电压  $v_{cs}$ . 表明本文所搭建的忆感器等效电路模型具有电感的特性. 由于忆感器内部非线性, 图 10(a) 中电压波形已不再是标准的正弦信号. 通过比较频率  $f = 10 \text{ Hz}$ ,  $f = 20 \text{ Hz}$  时的实验波形, 可以看出随着频率的增大,  $RLMC$  串联电路中忆感器端电压逐渐增大, 而电阻和电容的端电压逐渐减小, 同时

由于频率增大, 使得忆感值的磁滞环波形向内收敛, 非线性程度减弱. 当激励电压三角波频率为 20 Hz 时,  $RLMC$  串联电路实验波形与传统  $RLC$  串联电路的电压电流特性相近. 当频率减小到 10 Hz 时, 忆感器的非线性明显增大, 导致  $v_L$  的波形出现了非线性折点 A, B.

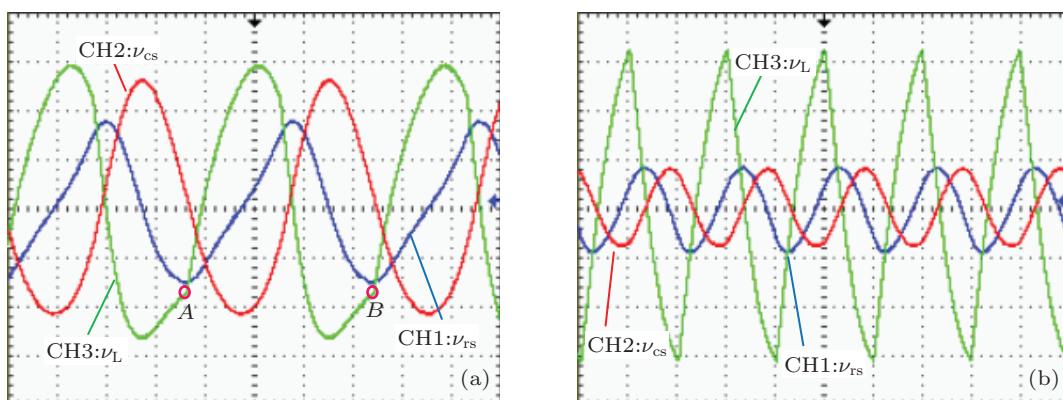

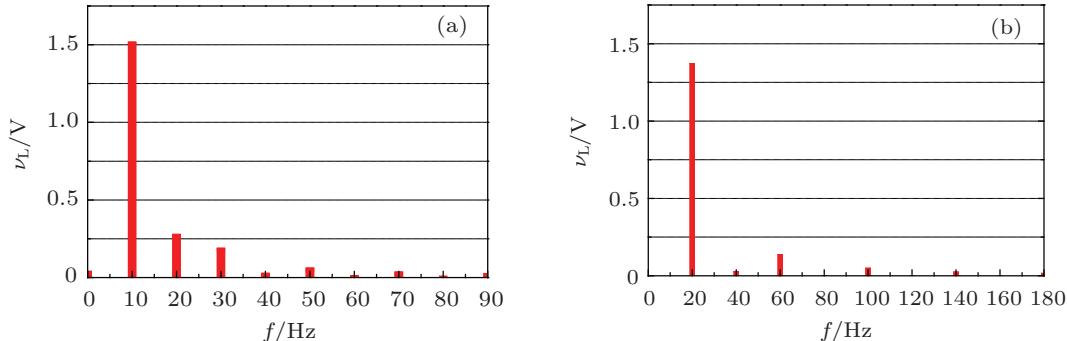

为了进一步分析  $RLMC$  串联电路特征, 对不同激励电压波形在不同频率下忆感器的端电压进行了频谱分析, 结果如图 12 和图 13 所示.

图 12 激励电压为正弦波时, 忆感器两端电压的频谱分析图 (a)  $f = 10 \text{ Hz}$ ; (b)  $f = 20 \text{ Hz}$

图 13 激励电压为三角波时, 忆感器两端电压的频谱分析图 (a)  $f = 10 \text{ Hz}$ ; (b)  $f = 20 \text{ Hz}$

由图 12 可以看出, 在忆感器与 RC 串联、激励电压为正弦信号条件下, 忆感器的端电压主要是由基波和二次谐波组成, 且随着频率的增大, 谐波分量明显减小. 因受忆感器特性的影响, 激励频率越大, 电流磁通相图收缩程度越大, 也越接近传统电感. 在激励电压为三角波信号时, 从图 13 中可以看出, 由于忆感器的非线性影响, 其端电压波形中也包含了各次谐波分量. 且二次、三次谐波分量幅值较大. 随着频率的增加, 各次谐波分量的幅值也逐渐减小, 在  $f = 20 \text{ Hz}$  时三次谐波分量仍然明显, 这是由于三角波自身包含奇次谐波分量. 通过对图

12、图 13 的分析可以得到: 激励电压为正弦波和三角波条件下, 由于受到忆感器非线性影响, 使得忆感器端电压频谱中出现了的明显二次谐波分量, 且随着频率的增加幅值减小. 由上述分析可知, 本文建立的忆感器等效电路模型可以应用在实际电路中, 具有一定的有效性.

## 6 结 论

本文建立了一个模拟磁通控制型忆感器的等效电路模型. 模型主要由运算放大器 TL084、电流反馈型运算放大器 AD844、光耦电阻等元器件

组成。仿真和实验结果均验证了模型具有忆感器的特性, 可以用于实际电路设计。本文设计的忆感

器等效电路模型对后续忆感器研究具有一定的参考价值。

- [1] Chua L O 1971 *IEEE Trans. Circ. Th.* **18** 507

- [2] Chua L O, Kang S M 1976 *Proc. IEEE* **64** 209

- [3] Strukov D B, Snider G S, Stewart D R, Williams R S 2008 *Nature* **453** 80

- [4] Wang W, Ma D G, 2010 *Chin. Phys. Lett.* **27** 018503

- [5] Liu Y, Song Z T, Ling Y, Feng S L 2010 *Chin. Phys. Lett.* **27** 038502

- [6] Huang L, Huang A P, Zheng X H, Xiao Z S, Wang M 2012 *Acta Phys. Sin.* **61** 137701 (in Chinese) [黄力, 黄安平, 郑晓虎, 肖志松, 王政 2012 物理学报 **61** 137701]

- [7] Bao B C, Hu X, Xu J P, Liu Z, Zou L 2011 *Acta Phys. Sin.* **60** 120502 (in Chinese) [包伯成, 胡许, 许建平, 刘中, 邹凌 2011 物理学报 **60** 120502]

- [8] Bao B C, Liu Z, Xu J P 2010 *Acta Phys. Sin.* **59** 3785 (in Chinese) [包伯成, 刘中, 徐建平 2010 物理学报 **59** 3785]

- [9] Jia L N, Huang A P, Zheng X H, Xiao Z S, Wang M 2012 *Acta Phys. Sin.* **61** 217306 (in Chinese) [贾林楠, 黄安平, 郑晓虎, 肖志松, 王政 2012 物理学报 **61** 217306]

- [10] Pershin Y V, Chua L O 2009 *Proc. IEEE* **97** 1717

- [11] Rák A, Cserey G 2010 *IEEE Trans. Computer-Aided Design of Integr. Circ. Syst.* **29** 632

- [12] Batas D, Fiedler H 2011 *IEEE Trans. Nano* **10** 250

- [13] Shin S, Kang S M 2010 *IEEE Trans. Computer-Aided Design of Integr. Circ. Syst.* **29** 590

- [14] Kim H, Sah M P, Yang C, Cho S, Chua L O 2012 *IEEE Trans. Circuits Syst. I: Reg. Papers* **59** 2422

- [15] Pershin Y V, Ventra M D 2010 *IEEE Trans. Circ. Syst. I: Reg. Papers* **57** 1857

- [16] Valsa J, Biolek D, Biolek Z 2010 *Int. J. Numer. Model.* **24** 400

- [17] Wang X Y, Fitch A L, Lu H H C, Qi W G 2012 *Chin. Phys. B* **21** 108501

- [18] Biolek D, Biolek Z, Biolkova V 2011 *Analog Intergr. Circ. Sig. Process* **66** 129

- [19] Pershin Y V, Ventra M D 2010 *Electron. Lett.* **46** 517

- [20] Senani R 1982 *Electrocomponent Sci. Techn.* **10** 7

# A novel meminductor emulator based on analog circuits\*

Liang Yan Yu Dong-Sheng<sup>†</sup> Chen Hao

(The School of Information and Electrical Engineering, China University of Mining and Technology, Xuzhou 221116, China)

(Received 6 March 2013; revised manuscript received 11 April 2013)

## Abstract

Meminductor, a nonlinear device with memory ability and controllable meminductance, was generalized on the basis of the conception of memristor. Currently, meminductor is still unavailable on the market. Therefore, in order to investigate its properties and potential application, designing electronic emulator is of significant importance. In this paper, a flux-controlled memristive emulator using light-dependent resistor (LDR) is proposed and the mutator for transferring memristor into a flux controlled meminductor is described, of which the realization is on the basis of two current conveyor chips and operational amplifiers. Results of Pspice simulation and hardware experiments indicate that the current-flux characteristic of the meminductor is a frequency-dependent pinched loop, like an inclined number “8”. To confirm the effectiveness and correctness, the proposed emulator is analyzed theoretically and tested experimentally as it is connected in an  $RL_M C$  series circuit. The dynamic behaviors of the  $RL_M C$  circuit are analyzed and observed. All the results manifest that this newly proposed emulator is capable of simulating a nonlinear meminductor and can be applied to the analog circuit design.

**Keywords:** memristor, meminductor, hysteretic loop, Pspice

**PACS:** 85.25.Hv, 07.50.Ek

**DOI:** 10.7498/aps.62.158501

\* Project supported by the Fundamental Research Funds for the Central Universities of China (Grant No. 2013QNB28).

† Corresponding author. E-mail: dongsiee@163.com