# 氮掺杂 $\text{Ge}_2\text{Sb}_2\text{Te}_5$ 相变存储器的多态存储功能

赖云锋<sup>1)</sup> 冯洁<sup>1)†</sup> 乔保卫<sup>1)</sup> 凌云<sup>2)</sup> 林殷茵<sup>2)</sup>

汤庭鳌<sup>2)</sup> 蔡炳初<sup>1)</sup> 陈邦明<sup>3)</sup>

1) 上海交通大学微米/纳米加工技术国家重点实验室, 薄膜与微细技术教育部重点实验室, 上海 200030)

2) 复旦大学专用集成电路和系统国家重点实验室, 上海 200433)

3) Silicon Storage Technology, Inc., Sunnyvale 94086, USA)

(2005 年 12 月 6 日收到 2006 年 3 月 28 日收到修改稿)

通过反应溅射的方法, 制备了 N 掺杂的  $\text{Ge}_2\text{Sb}_2\text{Te}_5$ (N-GST) 薄膜, 用作相变存储器的存储介质。研究表明, 掺杂的 N 以 GeN 的形式存在, 不仅束缚了  $\text{Ge}_2\text{Sb}_2\text{Te}_5$ (GST) 颗粒的长大也提高了 GST 的晶化温度和相变温度。利用 N-GST 薄膜的非晶态、晶态面心立方相和晶态六方相的电阻率差异, 能够在同一存储单元中存储三个状态, 实现相变存储器的多态存储功能。

关键词: 相变存储器, 多态存储, N 掺杂,  $\text{Ge}_2\text{Sb}_2\text{Te}_5$

PACC: 7865P, 8730G

## 1. 引言

近几年随着便携式电子产品的增多, 人们对非挥发存储器的需求急剧增长。基于  $\text{Ge}_2\text{Sb}_2\text{Te}_5$ (GST) 的相变存储器由于具有快速的读写速度、高密度存储能力以及能够和目前的 CMOS 工艺兼容等优点<sup>[1,2]</sup>, 被业界认为最有希望替代闪存(flash memory)成为下一代非挥发存储器的主流存储技术。基于 GST 的相变存储器是利用 GST 在非晶态与晶态之间的巨大电阻率差异实现双稳态的存储<sup>[3,4]</sup>。当一个宽而矮的电脉冲经过非晶态(高阻态)的 GST 薄膜, 电流产生的焦耳热能够使 GST 发生晶化, 从而实现高阻态到低阻态的转变; 为了使 GST 从晶态(低阻态)回复到非晶态(高阻态), 只要施加一个窄而高的电脉冲加热 GST 到达熔点以上, 而后在脉冲的“陡降”过程中, 通过急速冷却就可以使 GST 回复到非晶态<sup>[5-8]</sup>。

在存储技术的诸多研究内容中, 如何提高存储密度是人们永恒不变的研究内容。多态存储技术就是其中一种提高存储密度的手段。所谓多态存储技术就是在同一个存储单元内存储两个以上状态, 这样可以在不降低存储单元尺寸的前提下有效地增

加单位面积的存储密度。

本研究利用磁控溅射仪制备了 N 掺杂的 GST(N-GST) 薄膜, 用作相变存储器的存储介质。研究了 N 掺杂对 GST 结晶特性和电学性能的影响。研究表明, N-GST 薄膜能够实现相变存储器的多态存储功能。

## 2. 实验方法

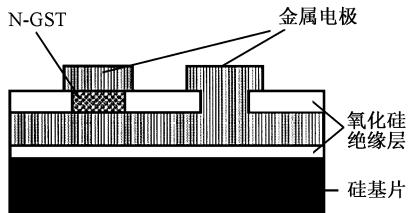

采用超高真空 5 靶磁控溅射仪, 通过反应溅射将 N-GST 薄膜沉积在热氧化的硅片上。溅射中 Ar 的分压控制在 0.207 Pa, 而薄膜中的 N 浓度通过调节  $\text{N}_2$  的分压得以控制。为了方便比较, 也制备了不掺 N 的 GST 薄膜。两种薄膜的制备条件如表 1 所列。薄膜中的 N 浓度通过 X 射线光电子能谱(XPS)标定为 1.3 at%。沉积之后的薄膜用 Ar 气保护, 在不同的温度下退火 10 min, 而后用四探针法测量薄膜的电阻率, 并通过 X 射线衍射(XRD)谱研究退火薄膜的结晶特性。采用差示扫描量热分析(DSC)测量了两种薄膜粉末样品的晶化温度和相变温度。为了研究 N 掺杂对 GST 存储特性的影响, 我们分别以 GST 薄膜和 N-GST 薄膜为存储介质, 采用图 1 所示的结构制备了存储器原型器件, 并且测量了原型器件的电流-电压( $I-V$ )特性和电阻-电压( $R-V$ )特性。

表1 薄膜的制备条件

| 样品名称  | 本底真空/ $10^{-5}$ Pa | 溅射功率/W | 总溅射气压/Pa | $N_2$ 分压比( $P_{N_2}/P_{total}$ ) |

|-------|--------------------|--------|----------|----------------------------------|

| GST   | 1                  | 30     | 0.207    | 0                                |

| N-GST | 1                  | 30     | 0.231    | 10.4%                            |

图1 相变存储器结构示意图

### 3. 结果及讨论

#### 3.1. N掺杂对GST结晶特性的影响

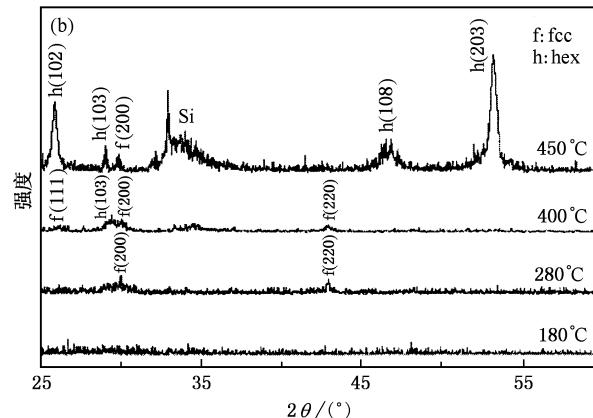

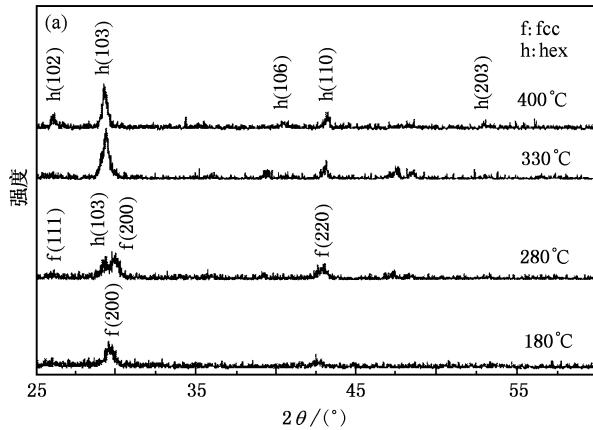

图2是GST薄膜和N-GST薄膜在不同温度下退火10 min后测量得到的XRD谱图。从图2可以看出,当退火温度为180 °C时,GST薄膜的XRD谱线中可以观察到晶态面心立方(fcc)相的衍射峰,而N-GST薄膜的XRD谱线中没有观察到衍射峰。这说明此温度下,GST薄膜已经晶化,而N-GST薄膜还没有晶化。N掺杂提高了GST的晶化温度。当退火温度为280 °C时,GST的XRD谱线中既可以观察到晶态fcc相的衍射峰也可以观察到晶态六方(hex)相的衍射峰,而此时N-GST的XRD谱线中只能观察到fcc相的衍射峰。说明280 °C时,GST已经发生了 $fcc \rightarrow hex$ 的相转变而N-GST还没有发生此转变。当退火温度到达400 °C时,GST的XRD谱图中只能观察到hex相的衍射峰,而N-GST的XRD谱图中仍然可以观察到fcc相和hex相的衍射峰。这说明此温度下GST的相转变结束,而N-GST的相转变还在进行中。N掺杂提高了GST的相变温度。

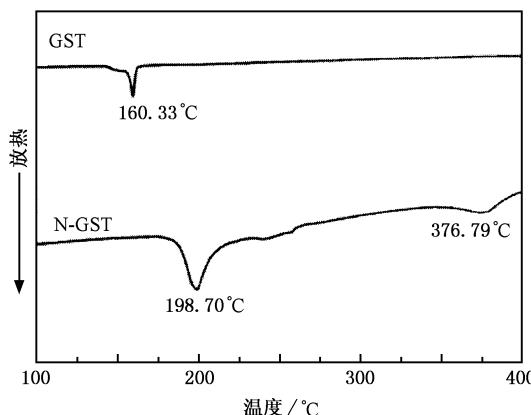

为了进一步证实N掺杂提高了GST的晶化温度和相变温度,我们使用DSC测量了两种材料的晶化温度和相变温度(图3)。在两种材料的DSC曲线上都可以观察到至少一个放热峰,其中第一个放热峰对应着材料的晶化温度,而第二个放热峰对应着 $fcc \rightarrow hex$ 的相变温度。从图3的DSC曲线上可以看出,N掺杂使GST的晶化温度从160.33 °C提升至198.7 °C。然而,图3中没有观察到GST相变温度对

图2 GST薄膜(a)和N-GST薄膜(b)经过不同退火温度处理后的XRD谱

应的放热峰,只观察到了N-GST相变温度对应的放热峰(376.79 °C)。结合XRD谱(图2)以及电阻率与退火温度的关系,我们可以看出GST由 $fcc \rightarrow hex$ 的相转变是一个渐变过程,转变中热量是缓慢释放的。而N-GST从 $fcc \rightarrow hex$ 的相转变是一个突变过程,该过程释放的热量相对集中。因此,DSC能够较容易检测到N-GST的相变放热峰,无法检测到GST的相变放热峰。而文献[7]报道了GST的相变温度小于300 °C。因此,N掺杂提高了GST的晶化温度和相变温度。

由于相变存储器是一种非挥发存储器,这就要求在断电的情况下写入的数据仍然能够得到很好保存。晶化温度和相变温度的适当提高,将会有助于相变存

图3 两种材料的DSC曲线

储器的数据保存特性起到积极的作用。因为在相变存储器从低阻态回复到高阻态的过程中,由于受到电脉冲的加热,GST的温度必然高于熔点(632 °C<sup>[9]</sup>),由此产生的高温会对邻近的存储单元产生影响。适当提高GST的晶化温度和相变温度能够增强GST非晶态和晶态fcc相的热稳定性<sup>[10]</sup>,从而提高相变存储器抵抗热串扰的能力。

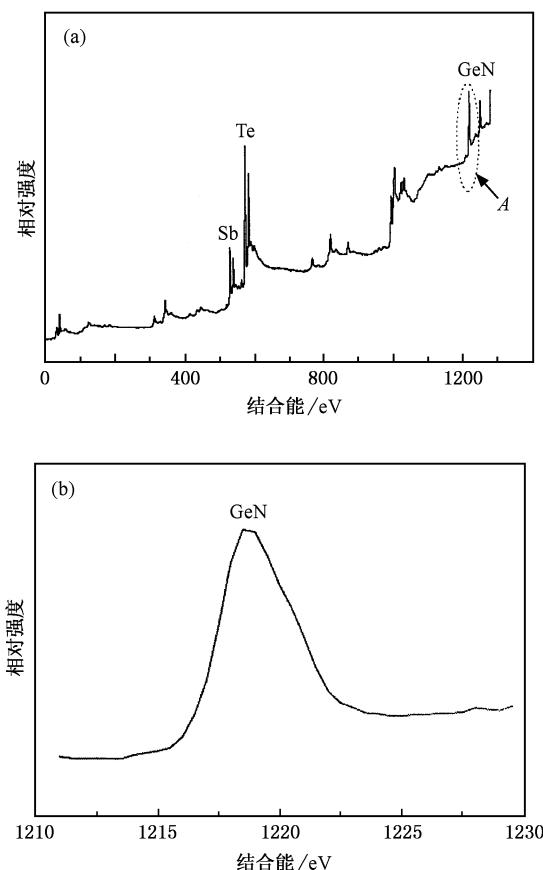

图4是由N-GST薄膜测量得到的XPS图,图中可以观察到Ge-N峰<sup>[11]</sup>,这表明其中的N以GeN的形式存在于GST中<sup>[12]</sup>。我们利用XRD谱线,通过谢乐公式计算了两种材料的平均晶粒大小,结果表明N掺杂使GST薄膜fcc相的平均晶粒从9.18 nm减小到2.71 nm,hex相的平均晶粒从21.13 nm减小到14.07 nm。N掺杂明显地细化了GST的晶粒<sup>[13,14]</sup>。由于相变存储器技术是目前“闪存”技术的替代升级技术,主要用于45 nm以下的尺度范围<sup>[15]</sup>,因此适当控制GST晶粒的长大,使薄膜晶化后得到纳米晶薄膜,能够降低从晶态到非晶态的编程电流<sup>[16]</sup>,使其满足纳米尺度的存储要求。研究还表明<sup>[17,18]</sup>,由于GeN束缚了晶粒的长大,也能够提高相变存储器的循环擦写次数,增长相变存储器的使用寿命。

### 3.2.N掺杂对GST电学特性的影响

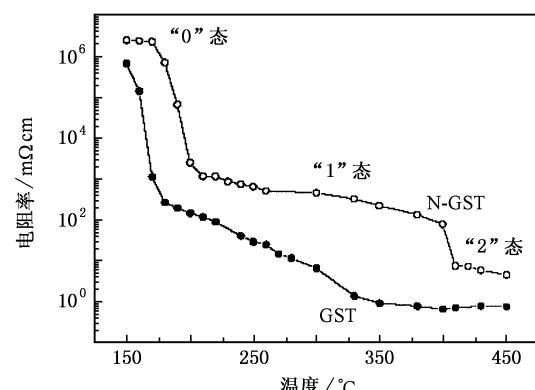

图5是GST薄膜和N-GST薄膜的电阻率随退火温度变化的曲线。对于GST薄膜,当退火温度达到约160 °C时,电阻率会突然降低,而后随着退火温度升高电阻率逐渐降低,当退火温度高于350 °C以后薄膜电阻率趋于稳定。对于N-GST薄膜,电阻率在约200 °C时突然下降,而后在200—400 °C范围内保持了基本稳定的电阻率,当退火温度达到400 °C时,电阻率再次突然下降。这样,在N-GST薄膜的电

图4 N-GST薄膜的XPS图 (b)图为(a)图的局部放大

阻率变化曲线上可以观察到两个明显的电阻率下降沿,分别对应着晶化温度和相变温度,而在GST薄膜的电阻率变化曲线上,我们只观察到了一个电阻率下降沿,对应着GST的晶化温度。这和DSC测量得到的结果是一致的。N掺杂产生的另一个效果就是在电阻率变化曲线上形成了三个较为稳定的电阻率“平台”。电阻率“平台”的形成和电阻率突变下降沿的产生,增强了N-GST非晶态、晶态fcc相和晶态

图5 薄膜电阻率与退火温度的关系

hex 相之间的电阻率区分度。如果将 N-GST 薄膜 200 ℃ 以下的电阻率作为“0”态, 200—400 ℃ 的电阻率作为“1”态, 高于 400 ℃ 的电阻率作为“2”态, 就能够在同一个存储单元中存储三个状态。

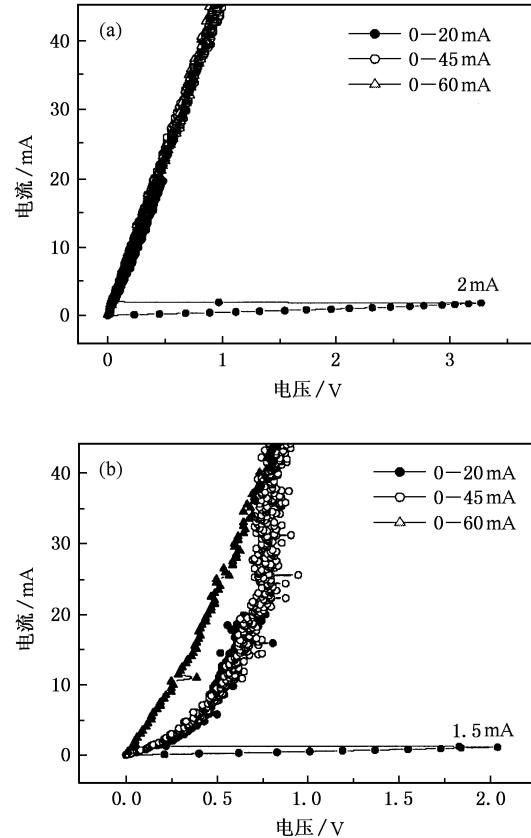

为了证实以上实现多态存储的构想, 我们分别以 GST 和 N-GST 作为存储介质, 制备了存储器原型器件, 并且对器件进行了  $I-V$  曲线的测试(图 6)。测试中对每个器件都进行连续三次扫描, 每次扫描的电流范围不同。如图 6(a)所示, 在第一次扫描(0—20 mA)中, 当施加电流达到 2 mA 时, 曲线上出现了负阻区域, 曲线的斜率也突然变大了。这说明施加电流达到 2 mA 时, 器件电阻突然由较高的电阻状态转变到较低的电阻状态。随后两次连续扫描(0—45 和 0—60 mA)得到的  $I-V$  曲线和第一次扫描转变后的  $I-V$  曲线是重合的。这说明了转变后的低电阻状态得到了保存, 而且整个晶化过程中只出现了两个电阻状态(最高电阻态和最低电阻态)。而在图 6(b)中可以看到, 在第一次扫描的过程中, 当施加电流达到 1.5 mA 时, 器件电阻也是从高阻态转变到了低阻态, 这种低电阻状态同样得到了保存。但是在第二次扫描(0—45 mA)中, 当施加电流高于 35 mA 时,  $I-V$  曲线上出现了不明显的负阻区域, 说明电阻可能进一步下降。接着进行第三次扫描(0—60 mA), 相对于第二次扫描的  $I-V$  曲线, 此时曲线斜率进一步增大, 而且在较高的电流范围(大于 35 mA)内, 第三次扫描的曲线和第二次扫描的曲线相重合。这进一步证实了在电流大于 35 mA 时, 器件的电阻有了进一步的下降, 而这种最低电阻状态同样得到了保存。从  $I-V$  曲线的初步分析可以看出: 对于使用 N-GST 作为存储介质的存储器, 具有三个不同的电阻状态, 能够存储三个状态; 而使用 GST 作为存储介质的存储器只有两个不同的电阻状态, 只能存储两个状态。

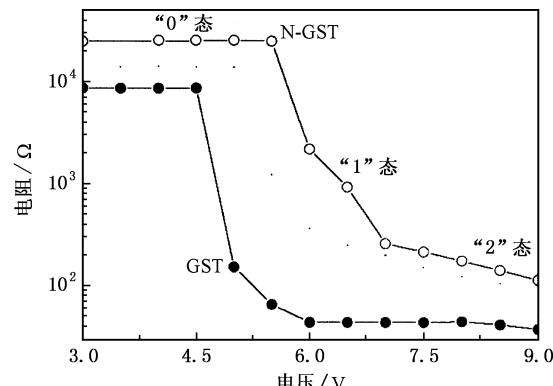

为了进一步证实 N-GST 薄膜的多态存储效应, 我们仿效存储器的写入原理, 进行  $R-V$  曲线的测试(图 7)。在实验中, 我们施加一个电压脉冲, 而后测量器件电阻的变化。从图 7 可以看出, 对于使用 GST 薄膜作为存储介质的存储器件, 当施加电压达到 4.75 V 时, 器件电阻直接从最高电阻状态( $9 \text{ k}\Omega$ )下降到最低电阻状态( $60\text{--}140 \Omega$ )。随着施加电压的进一步升高, 器件电阻保持在最低电阻状态; 而使用 N-GST 薄膜作为存储介质的存储器, 当施加电压达到 6 V 时, 器件电阻由最高电阻状态( $25 \text{ k}\Omega$ )下降到

了中间电阻状态( $800\text{--}2000 \Omega$ )。该状态的电阻值能够在施加电压为 6—7 V 的时候得到保持。当施加电压进一步高于 7 V 的时候, 器件电阻进一步从中间电阻状态下降到了最低电阻状态( $100\text{--}200 \Omega$ )。如果利用 N-GST 薄膜获得的三个电阻状态存储数据, 就能够在同一个存储单元中存储三个状态, 实现多态存储。

图 6 分别以 GST(a) 和 N-GST(b) 作为存储介质的相变存储器  $I-V$  特性曲线

图 7 基于 GST 和 N-GST 的相变存储器  $R-V$  特性曲线

## 4. 结 论

采用反应磁控溅射制备了 N 掺杂的 GST 薄膜。研究表明,掺杂的 N 以 GeN 的形式存在,不仅细化

了 GST 的晶粒而且提高了非晶态和晶态 fcc 相的高温稳定性。利用 N-GST 非晶态、晶态 fcc 相和晶态 hex 相之间的电阻率差异表征不同的存储状态,能够在同一个存储单元中存储三个状态,从而实现相变存储器的多态存储功能。

- [ 1 ] Lai S , Lowrey T 2001 *IEDM Tech . Dig .* ( Washington : IEEE ) p803

- [ 2 ] Maimon J , Spall E , Quinn R 2001 *IEEE Aero . Conf . Proc .* **5** 2289

- [ 3 ] Liu B , Song Z T , Zhang T et al 2004 *Chin . Phys .* **13** 1947

- [ 4 ] Liu B , Song Z T , Zhang T et al 2004 *Chin . Phys .* **13** 1167

- [ 5 ] Ovshinsky S R 1968 *Phys . Rev . Lett .* **21** 1450

- [ 6 ] Neale R , Nelson D , Moore G 1970 *Electron .* **43** 56

- [ 7 ] Qiao B W , Lai Y F , Feng J et al 2005 *J . Mater . Sci . Technol .* **21** 95

- [ 8 ] Zhang T , Liu B , Xia J L et al 2004 *Chin . Phys . Lett .* **21** 741

- [ 9 ] Kang D H , Ahn D H , Kim K B et al 2003 *J . Appl . Phys .* **94** 3536

- [ 10 ] Qiao B W , Feng J , Lai Y F et al 2006 *Chin . Phys . Lett .* **23** 172

- [ 11 ] Miao X S , Chong T C , Shi L P 2001 *Jpn . J . Appl . Phys .* **40**

1581

- [ 12 ] Kojima R , Kouzaki T , Matsunaga T et al 1998 *Proc . SPIE Int . Soc . Opt . Eng .* **3401** 14

- [ 13 ] Lai Y F , Qiao B W , Feng J et al 2005 *J . Electron . Mater .* **34** 176

- [ 14 ] Jeong T H , Kim M R , Seo H et al 2000 *Jpn . J . Appl . Phys .* **39** 2775

- [ 15 ] Lai S 2003 *IEDM Tech . Dig .* ( Washington : IEEE ) p255

- [ 16 ] Hwang Y N , Lee S H , Ahn S J et al 2003 *IEDM Tech . Dig .* ( Washington : IEEE ) p893

- [ 17 ] Kojima R , Okabayashi S , Kashihara T et al 1998 *Jpn . J . Appl . Phys .* **37** 2098

- [ 18 ] Horii H , Yi J H , Park J H et al 2003 *Symposium on VLSI Technology Digest of Technical Papers* ( Kyoto : IEEE ) p177

# Multiple-state storage capability of nitrogen-doped $\text{Ge}_2\text{Sb}_2\text{Te}_5$ film for phase change memory

Lai Yun-Feng<sup>1)</sup> Feng Jie<sup>1)†</sup> Qiao Bao-Wei<sup>1)</sup> Ling Yun<sup>2)</sup> Lin Yin-Yin<sup>2)</sup> Tang Ting-Ao<sup>2)</sup>

Cai Bing-Chu<sup>1)</sup> Chen Bang-Ming<sup>3)</sup>

1) State Key Laboratory of Micro/Nano Fabrication Technology, Key Laboratory for Thin Film and

Microfabrication of Ministry of Education, Shanghai Jiaotong University, Shanghai 200030, China

2) State Key Laboratory of Application Specific Integrated Circuit and System, Fudan University, Shanghai 200433, China

3) Silicon Storage Technology, Inc., Sunnyvale 94086, USA

(Received 6 December 2005; revised manuscript received 28 March 2006)

## Abstract

Nitrogen-doped  $\text{Ge}_2\text{Sb}_2\text{Te}_5$  (N-GST) film for phase change memory was prepared by reactive sputtering. Testing results show that doped nitrogen combines with Ge to form GeN, which not only restrains crystal grain growth but also increases the crystallization temperature and phase transformation temperature of  $\text{Ge}_2\text{Sb}_2\text{Te}_5$  (GST). Phase change memory (PCM) with N-GST can realize three-state storage in one PCM cell by using the resistivity difference between the amorphous state, the face centered cubic phase and the hexagonal phase of GST.

**Keywords:** phase change memory, multiple-state storage, nitrogen doping,  $\text{Ge}_2\text{Sb}_2\text{Te}_5$

**PACC:** 7865P, 8730G

† E-mail: jfeng@sjtu.edu.cn