# 薄栅氧化层中陷阱电荷密度的测量方法\*

# 刘红侠 郑雪峰 郝 跃

(西安电子科技大学微电子研究所,西安 710071) (2001年6月19日收到2001年7月26日收到修改稿)

提出了一种测量陷阱电荷密度的实验方法,该方法根据电荷陷落的动态平衡方程,利用恒流应力前后 MOS 电容高频 CV 曲线结合恒流应力下栅电压的变化曲线求解陷阱电荷密度及位置等物理量,给出了陷阱电荷密度的解析表达式和相关参数的提取方法和结果,实验表明这种方法方便而且具有较高的精度。

关键词:薄栅氧化膜,经时击穿,恒流应力,陷阱电荷密度

PACC: 7360H, 0710, 7220J

# 1 引 言

随着集成电路的迅速发展,集成电路的性能在不断的提高.超大规模集成电路技术的发展要求栅介质层的厚度显著减薄  $0.35~\mu m$  工艺的栅介质层厚度为 6-10~n m  $,0.25~\mu m$  工艺的栅介质层厚度为 4-5~n m ,发展到  $0.13~\mu m$  工艺时,栅介质层的厚度将仅为 2-3~n m .介质层的厚度将直接影响到器件的电性能和可靠性.因此,栅氧化膜可靠性的研究越来越重要 1-61 .评估仅有几个原子层的薄介质层的质量 ,可以用原子力显微镜 (AFM ) ,担描电子显微镜 (SEM ) ,透射电子显微镜 (TEM ) ,直接观察表面形貌,也可以测量与时间相关的介质击穿 TDDB (Time Dependent Dielectric Breakdown )的击穿时间  $t_{\rm bd}$  ,击穿电场强度  $E_{\rm bd}$ 和击穿电量  $Q_{\rm bd}$ 等参数 ,直接评估工艺和基体材料对小于 20~n m 的薄栅介质层质量的影响。

薄栅氧化层的经时击穿可归因于在电应力作用下,介质膜内陷阱电荷密度的增加,陷阱电荷密度增加的速率直接影响薄栅氧化层寿命的长短.因此,研究陷阱电荷密度变化的规律,是研究薄栅氧化层经时击穿的一个重要方面 $^{[78]}$ .实验通常利用正负栅压下 MOS 结构的  $_{LV}$  特性曲线测量陷阱电荷的位置及陷阱电荷密度 $^{[9]}$ .考虑到栅介质膜在相反极性栅压下的退陷阱现象,这种测量方法会引入较大的误差.本实验采用高频  $_{C-V}$  曲线结合恒流应力下栅电

压的变化可以精确测量陷阱电荷密度及位置,同时 从应力前后栅电压改变量的正负还可判断陷阱电荷 的极性.这对介质击穿究竟是由电子俘获还是空穴 俘获引起的问题上提供了有力判据.

#### 2 实验原理

薄栅氧化层中的电荷陷落机理可能是电子陷阱俘获电子,也可能是空穴陷阱俘获空穴。以电子陷阱为例,电子陷阱与  $SiO_2$  导带,价带交换电子的过程有两个.

1)被电子占据的电子陷阱向 SiO<sub>2</sub> 导带发射电子

设每个被电子占据的电子陷阱单位时间内向  $SiO_2$  导带发射电子的概率为  $e_n$  ,并设单位时间内被电子占据的电子陷阱密度  $n_i$  ,则由此过程引起的  $n_i$  减少为

$$\frac{\mathrm{d}n_t}{\mathrm{d}t} = e_n n_t. \tag{1}$$

这里假设  $SiO_2$  导带中的能态全为空态 i不影响电子陷阱向导带发射电子.

2)未被电子占据的电子陷阱从  $SiO_2$  导带俘获电子.

设未被电子占据的电子陷阱单位时间从导带俘获电子的概率为  $c_n$  ,电子陷阱的总密度为  $N_T$  ,被电子占据的电子陷阱密度为  $n_t$  , $SiO_2$  导带中电子密度为  $n_t$  则此过程引起的  $n_t$  的增加为

式中

$$\frac{\mathrm{d}n_t}{\mathrm{d}t} = c_n n(N_T - n_t), \qquad (2)$$

结合(1)(2)式  $n_i$  的变化率为

$$\frac{\mathrm{d}n_t}{\mathrm{d}t} = c_n n(N_T - n_t) - e_n n_t. \tag{3}$$

设初始条件为 t=0 时,被电子占据的陷阱密度为 n(0) 则由方程(3)解得

$$n_{t} = A + (n_{t}(0) - A)e^{-Bt}$$

, (4)

$A = \frac{nN_{T}}{n + \frac{e_{n}}{a}}$ ,  $B = e_{n} + c_{n}n$ .

若在加应力期间,氧化层导带内自由电子密度较高,电子陷阱俘获电子的过程占主导地位,因而可以忽略电子陷阱向  $SiO_2$  导带发射电子的过程,则 t 时刻被电子陷阱俘获的电子数为

$n_t = \frac{rit}{q} + N_T + (n_t(0) - N_T)e^{-Bt}$ . (6) (6)式中陷阱电荷密度  $n_t$  可以利用恒流应力前后 MOS 器件高频 C-V 曲线结合恒流应力下栅电压的 变化曲线求解.参数 r ,B , $n_t(0)$  , $N_T$  等可用计算机 统计拟合方法求出.

增加的电子陷阱即被电子占据(5)式可修正为

向 MOS 电容注入恒定电流,由于电荷陷落及注入  $SiO_2$  的载流子在  $SiO_2$  中产生新的陷阱,使得二氧化硅层中陷阱电荷密度增加,陷阱电荷密度的增加使得阴极附近的电场强度发生变化,电场的变化可以改变注入电流的大小.为保持恒定电流注入,必须改变加在 MOS 电容两极之间电压-栅电压  $V_{\rm g}$ . 近似认为  $SiO_2$  中的陷阱电荷成片状分布,片电荷与硅衬底的距离为 x,则根据电中性原理求得陷阱电荷

密度

$$n_{t}(t) = \frac{\Delta V_{g}(t) \cdot \epsilon}{xq}, \qquad (7)$$

式中  $\triangle V_g$ (t)表示恒定电流应力中栅电压的变化量  $\varepsilon$  为栅介质的介电常数 Q 为电子电量 在恒流应力实验前后分别测出 MOS 电容的高频 C-V 曲线 ,求出  $\Delta V_{\rm B}$  ,

$$\Delta V_{\rm FB} = \frac{q n_{\rm f} (d-x)}{\varepsilon}.$$

(8)

联立方程(7)和(8),可求出x及 $n_i(t)$ ,

$$n_t = \frac{\varepsilon (\Delta V_{\rm FB} + \Delta V_{\rm g})}{qd}, \qquad (9)$$

$$x = \frac{\Delta V_{\rm g} \cdot d}{\Delta V_{\rm FB} + \Delta V_{\rm g}}.$$

(10)

### 3 实验结果和讨论

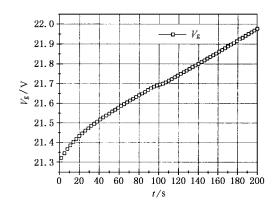

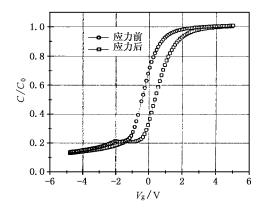

实验采用的器件是无锡华晶公司提供的封装好 的 NMOS 电容样品 氧化层厚度是 20.5 nm .栅电极 为铝 ,面积大小是 1.778×10<sup>-3</sup> cm<sup>2</sup> ,本实验采用的仪 器是 HP 公司的高精度半导体参数分析仪 HP4156B 和 Keithley 仪器公司的 C-V 测试仪. HP4156B 的作 用是对样品加栅压以保持恒流  $I_g$  注入 ,并对栅电压  $V_{\rm g}$  予以实时测量 ,以得到栅压的变化量  $\Delta V_{\rm g}$  . C-V测试仪的作用是测量应力前后高频  $C ext{-}V$  曲线的变 化 以便求得平带电压的漂移量  $\Delta V_{\text{\tiny IR}}$  在本实验中, 对样品所加的恒流是 100 4A,对应的电流密度是 0.056A/cm<sup>2</sup>. 栅电压为正 ,电流从栅极向栅氧化层注 入 总注入时间是 200 s. 恒流注入过程前后的栅电 压变化及高频 C-V 曲线的变化如图 1 和图 2. 从图 1 中可以看出,在整个200 s 的恒流应力注入过程中, 栅电压的变化量  $\Delta V_g = 0.6562 \text{ V}$  ,由图 2 中可以测 出注入前后高频 C-V 曲线的平带电压变化量为  $\Delta V_{\rm B} = 0.798 \text{V}$  .根据(9)式和(10)式,求得整个注入 过程中陷阱电荷密度的增量  $n_r = 1.53 \times 10^{12} / \text{cm}^2$ .这 和文献 10 的报道是一致的. 陷阱电荷中心离阴极 的距离是 x = 9.2 nm. 恒流注入过程中. 栅电压不断 增加 说明电子不断的陷入氧化层 ,这和高频 C-V曲线的测量结果相符合.图 2 中,电流注入后的 C-V曲线向 + V₂ 方向漂移 同样证明恒定电流注入在栅 氧化层中产生负陷阱电荷 ,在恒定电流注入过程中 , 负陷阱电荷密度随应力时间的增加而增加.

在测量完陷阱电荷密度后,从(6)式可以进行相

图 1 恒流应力中栅电压随时间的改变

图 2 恒流应力前后 MOS 电容的高频 C-V 曲线

关参数提取.(6)式中包含的参数有四个.式中  $N_T$  为介质膜内原有陷阱总密度, $n_L$ (0)为电应力开始时被电子占据的陷阱密度,B 为陷阱俘获电子的能力,T 是每注入一个电子产生电子陷阱的概率,这四个参数都具有很明显的物理意义.因此,对于陷阱密度表达式中参数的提取非常重要.

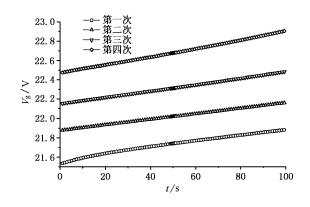

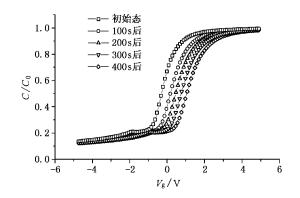

在相关的参数测量中,对样品连续施加恒流应力,在不同的时刻测量恒流应力中栅电压随时间的改变和不同时刻应力前后的的高频 C-V 曲线.实验方法同上.具体的参数条件是:注入电流  $100~\mu$ A,相应的电流密度  $0.056~A/cm^2$ .对于同一样品,分别在 100~200~300 和 400~s 后测试恒流应力中栅电压随时间的改变和恒流应力前后 MOS 电容的高频 C-V 曲线 结果如图 3 和图 4 所示.

从图 3 和图 4 中 ,可以求出在开始 100 s 中 ,平 带电压的变化量  $\Delta V_{\text{FB}} = 0.5 \text{ V}$  , 栅电压的变化量  $\Delta V_{\text{g}} = 0.3392 \text{ V}$  .从中可以求出  $n_{\iota} = 0.80 \times 10^{12}/\text{cm}^2$  .用同样的方法 ,可以求出第 200 ,300 和 400 s 结束时 ,平带电压的变化量  $\Delta V_{\text{FB}}$  .栅电压的变化量  $\Delta V_{\text{CB}}$

图 3 不同恒流应力时刻中栅电压随时间的改变

图 4 不同恒流应力时刻 MOS 电容的高频 C-V 曲线

和陷阱密度  $n_i$  如表 1 所示.

表 1 样品在不同应力时间后的  $\Delta V_{ ext{FB}}$   $\Delta V_{ ext{g}}$  和  $n_{t}$  值

| 测量时间/s | $\Delta V_{\mathrm{FB}}/\mathrm{V}$ | $\Delta V_{ m g}/{ m V}$ | $n_t / (\times 10^{12} / \text{cm}^2)$ |

|--------|-------------------------------------|--------------------------|----------------------------------------|

| 100    | 0.5                                 | 0.3392                   | 0.80                                   |

| 200    | 0.8                                 | 0.6184                   | 1.49                                   |

| 300    | 1.1                                 | 0.9404                   | 2.14                                   |

| 400    | 1.4                                 | 1.3628                   | 2.90                                   |

把不同时刻的陷阱电荷密度带入(6)式可求出r,B, $N_T$ 和 $n_i$ (0)的值.由于不同样品之间存在个体差异,对于上述 MOS 电容样品进行了大量的实验,对其进行统计分布.在提取相关参数时,计算量很大,编了一个计算机统计软件进行拟合求解.求解的结果为: $r=1.36\times10^{-8}$ , $B=5.97\times10^{-4}$ , $N_T=3.05\times10^{11}/\mathrm{cm}^2$ , $n_i$ (0)= $1.09\times10^{11}/\mathrm{cm}^2$ .

实验发现对同一样品施加不同的恒流应力,一个电子产生电子陷阱的产生概率  $_r$  非常相近 ,这个结论是合理的 .但是陷阱俘获电子的概率  $_B$  随注入电流密度的增大而减小 ,说明注入电流密度越大  $_R$

应的栅电压越高 栅氧化层的电场越高 注入电子被加速而获得的能量越大 陷阱越不容易俘获电子.

### 4 结 论

薄栅氧化层的可靠性是 MOS 集成电路中最重要的问题之一,研究薄栅氧化层中陷阱电荷密度变

化的规律,是研究薄栅氧化层击穿的一个重要方面.本文根据动态平衡方程,采用高频 C-V 曲线结合恒流应力下栅电压的变化可以精确求解陷阱电荷密度及位置,同时从应力前后栅电压改变量的正负还可判断陷阱电荷的极性.通过计算机统计拟合软件,可以方便地提取电荷俘获过程中的各个参数.实验表明这种方法简单,易行,具有较高的精度.

- [1] Thonmas R W 1998 Microelec . Reliab . 38 861

- [2] Stathis J H, Dimaria D J 1998 IEDM Tech. Dig. 167

- [3] Schuegraf K F, Hu C 1994 IEEE Trans. Electron Devices 41 761

- [4] Dumin D J , Maddux J R , Scott R S , Subramoniam R 1994 IEEE Trans . Electron Devices 41 1570

- [5] Yang T C and Saraswat K C 2000 IEEE Trans. Electron Devices 47 746

- [6] Liu H X , Fang J P , Hao Y 2000 Acta Phys . Sin . **49** 1172(in Chinese ] 刘红侠、方建平、郝跃 2001 物理学报 **50** 1172]

- [7] Placencia I, Sune J 1988 J. Phys. 49 783

- [8] Degraeve R, Ogier JL, Bellens R 1996 IRPS 44

- [9] Kate I , Horie H , Oikawa K , Taguchi M 1991 IEEE Trans . Electron Devices 38 1334

- [ 10 ] Fazan P , Dutoit M , Martin C and Ilegems M 1987 Solid-State Electronics 30 829

#### A method for measuring the density of trapping charges in thin gate oxides \*

Liu Hong-Xia Zheng Xue-Feng Hao Yue (Microelectronic Institute, Xidian University, Xi'an 710071, China)

( Received 19 June 2001; revised manuscript received 26 July 2001)

#### ABSTRACT

This paper presents an experimental method for measuring the density of trapping charges. This method is based on the dynamic equilibrium equation for the process of trapped charges. We can obtain the density and the location of trapping charges by measuring the high frequency *C-V* curve of MOS capacitance before and after stress and the change of gate voltage under constant current stress. The analytical expression of the density of trapping charges is proposed. The method and the results of parameters extraction are also presented. Experimental results show that this method is convenient and precise.

**Keywords**: thin gate oxides , time dependent dielectric breakdowr( TDDB) , constant current stress , density of trapping charges **PACC**: 7360H , 0710 , 7220J

<sup>\*</sup> Project supported by the National High Technology Development Program of China (Grant No. 863-SOC-Y-3-6-1).