# 一种新的 GaAs PHEMT 器件可靠性评估方法研究\*

刘红侠1) 郑雪峰1) 韩晓亮1) 郝 跃1) 张 绵2)

<sup>1</sup>(西安电子科技大学微电子研究所 .西安 710071) <sup>2</sup>(信息产业部十三所 .石家庄 050002) (2003年1月23日收到 2003年3月5日收到修改稿)

通过研究应力前后 GaAs PHEMT 器件电特性的测量 ,分析了 GaAs PHEMT 退化的原因 ,从实验中得出高场下碰撞电离的电离率与器件沟道电场峰值的关系曲线.对高场下碰撞电离率的实验曲线进行拟合 ,可以得到碰撞电离率与器件沟道电场峰值的量化关系 ,由此可以对 GaAs PHEMT 器件的电性能和可靠性进行改善和评估.进一步改进 GaAs PHEMT 的击穿电压 将需要严格控制沟道中的碰撞电离.

关键词:高电子迁移率晶体管,碰撞电离率,可靠性评估

PACC: 7360L, 7220J, 7300, 6855

#### 1. 引 言

以化合物半导体 GaAs JnP ,GaN 等为材料的量 子阱器件由于其特有的高频、高功率的优异性能及 其耐恶劣环境的能力在军用卫星、航空、导弹、通信、 微波、毫米波和雷达等诸多领域内获得了广泛的应 用,而其中高电子迁移率场效应管 HEMT( high electron mobility transistor)是被公认为微波、毫米波和电 路领域内极具竞争力的三端器件[1-5] 随着器件尺 寸由微米进入亚微米甚至深亚微米,器件内部电场 强度大大增加 器件受到的电应力不断增强 器件性 能受电路参数和工艺参数影响的灵敏度不断提高, 尤其是电路在各种应力的作用下产生的性能退化将 越来越严重,这些应力产生的各种效应,如热载流子 效应、源漏击穿和栅电流退变等等也比长沟道器件 中的严重.这些退变将大大影响电路的使用寿命和 可靠性 HEMT 器件可靠性成为制约整个系统可靠 性的重要因素.进行 HEMT 器件性能退化研究,并不 断加强器件的可靠性优化设计,使器件可靠性在设 计过程中就尽可能达到最优,平均无故障时间最长, 避免突发性失效的出现.

HEMT 的结构与工作原理同 MESFET( metal-semiconductor field-effect transistor)是相似的. HEMT 优于 MESFET 的关键所在是导电沟道不掺杂,导电

沟道中的电子由高掺杂层(如 AlGaAs)提供,因而避免了杂质对载流子的散射,具有很高的电子迁移率。这个特点使它不仅具有优异的噪声特点,而且具有出色的功率性能<sup>6—10 ]</sup>. 其中赝配 HEMT 即 PHEMT (pseudomorphic HEMT)表现尤为特殊,PHEMT 能够显著改善 HEMT 的跨导和电流密度.

以往对 GaAs PHEMT 的研究,很多都是集中在器件的高温环境下工作和寿命预测方面.直到最近,才着重研究室温、高漏偏压应力下热电子引起的相关问题.热电子引起的主要是栅电流退化.阈值电压漂移和跨导等电特性变化以及器件击穿等可靠性问题.本文通过研究应力前后 HEMT 器件电特性的退化.得出高场下碰撞电离的电离率与器件沟道电场峰值的关系曲线,对高场下电离率的曲线进行拟合,可以得到电离率与器件沟道电场峰值的量化关系,由此可以对 GaAs PHEMT 器件的可靠性进行评估.

### 2. 材料生长和器件制作

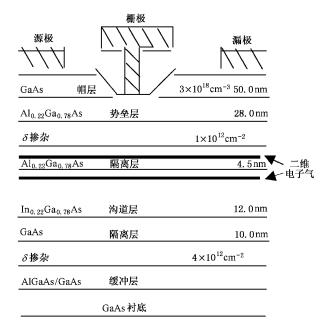

本文所研究的器件是由电子工业部十三所提供的双  $\delta$  掺杂 GaAs PHEMT 器件. 栅长  $L_g=0.40\mu m$  , 栅宽  $W_g=260\mu m$  ,源漏间距为  $3.0\mu m$ . 从底到顶的层结构分别是 ,GaAs 衬底 ,AlGaAs/GaAs 超晶格缓冲层 Si  $\delta$  掺杂(  $4\times 10^{12}$  cm $^{-2}$  )层 ,GaAs 隔离层 , $In_{0.22}$   $Ga_{0.78}$  As 沟道层 , $Al_{0.22}$   $Ga_{0.78}$  As 沟道层 , $Al_{0.22}$   $Ga_{0.78}$  As 隔离层 ,Si  $\delta$  掺杂(  $1\times$

<sup>\*</sup> 国家自然科学基金( 批准号:60206006)和国防预研基金( 批准号:00J8.4.3DZ01)资助的课题.

$10^{12} {

m cm}^{-2}$  )层 , ${

m Al}_{0.22} {

m Ga}_{0.78} {

m As}$  势垒层 , ${

m GaAs}$  帽层 . 采用的是凹槽  ${

m T}$  形栅结构 ,如图  ${

m 1}$  所示 .

图 1 双 δ 掺杂 T 形栅 PHEMT 结构图

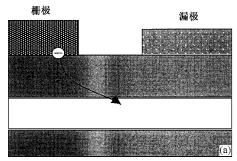

图 2 HEMT 器件中(a)热离子场发射和(b)沟道电子碰撞电离的示意图

栅漏区域的击穿是限制 GaAs HEMT 器件功率的关键因素 .本节对这种击穿现象做了研究 ,采用了通过热电子应力来表征其由于碰撞产生的电子-空穴对的方法 .这种方法是基于在高漏偏置电压下对栅电流的测量 .通过假设大部分产生的空穴能够被栅收集 ,来表征碰撞电离率与沟道内最大电场的关系

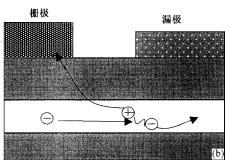

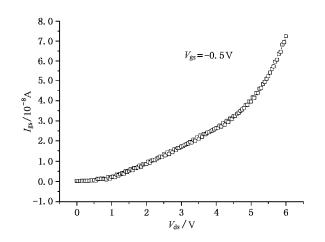

由于偏置在高漏电压下碰撞电离产生的空穴流向栅极,栅极的电流会出现一个突然的增加.这个栅电流会影响最大漏偏置电压.对于已经观察到的器件,由于碰撞电离产生的栅电流的突变会显著降低栅漏击穿电压,从而影响器件的功率.在不同的栅电压下分别测量器件的  $I_{\rm ds}$ - $V_{\rm ds}$ ,  $I_{\rm gs}$ - $V_{\rm ds}$ , 其关系如图 3 所示.

实验采用 HP4156B 高精度半导体参数测试仪. 在测量的时候专门制作了测试盒. 因为对于 HEMT 器件,其增益很高,测试的过程中很容易就出现自激振荡, I-V 特性很容易出现负阻效应,有鉴于此,在测试的时候在栅极和漏极分别串连上电感,在漏源之间串接上电容,以避免负阻效应,使测试的效果更好.事实证明,这种测试盒在测试的过程中是很有效的. 在实验的过程中,一定要保证测试仪器和器件的良好接地.

#### 3. HEMT 的可靠性表征

几年来,对 HEMT 击穿机理的认识有了很大的进步.在设计和制作良好的器件中基本上有两个物理机制决定着 HEMT 之后的击穿机理:1)栅电子的隧穿或者热离子场发射 TFE( thermionic-field emission) 2)沟道电子的碰撞电离. HEMT 器件的两种击穿机制描述在图 2 中.

图 3 器件在不同栅电压下的输出特性和栅电流特性

从图中 3 可以看出 ,当器件在  $V_{ds} > 2.5V$  时 ,栅电流有一个显著的增加 . 当测试器件偏置在高  $V_{ds}$

时,由于栅漏区域的高电场,会出现显著的热电子现象.也就是说在高电场的作用下电子被加速能够达到足够高的能量碰撞进而产生电子-空穴对.假设碰撞电离产生的大部分空穴在栅极被收集,通过测量 $I_s$ ,能够估计碰撞电离率.如果把源端悬置,进行如图 3 一样的测试,在整个  $V_d$ 。范围内可以发现栅电流的增加始终是缓慢的,并不会出现一个突然的增加,进一步说明  $I_s$ 的显著增加不是由栅漏反向电流引起的,而是由碰撞电离产生的空穴引起的.

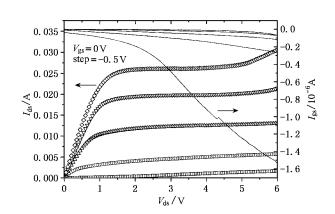

图 4 显示了在  $V_{ss} = -0.5$ V 时  $I_{ss}$ 随  $V_{ds}$ 变化的函数 .从图 4 中可以看出 ,在低的漏电压下 ,即栅漏低电场下 ,栅漏反向电流占主导地位 . 当器件工作在高的漏电压下 ,栅漏之间会出现高场区 ,高能电子碰撞会产生电子-空穴对 ,产生的空穴被栅极收集 ,当它取代栅漏反向电流占主导地位时  $I_{ss}$ 就会有突然的增加 .

图 4  $V_{\rm g} = -0.5 \text{V}$  时的  $I_{\rm g}$ - $V_{\rm ds}$ 曲线

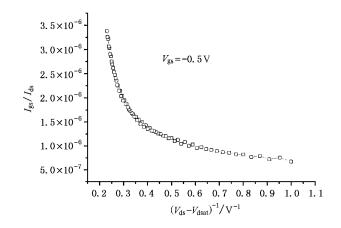

图 5 显示了在  $V_{\rm gs}$  =  $-0.5{\rm V}$  时  $I_{\rm gs}/I_{\rm ds}$  随 I( $V_{\rm ds}$   $-V_{\rm dsat}$ )变化的函数 . 当  $V_{\rm ds}$  很高时 ,所有的数据成为一条直线 . 证实了在高的  $V_{\rm ds}$  下 ,即高电场下 , $I_{\rm gs}/I_{\rm ds}$  与 I( $V_{\rm ds}$   $-V_{\rm dsat}$ )成线性关系 .

为了得到碰撞离化系数 ,需要电场的值. 采用 Hu 提出的简单模型<sup>111</sup> ,即采用

$$E_{\text{max}} = \frac{V_{\text{ds}} - V_{\text{dsat}}}{L_c} , \qquad (1)$$

其中, $V_{\rm dsat}$ 是栅漏饱和电压, $E_{\rm max}$ 是器件沟道区的最大电场, $L_{\rm c}$ 是高场区的特征长度.  $L_{\rm c}$ 依赖于器件偏置电压和器件的沟道长度.

$$\frac{I_{\rm gs}}{I_{\rm de}} = \alpha_{\rm n} (E_{\rm max}) \times L_{\rm c}. \tag{2}$$

图 5  $V_{\rm gs} = -0.5$ V 时的  $I_{\rm gs}/I_{\rm ds}$  - 1/(  $V_{\rm ds} - V_{\rm dsat}$  )曲线

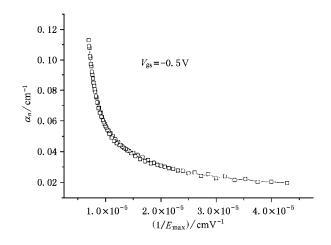

从(2)式可以得到电离率  $\alpha_n$ ( $E_{max}$ ),从而做出  $\alpha_n$ ( $E_{max}$ )与  $1/E_{max}$ 之间的关系图 如图 6 所示.

图 6  $V_{gs} = -0.5 \text{V}$  时的  $\alpha_n$  ( $E_{max}$ )  $1/E_{max}$  曲线

碰撞电离是与沟道最大电场密切相关,对图 6 高场下电离率的曲线进行拟合,可以得到电离率与沟道最大电场之间的关系:

$$\alpha_{\rm n} = 5.6 \times 10^{-2} \times \exp(-3 \times 10^5/E_{\rm max})$$

. (3)

### 4. 结 论

通过对 GaAs PHEMT 器件在高场下的栅电流等参数进行测量,得到器件在高场下的碰撞电离率与电场的函数关系.通过对碰撞电离率的估测,可以对器件的电性能和可靠性进行改善和评估.进一步改进 GaAs PHEMT 的击穿电压,将需要严格控制沟道中的碰撞电离.例如,改变结构,使栅漏距离大于栅源的距离,减小栅漏电场,进而减小电离率,提高器件的击穿特性.

- [1] Gaddi R, Menozzi R, Dieci D, Lanzieri C, Meneghesso G, Canali C and Zanoni E 1999 IEEE 37th Annual International Reliability Physics Symposium 110

- [2] Bollaert S, Cordier Y, Happy H, Zaknoune M, Hoel V, Lepilliet S and Cappy A 1998 IEDM 235

- [3] Fernandez T, Garcia JA, Tazon A, Mediavilla A, Pedro JC and Garcia JL, 1999 IEEE Electron Device Letters 20 557

- [4] Xu D , Suemitsu T , Osaka J , Umeda Y , Yamane Y , Ishii Y , Ishii T and Tamamura T 1999 IEEE Electron Device Letters 20 206

- [5] Zhong Y G , Shen B , Liu J et al 2001 Acta Phys . Sin . **50** 1774[周玉刚、沈 波、刘 杰等 2001 物理学报 **50** 1774]

- [ 6 ] Whelan C S , Hoke W E , Mctaggart R A , Lardizabal S M , Lyman P

- S , Marsh P F and Kazior T E 2000 IEEE Electron Device Letters 21 5

- [7] Binari ST, Ikossi K and Roussos J A et al 2002 IEEE Trans. Electron Devices 48 465

- [8] Bradley S T , Young A P and Brillson L J et al 2001 IEEE Trans . Electron Devices 48 412

- [9] Smorchkova I P , Elsass C R and Ibbetson J P et al . 1999 J. Appl . Phys. 86 4520

- [10] Liu H X , Hao Y , Zhang T , Zheng X F and Ma X H 2003 Acta

Phys. Sin. 52 1774[刘红侠、郝 跃、张 涛、郑雪峰、马晓华

2003 物理学报 52 1774]

- [ 11 ] Hu C 1985 IEEE Trans . Electron Devices 32 375

## A new method to evaluate reliability in GaAs PHEMT 's \*

Liu Hong-Xia<sup>1</sup>) Zheng Xue-Feng<sup>1</sup>) Han Xiao-Liang<sup>1</sup>) Hao Yue<sup>1</sup>) Zhang Mian<sup>2</sup>)

<sup>1</sup> ( Microelectronics Institute , Xidian University , Xi 'an 710071 ,China )

<sup>2</sup> ( Thirteenth Institute , Ministry of Information Industry , Shijiazhuang 050002 ,China )

( Received 23 January 2003 ; revised manuscript received 5 March 2003 )

#### Abstract

This paper analyzes the degradation in GaAs pseudomorphic high electron mobility transistors (PHEMT's) by measuring the electric characteristics in GaAs PHEMT's before and after stress. The relation between impact ionization rate and maximum channel electric field is gained. An analytical expression of impact ionization rate versus maximum channel electric field is deduced by fitting the experimental results. The electric characteristic and reliability in GaAs PHEMT's can be improved and evaluated using the analytical expression. The impact ionization in channel should be decreased in order to improve the breakdown voltage in GaAs PHEMT's.

Keywords: high electron mobility transistor, impact ionization rate, evaluation of reliability

PACC: 7360L, 7220J, 7300, 6855

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (Grant No. 60206006) and the National Defence Pre-research Foundation of China (Grant No. 00J8.4.3DZ01).