# 射频能量 AC/DC 电荷泵的 MOS 实现研究

# 姚 远 石 寅

(中国科学院半导体研究所人工神经网络实验室,北京 100083) (2004年9月10日收到2004年10月20日收到修改稿)

在射频能量 AC/DC 的能源转换实现研究中提出一种采用低阈值 MOS 管构成的高效电荷泵. 新方案消除了现有的肖特基二极管高效电荷泵制作工艺特殊、批次性能不够一致的缺陷. 分析表明,通过有机调整 MOS 管宽长比、器件电容、充电级数等设计参量,可以方便地满足不同的性能要求,实现集成制作方便、性能稳定的高效射频能量AC/DC 型电荷泵.

关键词:电荷泵,低功耗,高效率

PACC: 8630, 7280C, 7230

### 1. 引 言

电荷泵也称作电压倍增器 ,较小的交流或直流电压通过电荷泵可以转变为不同电平的直流电压.根据输入情况的不同 ,电荷泵分为 AC/DC 型和 DC/DC型.在 EEPROM ,Flash Memory 以及无源射频芯片等电路中 ,有着广泛应用.

传统的 AC/DC 电荷泵采用半导体二极管及储能部件构成 ,为了提高输出电压和转换效率 ,采用开启电压低且导通电阻小的肖特基二极管 <sup>1]</sup> .但由于肖特基管需要特殊的制作工艺 ,工艺制备上的不通用性以及批次间性能的不够一致性 ,在很大程度上限制了电荷泵低成本制作来被广泛使用 . 本文提出采用常规制备、批次性能稳定的低阈值 MOS 管来替代肖特基管构成射频能量 AC/DC 电荷泵 .

本项研究从器件工作原理出发,提出并分析了低阈值 MOS 晶体管方案电荷泵. 论文依据电路理论 以单位充电单元作为基本部件讨论 MOS 型电荷泵的基本原理,推导输出电压的解析表达式;从优化性能的角度,研究输出特性,电压建立时间以及转换效率等主要特性指标与诸如 MOS 管衬底连接方式、尺寸,电容大小以及拓扑级数等设计控制参数之间的关系,依据器件物理,推导针对不同要求指标的数学控制表达式.实例验证表明,这些分析结果为高效MOS 型电荷泵的集成实现提供了合理的理论基础

# 2. MOS 型电荷泵结构和工作原理

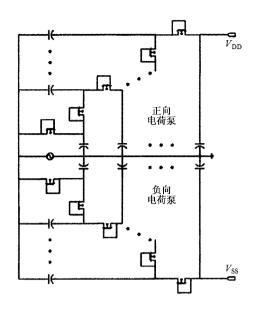

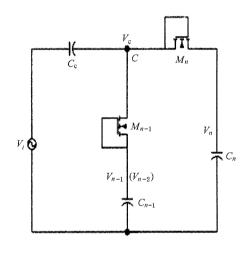

文献 2 3 给出了经典的二极管电荷泵结构,据此本文提出了奇数级拓扑结构的 NMOS 型 AC/DC 电荷泵,分为正向和负向电压倍增两部分,如图 1 所示,以正向倍增为对象,取如图 2 所示的单位倍增单元来分析,在射频情况下可以看到充电电容  $C_{n-1}$ , $C_n$  分别相当于一个直流电压源,而  $C_c$  相当于一个交流耦合电容,将交流输入  $V_i$  与前一级  $C_{n-1}$  上的直流电压  $V_{n-1}$  进行耦合并送入  $C_n$  进行倍增,设  $M_{n-1}$   $M_n$  管上压降分别为  $V_{n-1}$  和  $V_{n}$  稳定时有

$$V_{\rm c}$$

=  $V_{\rm n-1}$  -  $V_{

m dn-1}$  ,  $V_{

m c}$  =  $V_{\rm n}$  +  $V_{

m dn}$  , 若两管宽长比一样 ,在电流相同时近似有  $V_{

m dn-1}$  =

V<sub>dz</sub> ,所以

$$V_c = (V_n + V_{n-1})/2$$

同时  $M_n$ 管的交流输入信号为  $V_c$  +  $V_i$  ,设单级直流电压增量

$$\Delta V = V_{\rm i} - V_{\rm d} ,$$

则

$$(V_n + V_{n-1})/2 + \Delta V = V_n$$

,

所以

$$V_n = V_{n-1} + 2\Delta V.$$

<sup>†</sup>E-mail: yyao@mail.semi.ac.cn

图 1 NMOS 型电荷泵的电路结构

图 2 单位电荷泵倍增单元

$2\Delta N$  其中 n=2k+1 , k 为电路中单位电荷泵倍增单元的序数 ,依次取 1 2 3 ,.... 当电荷泵所有 NMOS 管取相同宽长比时 ,每级  $\Delta V$  相等 ,继续递归推导有

$$V_n = n\Delta V = n(V_i - V_d), \qquad (1)$$

n 为电路中 NMOS 管个数.(1)式即为推导出的 NMOS 型 AC/DC 电荷泵输出电压的数学表达式.对于偶数 拓扑结构型和 PMOS 型电荷泵 (1)式同样成立.

# 3.MOS 型 AC/DC 电荷泵诸性能分析

#### 3.1. 输出电压

#### 3.1.1.MOS 管衬底连接方式

一般的 NMOS 电路中 ,为避免漏电都将源/漏与

衬底的 pn 结反偏 ,即衬底连接到系统最低电位.但是为了满足不同输出电压需求 ,电荷泵中 NMOS 衬底连接方式分为接最低电位的普通方式和接源端的去衬偏方式. 当需要较高电压输出时 ,衬底连接采用去衬偏方式 ,以避免体效应引起的管上压降增大而带来的电压提高限制. 例如 ,EEPROM 中 MOS 型 DC/DC 电荷泵需要产生 14 V 的擦除高电压 ,若衬底连接采用普通方式 ,根据阈值公式

$V_{th} = V_{th0} + \chi (\sqrt{12\Phi_{\rm F} + V_{\rm sb} + -\sqrt{12\Phi_{\rm F} + V_{\rm sb}}})^{41}$ ,当  $V_{\rm sb} = 14$  V 时, $V_{th}$ 将增大 1 V 以上,会明显导致输出电压降低和充电时间增加,降低了电路性能.当需要较低电压输出时,衬底采用普通连接方式,避免了去衬偏连接时反向充电过程中衬底与漏端之间正向pn 结的漏电损耗,从而提高了转换效率.

对于射频能量转换 AC/DC 电荷泵 ,由于输入信号功率很小,所以尽管体效应会使单级电荷泵电压增量  $\Delta V$  不断变小进而降低输出电压,但为了降低功耗而提高转换效率,衬底仍应采用普通连接方式,接到系统最低电位负电压输出端  $V_s$ 上.

### 3.1.2.MOS 管阈值、器件尺寸和充电级数

根据(1)式,增加级数n能最方便地提高输出电压,但NMOS管和电容数目的增加会同时增大电路功耗进而使转换效率降低.这就要求在最少级数以及输入信号 $V_i$ 一定的条件下为了使输出电压最大必须尽量降低NMOS管上压降 $V_d$ .由于栅漏短接NMOS管工作在饱和区有

$$V_{

m d}$$

=  $V_{

m ds}$  =  $\sqrt{2I_{

m ds}/eta}$  +  $V_{

m th}$  ,

其中  $\beta = \mu_n C_{\infty} W/L$ .可知在输出电流恒定的情况下为了减小  $V_d$ 需要选择大的宽长比和较低的阈值.在具体实现中,鉴于宽长比与转换效率以及工艺等因素都还有制约关系,其具体数值还应与充电级数等参量进行折衷考虑.

#### 3.1.3. 反向漏电

在(1)式的推导中,尽管可以粗略地设定  $\Delta V = V_i - V_d$ ,但两者在严格意义上并不完全等价,因为 NMOS 管器件电容的反向漏电影响了充电效果. 对于高频尤其在射频范围应用的电荷泵,在输入电压 半个非充电周期中存在着由器件结电容  $C_p$  导致的源漏反向漏电流,而且随着频率升高这种电容耦合漏电会越发显著,从而使  $\Delta V \neq V_i - V_d$ . 因此(1)式中需要增加一个描述反向漏电的电压损耗项  $V_{leak}$ . 根据器件原理, $C_p$  可以看作是 NMOS 管内多个 pn

结电容的并联 ,主要由  $C_{\rm gs}$  , $C_{\rm gb}$ 以及  $C_{\rm db}$ 组成 ,所以  $C_{\rm p} \propto C_{\rm jo} I 1 + V_{\rm r}/\Phi_{\rm b}$  ]" , $V_{\rm r}$ 是结反向电压 , $\Phi_{\rm b}$  是结内建电势 ,m 的值一般在 0.3 到 0.4 之间  $^{14}$  因为  $V_{\rm r} \sim V_{\rm sb}$  因此当  $V_{\rm sb}$ 增大时  $C_{\rm p}$ 不断减小并导致容抗随之增大 ,最终使  $V_{\rm leak}$ 进一步减小 . 另外 ,尽管增加宽长比会增大结电容  $C_{\rm p}$  而导致更大的  $V_{\rm leak}$  .但同时也会更显著地降低管上压降  $V_{\rm d}$  ,从而实现更高的输出电压 .

至此(1)式变为

$$V_n = n(V_i - V_d - V_{leak}), \qquad (2)$$

这是修正后的 NMOS 型电荷泵输出电压表达式.

所以在 MOS 型 AC/DC 电荷泵中,对于输出电压,当需要高电压输出但对功耗要求不严格时,衬底应该采用接源端的去衬偏连接;而当应用在低功耗而输出电压不高时,衬底应该采用接最低电位的普通连接.在尽可能选择低阈值 MOS 管的基础上,可以通过配置宽长比和充电级数来使输出电压满足预期要求.

#### 3.2. 输出电压建立时间

图 1 提出的新结构 NMOS 型电荷泵 ,采用了正负双向电压倍增结构来加快充电速度 ,以更快地稳定电路输出 . 文献 2 3 ]中传统的单一正向或负向电压倍增结构仅仅利用输入信号的半个周期进行充电 ,而另外半个非充电周期则完全被浪费 ,使得输出建立速度明显慢于利用正负半周同时充电的双向结构 . 此外 ,充电电容以及 MOS 管宽长比都会对输出建立时间产生影响 . 在实际测量中 ,一般取输出达到最终电压 90% 的时刻为建立时间  $T_{\rm rise}$  . 由于  $T_{\rm rise}$  =  $C_{\rm load}V_{\rm o}/I_{\rm aver}$  , $C_{\rm load}$  为最后一级充电电容 , $V_{\rm o}$  为输出电压 , $I_{\rm aver}$  为建立时间过程中流过电容的平均电流正比于宽长比 ;可知 ,对于一定的  $I_{\rm aver}$  当  $C_{\rm load}$  越小 ,W/L 越大时 , $T_{\rm rise}$  越小 ,E 之 ,  $T_{\rm rise}$  越大 .

因此,为了减小输出电压建立时间,应采用正负 双向倍增结构,并减小充电电容和增大 NMOS 管宽 长比.

#### 3.3. 转换效率

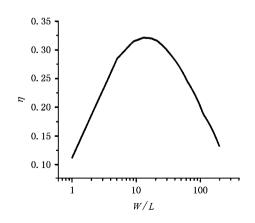

当 AC/DC 电荷泵应用在射频能量转换时,由于 天线接收的信号功率相当有限,转换效率成为非常 重要的技术指标和考虑因素.因此本文利用高频器 件物理模型分析并给出了功耗来源和计算公式,以 实现转化效率最大化. 转换效率的具体定义为  $\eta = P_o/P_i$  ,  $P_i$  ,  $P_o$  分别为电荷泵的输入、输出功率 ;另设  $P_{loss}$  为电路本身损耗 ,上式变为  $\eta = 1 - P_{loss}/P_i$  . 对于 NMOS 电荷泵 ,本文提出  $P_{loss}$  由两部分组成 :1 ) NMOS 管上功率损耗 ,主要由沟道电阻  $R_c$  和与其并联的器件电容  $C_p$  产生 . 在充电过程中 ,根据高频下 NMOS 管器件物理模型推导有

$$P_{\rm nmos\ loss} = \frac{1}{2} V_{\rm i}^2 (R_{\rm c} \omega^2 C_{\rm p}^2 + 1/R_{\rm c}),$$

$V_i$  和  $\omega$  分别是输入信号幅值和角频率.可知 ,当  $R_c$  =  $1/\omega C_p$  时  $P_{\rm nmos\ loss}$  取最小值 ,由于在输出电流相同时  $R_c \propto 1/\sqrt{(W/L)}$  ,  $C_p \propto W/L$  ,所以存在一个特定的 W/L 值使转换效率最大 ,如图 3 所示.同样地 ,由于宽长比与输出电压以及输出建立时间也同时存在制约关系 ,对其具体数值的选取仍然需要进行折衷考虑. 2 )耦合和充电电容的功率损耗. 在集成电路中 ,电容存在着与衬底的寄生电容  $C_{\rm sub}$  和串联电阻  $R_{\rm sub}$  ,与之对应的功耗[1]为

$$P_{\text{cap,loss}} = \frac{1}{2} V_{\text{i}}^2 \frac{R_{\text{sub}}}{R_{\text{sub}}^2 + (\omega C_{\text{sub}})^{-2}} ,$$

而且对于一般低阻型衬底有  $R_{\text{sub}}\omega C_{\text{sub}}\ll 1$  ,上式可以简化为

$$P_{\text{cap ,loss}} = \frac{1}{2} V_{\text{i}}^2 (\omega C_{\text{sub}})^2 R_{\text{sub}}.$$

由于电容面积与其大小有对应关系 ,所以并不能通过改变电容尺寸来方便地调节  $C_{\text{sub}}$  和  $R_{\text{sub}}$  ,这就要求在满足输出要求的情况下为了提高转换效率应尽量减小电容 .同时 ,随着频率上升电路功耗会随之增大 ,从而使转换效率越来越低 .

图 3 MOS 管宽长比 W/L 与转换效率  $\eta$  关系图

通过上述分析可知,在同时考虑输出电压和上

升速度的前提下 通过选取特定的 NMOS 管宽长比、充电电容和充电级数 ,可以实现转换效率的最大化.

# 4. 实例与实验结果

现在根据上述原理,研究了一个完成射频信号能量转换以提供芯片直流电源的 AC/DC 电荷泵实例. 要求在频率 900~MHz 幅度 300~mV 的输入电压条件下,在  $1~M\Omega$  负载上输出正负电压差达到 2~V.

#### 4.1. 参数选择

充电级数选择 根据输入、输出电压以及宽长 比选择范围,选择正负各九级充电结构。

充电、耦合电容选择 为了给后续电路提供稳定的电压 要求最后一级充电电容为  $250~\mathrm{pF}$  其余充电电容一同定为  $10~\mathrm{pF}$  ;耦合电容选择  $20~\mathrm{pF}$  ,在  $900~\mathrm{MHz}$  时容抗为  $8.8~\Omega$  ,满足交流短路要求 .

NMOS 管的选择 生产工艺提供了  $V_{tt0}$  仅为 23 mV 的极低阈值 NMOS 管 通过扫描得到当 NMOS 管 宽长比为  $52.5~\mu\text{m}/1.5~\mu\text{m} = 35/1$  时 ,转换效率最大 ,此时输出为 1.93~V ,考虑输出电压要求 ,选择宽长比为  $60~\mu\text{m}/1.5~\mu\text{m} = 40/1$  .

#### 4.2. 实验结果

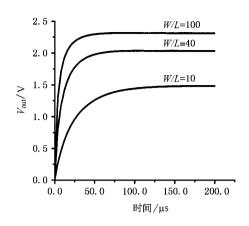

输出电压  $V_o = 2.036$  V,输出建立时间  $T_{rise} = 29.0 \, \mu s$  输入功率  $P_i = 14.24 \, \mu W$  输出功率  $P_o = 4.2 \, \mu W$ ,已经满足了 AC/DC 电荷泵设计要求.其中,转换效率  $\eta = 29.4\%$ ,优于文献 1]中肖特基二极管型电荷泵所报道的结果.如图 4 所示,随着 NMOS 管宽长比增加 输出电压增大,输出建立时间缩短都符合

上述理论分析.

图 4 电荷泵的仿真结果

# 5. 结 论

理论分析和实例验证表明,本文提出的采用正负双向倍增结构的 MOS 型射频能量 AC/DC 电荷泵在缩短输出电压稳定时间和消除特殊制作工艺前提下,通过所需的 MOS 管阈值、宽长比、级数以及结构中储能电容等因素存在彼此的折衷关系的调整,可以满足不同的性能要求.选择适当的级数和 NMOS 管衬底连接方式来满足电路对输出和转换效率的要求,通过对具体宽长比与电容数值的折衷考虑来实现上升时间以及功率损耗的优化配置.

新结构电荷泵采用常规制作工艺,便于与其他部件 SOC 系统集成的特点为它的广泛应用提供了基础.与此同时,DC/DC 电荷泵同样可以利用相同的MOS 管结构来提高电路的通用性.

<sup>[1]</sup> Karthaus U and Fischer M 2003 IEEE JSSC 38 1602

<sup>[2]</sup> Lin P M and Chua L O 1977 IEEE Trans. Circ. Syst. 24 517

<sup>[ 3 ]</sup> Brugler J S 1971 *IEEE JSSC* **7** 132

<sup>[4]</sup> Razavi B 2003 Design of Analog CMOS Integrated Circuits (Xi' an Jiaotong University Press) p26

#### 物 理 报

# A study on the realization of radio frequency energy AC/DC charge pump based on MOS FET

Yao Yuan<sup>†</sup> Shi Yin

( Artificial Neural Networks Laboratory , Institute of Semiconductors , Chinese Academy of Sciences , Beijing 100083 , China ) ( Received 10 September 2004; revised manuscript received 20 October 2004)

#### Abstract

This paper presents a novel efficient charge pump composed of low Vth metal-oxide-semiconductor ( MOS ) field effect transistors (FET) in the course of realizing radio frequency (RF) energy AC/DC conversion. The novel structure eliminates those defects caused by typical Schottky-diode charge pumps, which are dependent on specific processes and inconsistent in quality between different product batches. Our analyses indicate that an easy-fabricated, stable and efficient RF energy AC/DC charge pump can be conveniently implemented through reasonably configuring the MOS transistor aspect ratio, and other design parameters such as capacitance, multiplying stages to meet various demands on performance.

Keywords: charge pump, low power, high efficiency

PACC: 8630, 7280C, 7230

<sup>†</sup>E-mail:yyao@mail.semi.ac.cn